# INDICE DE ANEXOS

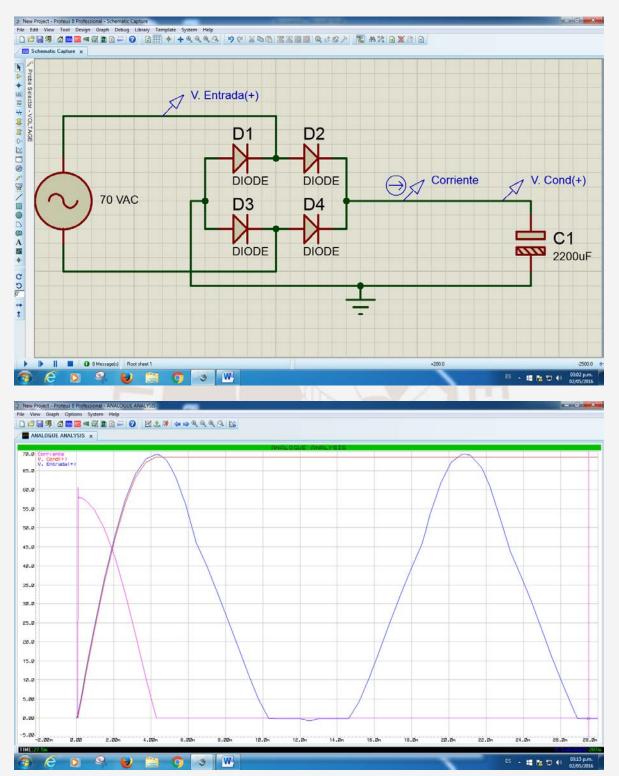

ANEXO 1: SIMULACIÓN EN PROTEUS DE CIRCUITO DE RECTIFICACIÓN SIN RESISTENCIA MINIMIZADORA DE CORRIENTE INICIAL.

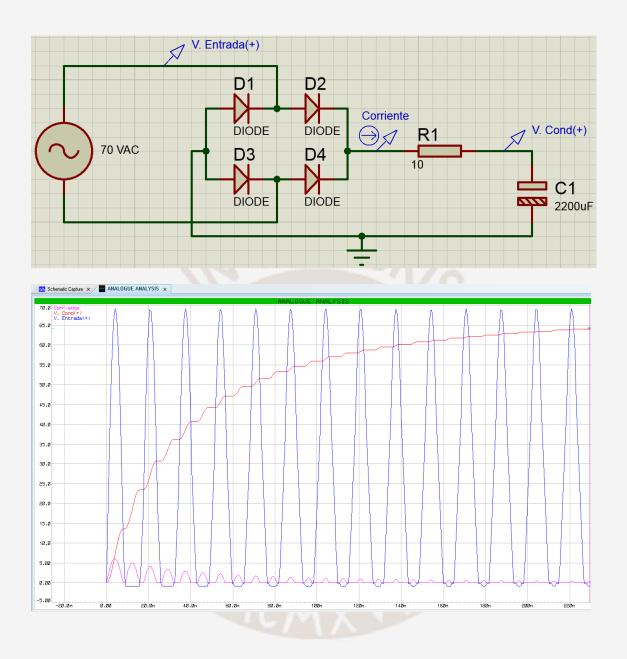

ANEXO 2: SIMULACIÓN EN PROTEUS DE CIRCUITO DE RECTIFICACIÓN CON LA RESISTENCIA MINIMIZADORA DE CORRIENTE INICIAL.

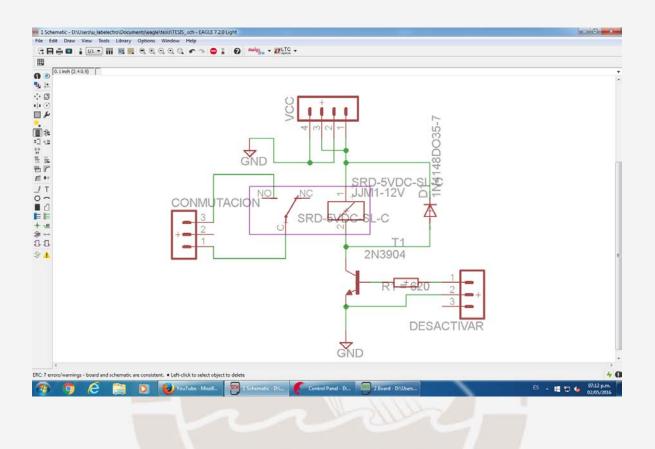

**ANEXO 3**: DIAGRAMA ESQUEMÁTICO DEL CIRCUITO DE PROTECCIÓN CONTRA LA CORRIENTE DE IRRUPCIÓN.

**ANEXO 4**: PAGINA WEB CON MODELO DE DISIPADOR EMPLEADO.

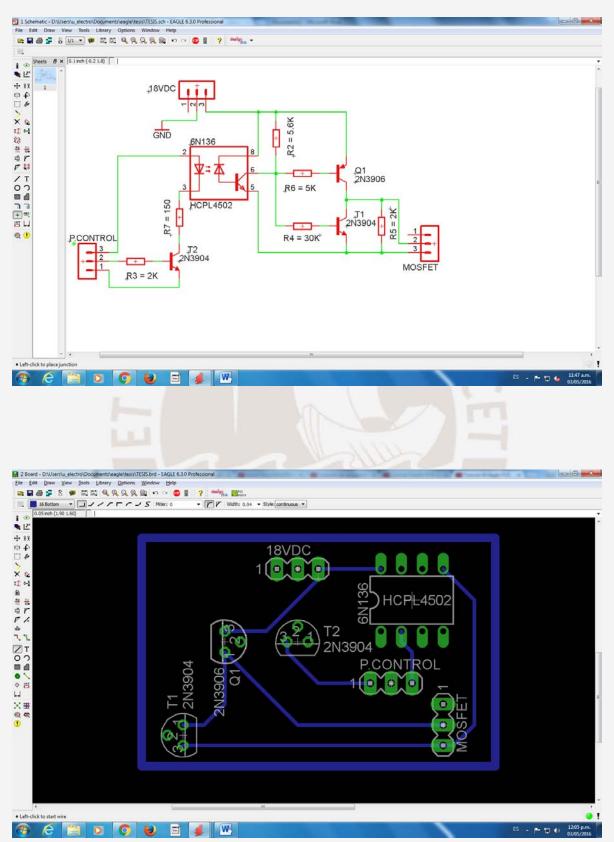

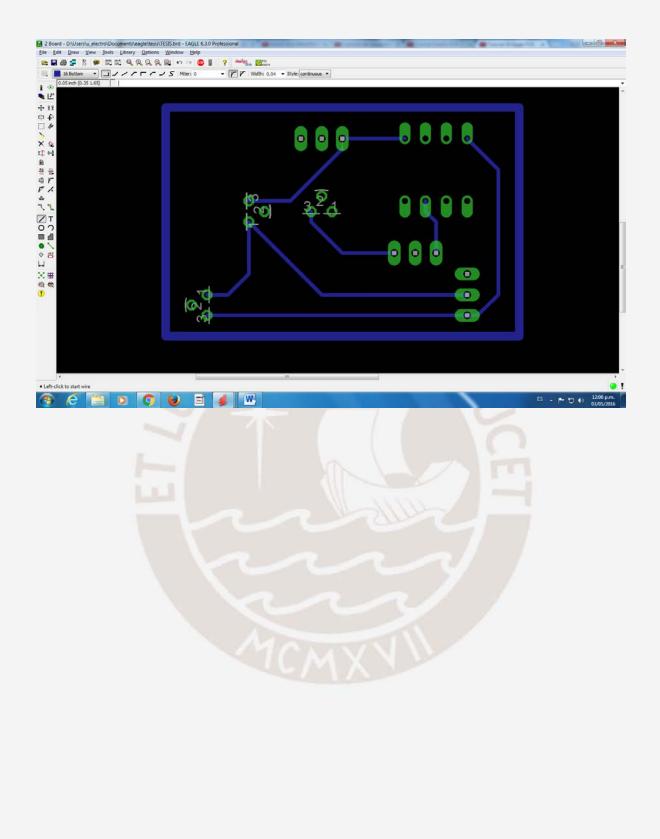

ANEXO 5: ESQUEMÁTICO DEL CIRCUITO DE MANDO DE COMPUERTA CON EL RESPECTIVO BOARD.

**ANEXO 6**: ESQUEMÁTICO DE LA FUENTE PARA EL CIRCUITO DE CAMPO DEL MOTOR CON EL RESPECTIVO BOARD.

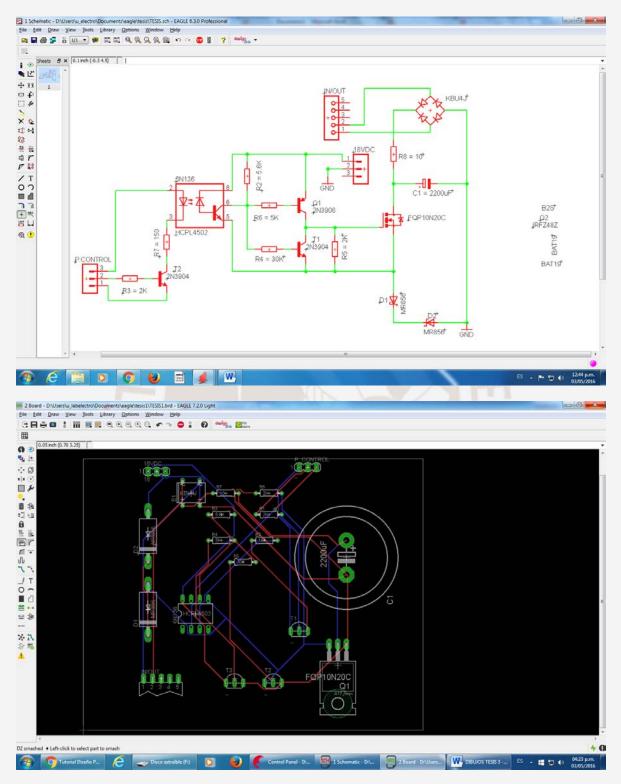

ANEXO 7: ESQUEMÁTICO DEL CIRCUITO DE CONTROL CON EL RESPECTIVO BOARD.

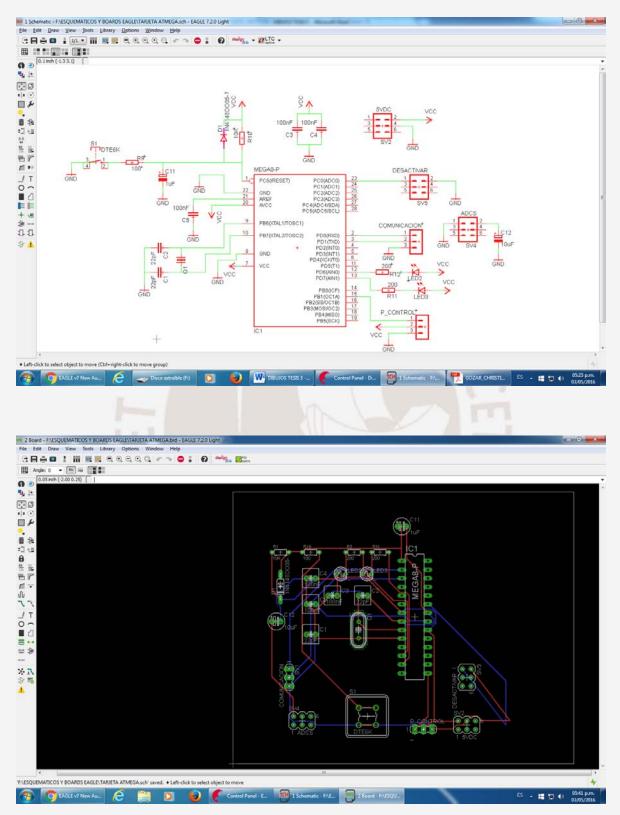

ANEXO 8: HOJA DE DATOS DEL KBU4J.

ANEXO 9: HOJA DE DATOS DEL MOSFET FQP10N20C.

ANEXO 10: HOJA DE DATOS DEL DIODO RÁPIDO MR856.

ANEXO 11: HOJA DE DATOS DEL OPTOACOPLADOR 6N136.

ANEXO 12: HOJA DE DATOS DEL ATMEGA8.

ANEXO 13: CONCEPTOS BÁSICOS DE LA MODULACIÓN POR ANCHO DE PULSOS.

ANEXO 14: PROGRAMA EN C PARA ARRANQUE DE MOTOR SÍNCRONO.

ANEXO 15: ESTUDIO DEL MOTOR SÍNCRONO.

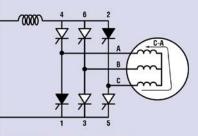

**ANEXO1**: SIMULACIÓN EN PROTEUS DE CIRCUITO DE RECTIFICACIÓN SIN RESISTENCIA MINIMIZADORA DE CORRIENTE INICIAL

**ANEXO 2**: SIMULACIÓN EN PROTEUS DE CIRCUITO DE RECTIFICACIÓN CON LA RESISTENCIA MINIMIZADORA DE CORRIENTE INICIAL

**ANEXO 3**: DIAGRAMA ESQUEMÁTICO DEL CIRCUITO DE PROTECCIÓN CONTRA LA CORRIENTE DE IRRUPCIÓN

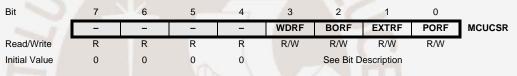

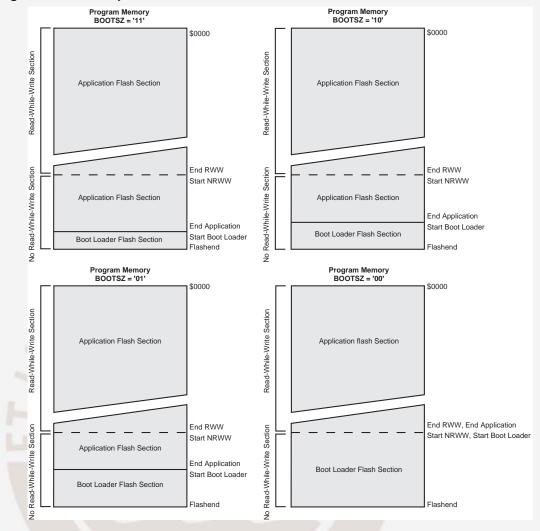

| Α |                                            | <b>ektronik 2</b><br>ransistors in pla                                            |                                                                                                                        |                                                                                                                                                                                |

|---|--------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B | art. no.                                   | T                                                                                 |                                                                                                                        | 25 K/W                                                                                                                                                                         |

| D | FK 211 32<br>art. no.                      | Trin                                                                              |                                                                                                                        | 18 K/W<br>CB (SOT 32 + TO 220)<br>18 K/W                                                                                                                                       |

| E | art. no.                                   |                                                                                   |                                                                                                                        | 21 K/W                                                                                                                                                                         |

| G | art. no.<br>FK 216 SA                      | 140                                                                               |                                                                                                                        | 15 K/W<br>CB (SOT 32 + TO 220)<br>- 30<br>                                                                                                                                     |

| H | art. no.<br>FK 222                         |                                                                                   | + <u>1</u><br><u>1</u><br><u>1</u><br><u>1</u><br><u>1</u><br><u>1</u><br><u>1</u><br><u>1</u><br><u>1</u><br><u>1</u> | 20 K/W                                                                                                                                                                         |

| ĸ | art. no.<br>FK 222 THF                     |                                                                                   | × 5°5                                                                                                                  | 20 K/W<br>& TO 220                                                                                                                                                             |

| L | art. no.<br>FK 247 220<br>please indicate: |                                                                                   | + <u>7,9</u><br>+ <u>7,9</u><br>+ <u>1,5</u>                                                                           | 22 K/W<br>\$ TO 220                                                                                                                                                            |

| M |                                            | surface treatment     SA=black anodised     MI=solderable                         | ittern as well, e.g. FK 211 SA                                                                                         |                                                                                                                                                                                |

| N | C 7 Heatsi<br>GEL th                       | ing springs for transistors<br>nks for D PAK<br>ermal conductive foil<br>tor caps | → C 17 Mountin<br>→ E 7 Mountin                                                                                        | g material for semiconduct. $\rightarrow$ E 34 – 38<br>g pads $\rightarrow$ E 36<br>g pads for transistors $\rightarrow$ E 37<br>g parts for heatsinks $\rightarrow$ E 39 – 40 |

ANEXO 5: ESQUEMÁTICO DEL CIRCUITO DE MANDO DE COMPUERTA CON EL RESPECTIVO BOARD.

**ANEXO 6**: ESQUEMÁTICO DE LA FUENTE PARA EL CIRCUITO DE CAMPO DEL MOTOR CON EL RESPECTIVO BOARD.

ANEXO 7: ESQUEMÁTICO DEL CIRCUITO DE CONTROL CON EL RESPECTIVO BOARD.

# KBU4A, KBU4B, KBU4D, KBU4G, KBU4J, KBU4K, KBU4M

www.vishay.com

$V_F$  at  $I_F = 4 A$

T<sub>J</sub> max.

Diode variations

VISHAY

Vishay General Semiconductor

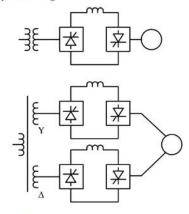

### **Single-Phase Bridge Rectifier**

- UL recognition, file number E54214 · Ideal for printed circuit boards

- High surge current capability

- High case dielectric strength of 1500  $V_{\text{RMS}}$ Solder dip 275 °C max. 10 s, per JESD 22-B106

Compliant

- Material categorization: for definitions of compliance please see www.vishay.com/doc?99912

#### **TYPICAL APPLICATIONS**

General purpose use in AC/DC bridge full wave rectification for monitor, TV, printer, SMPS, adapter, audio equipment, and home appliances applications.

#### **MECHANICAL DATA**

Case: KBU

Molding compound meets UL 94 V-0 flammability rating Base P/N-E4 - RoHS-compliant, commercial grade

Terminals: Silver plated leads, solderable per J-STD-002 and JESD22-B102

Polarity: As marked on body

Mounting Torque: 10 cm-kg (8.8 inches-lbs) max.

Recommended Torque: 5.7 cm-kg (5 inches-lbs)

| MAXIMUM RATINGS                                                           | (T <sub>A</sub> = 25 °C unle          | ss otherw                         | vise note | ed)   |       |            |       |       |       |      |  |  |  |  |  |

|---------------------------------------------------------------------------|---------------------------------------|-----------------------------------|-----------|-------|-------|------------|-------|-------|-------|------|--|--|--|--|--|

| PARAMETER                                                                 |                                       | SYMBOL                            | KBU4A     | KBU4B | KBU4D | KBU4G      | KBU4J | KBU4K | KBU4M | UNIT |  |  |  |  |  |

| Maximum repetitive peak reverse voltage                                   |                                       | V <sub>RRM</sub>                  | 50        | 100   | 200   | 400        | 600   | 800   | 1000  | V    |  |  |  |  |  |

| Maximum RMS voltage                                                       |                                       | V <sub>RMS</sub>                  | 35        | 70    | 140   | 280        | 420   | 560   | 700   | V    |  |  |  |  |  |

| Maximum DC blocking voltage                                               |                                       | V <sub>DC</sub>                   | 50        | 100   | 200   | 400        | 600   | 800   | 1000  | V    |  |  |  |  |  |

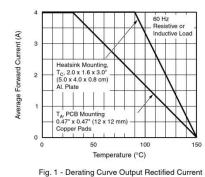

| Maximum average forward                                                   | $T_{C} = 100 \ ^{\circ}C \ ^{(1)}$    | 6                                 | 4.0       |       |       |            |       |       |       |      |  |  |  |  |  |

| rectified output current at                                               | T <sub>A</sub> = 30 °C <sup>(2)</sup> | F(AV)                             |           |       |       | 4.0        |       |       |       | — A  |  |  |  |  |  |

| Peak forward surge current single sine-wave<br>superimposed on rated load |                                       | I <sub>FSM</sub>                  | 200       |       |       |            |       |       |       | A    |  |  |  |  |  |

| Operating junction and storage                                            | temperature range                     | T <sub>J</sub> , T <sub>STG</sub> |           |       | -     | 50 to + 15 | 60    |       |       | °C   |  |  |  |  |  |

#### Notes

(1) Units mounted on a 2.0" x 1.6" x 0.3" thick (5 cm x 4 cm x 0.8 cm) aluminum plate

(2) Units mounted on PCB with 0.5" x 0.5" (12 mm x 12 mm) copper pads and 0.375" (9.5 mm) lead length

1.0 V

150 °C

In-Line

| ELECTRICAL CHAR                                    | ACTERISTICS (T,         | <sub>A</sub> = 25 °C | unless of          | otherwis | e noted | )     |       |       |       |      |

|----------------------------------------------------|-------------------------|----------------------|--------------------|----------|---------|-------|-------|-------|-------|------|

| PARAMETER                                          | TEST CONDITIONS         | SYMBOL               | KBU4A              | KBU4B    | KBU4D   | KBU4G | KBU4J | KBU4K | KBU4M | UNIT |

| Maximum instantaneous<br>forward drop per diode    | I <sub>F</sub> = 4.0 A  | V <sub>F</sub>       | 1.0                |          |         |       |       | v     |       |      |

| Maximum DC reverse<br>current at rated DC blocking | T <sub>A</sub> = 25 °C  | Т                    | 5.0                |          |         |       |       | μA    |       |      |

| voltage per diode                                  | T <sub>A</sub> = 125 °C | I IR                 | I <sub>R</sub> 1.0 |          |         |       |       |       | mA    |      |

Revision: 14-May-14

Document Number: 88656

1 For technical questions within your region: DiodesAmericas@vishay.com, DiodesAsia@vishay.com, DiodesEurope@vishay.com THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

KBU4A, KBU4B, KBU4D, KBU4G, KBU4J, KBU4K, KBU4M VISHAY.

www.vishay.com

Vishay General Semiconductor

| THERMAL CHARACTERISTICS (T <sub>A</sub> = 25 °C unless otherwise noted) |                  |        |       |       |         |       |       |       |      |  |

|-------------------------------------------------------------------------|------------------|--------|-------|-------|---------|-------|-------|-------|------|--|

| PARAMETER                                                               | SYMBOL           | KBU4A  | KBU4B | KBU4D | KBU4G   | KBU4J | KBU4K | KBU4M | UNIT |  |

| Typical thermal resistance                                              | R <sub>0JA</sub> | 19 (2) |       |       |         |       |       |       | °C/W |  |

| Typical memai resistance                                                | R <sub>0JL</sub> |        |       |       | 4.0 (1) |       |       |       | 0/11 |  |

#### Notes

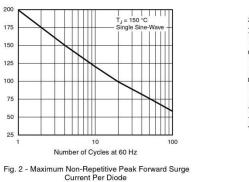

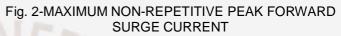

200

175

150

125 100 75

> 50 25

Peak Forward Surge Current (A)

(i) Units mounted on a 2.0" x 1.6" x 0.3" thick (5 cm x 4 cm x 0.8 cm) aluminum plate

(2) Units mounted on PCB with 0.5" x 0.5" (12 mm x 12 mm) copper pads and 0.375" (9.5 mm) lead length

| ORDERING INF  | ORDERING INFORMATION (Example) |                        |               |                      |  |  |  |  |  |

|---------------|--------------------------------|------------------------|---------------|----------------------|--|--|--|--|--|

| PREFERRED P/N | UNIT WEIGHT (g)                | PREFERRED PACKAGE CODE | BASE QUANTITY | DELIVERY MODE        |  |  |  |  |  |

| KBU4J-E4/51   | 8.0                            | 51                     | 250           | Anti-static PVC tray |  |  |  |  |  |

100

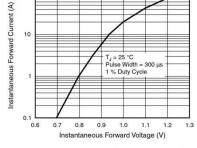

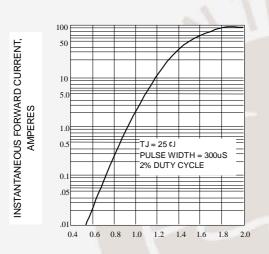

RATINGS AND CHARACTERISTICS CURVES (T<sub>A</sub> = 25 °C unless otherwise noted)

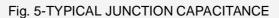

Fig. 3 - Typical Forward Characteristics Per Diode

Revision: 14-May-14 Document Number: 88656 2 For technical questions within your region: DiodesAmericas@vishay.com, DiodesAsia@vishay.com, DiodesEurope@vishay.com THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

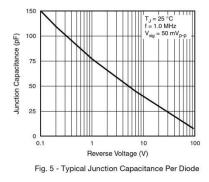

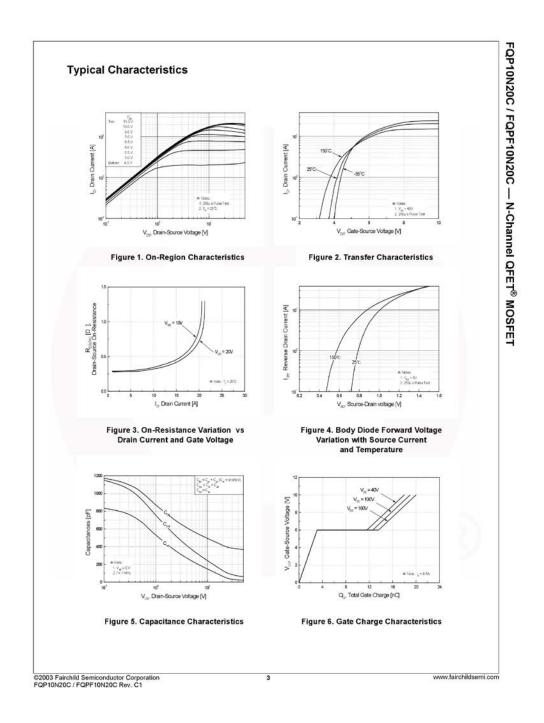

PACKAGE OUTLINE DIMENSIONS in inches (millimeters)

Revision: 14-May-14

3

Document Number: 88656

For technical questions within your region: DiodesAmericas@vishay.com, DiodesAsia@vishay.com, DiodesAsia@vishay.com, DiodesAsia@vishay.com

Document Number: 88656

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Vishay

### Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

### Material Category Policy

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.

Revision: 02-Oct-12

1

Document Number: 91000

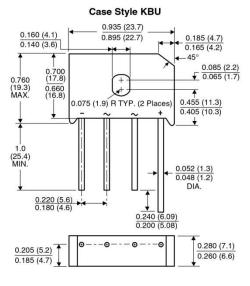

# FAIRCHILD

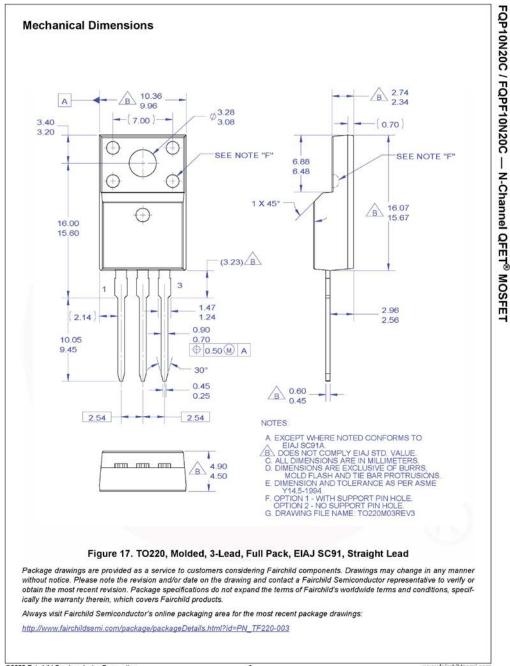

# FQP10N20C / FQPF10N20C N-Channel QFET<sup>®</sup> MOSFET 200 V, 9.5 A, 360 mΩ

#### Features

- + 9.5 A, 200 V,  $R_{DS(on)}$  = 360 m $\Omega$  (Max.) @  $V_{GS}$  = 10 V,  $I_{D}$  = 4.75 A

- Low Gate Charge (Typ. 20 nC)

- Low Crss (Typ. 40.5 pF)

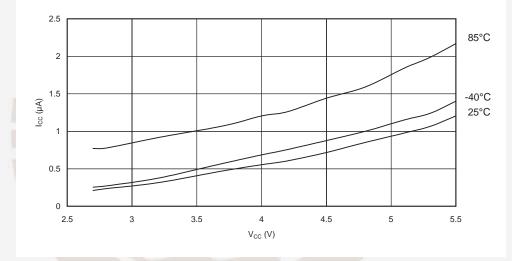

- 100% Avalanche Tested

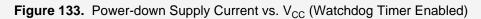

November 2013

FQP10N20C / FQPF10N20C — N-Channel QFET® MOSFET

### Description

This N-Channel enhancement mode power MOSFET is produced using Fairchild Semiconductor's proprietary planar stripe and DMOS technology. This advanced MOSFET technology has been especially tailored to reduce on-state resistance, and to provide superior switching performance and high avalanche energy strength. These devices are suitable for switched mode power supplies, active power factor correction (PFC), and electronic lamp ballasts.

### MOSFET Maximum Ratings T<sub>C</sub> = 25°C unless otherwise noted.

| Symbol               |                                                | Parameter                             |          | FQP10N20C | FQPF10N20C | Unit |

|----------------------|------------------------------------------------|---------------------------------------|----------|-----------|------------|------|

| V <sub>DSS</sub>     | Drain to Source Voltage                        | 1                                     |          | 20        | 00         | v    |

| -                    | Desis Ourset                                   | -Continuous (T <sub>C</sub> = 25°C)   |          | 9.5       | 9.5 *      | A    |

| D                    | Drain Current                                  | -Continuous (T <sub>C</sub> = 100°C)  | 1        | 6.0       | 6.0 *      | A    |

| DM                   | Drain Current                                  | - Pulsed                              | (Note 1) | 38        | 38 *       | A    |

| V <sub>GSS</sub>     | Gate to Source Voltage                         |                                       |          | ±         | 30         | ٧    |

| E <sub>AS</sub>      | Single Pulsed Avalanch                         | e Energy                              | (Note 2) | 2         | 10         | mJ   |

| AR                   | Avalanche Current                              |                                       | (Note 1) | 9         | .5         | A    |

| EAR                  | Repetitive Avalanche E                         | nergy                                 | (Note 1) | 7         | .2         | mJ   |

| dv/dt                | Peak Diode Recovery d                          | v/dt                                  | (Note 3) | 5         | .5         | V/ns |

| PD                   | Power Dissipation                              | $(T_{C} = 25^{\circ}C)$               |          | 72        | 38         | w    |

| r D                  | S                                              | - Derate above 25°C                   |          | 0.57      | 0.3        | W/°C |

| TJ, T <sub>STG</sub> | Operating and Storage                          | Temperature Range                     |          | -55 to    | °C         |      |

| Τ <sub>L</sub>       | Maximum Lead Temper<br>1/8" from Case for 5 Se | ature for Soldering Purpose,<br>conds |          | 3         | 00         | °C   |

|                      | nited by maximum junction ter                  | nperature                             |          |           |            |      |

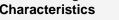

| Thermal              | Characteristics                                |                                       |          |           |            |      |

| Symbol               |                                                | Parameter                             |          | FQP10N20C | FQPF10N20C | Unit |

| R <sub>eJC</sub>     | Thermal Resistance, Ju                         | inction to Case, Max                  |          | 1.74      | 3.33       | °C/V |

| R <sub>BJA</sub>     | Thermal Resistance, Ju                         | nction to Ambient, Max                |          | 62.5      | 62.5       | °C/V |

©2003 Fairchild Semiconductor Corporation FQP10N20C / FQPF10N20C Rev. C1

10

www.fairchildsemi.com

| Dev                                     | ice Marking                           | Device                                                                                                                                         | Pa                                                                                                | ckage                                           | Reel     | Size | Tape Width | ı Qı | antity   |  |

|-----------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------|----------|------|------------|------|----------|--|

| FC                                      | P10N20C                               | FQP10N20C                                                                                                                                      |                                                                                                   | D-220                                           | Tu       | be   | N/A        |      | 50 units |  |

| FQ                                      | PF10N20C                              | FQPF10N20C                                                                                                                                     | тс                                                                                                | -220F                                           | Tu       | be   | N/A        | 50   | ) units  |  |

| Electric                                | al Characte                           | <b>ristics</b> T <sub>C</sub> = 25°C ur                                                                                                        | nless otherwise n                                                                                 | oted.                                           | h.:      |      |            | 10   |          |  |

| Symbol                                  | Pa                                    | rameter                                                                                                                                        | Test (                                                                                            | onditions                                       |          | Min  | Тур        | Max  | Unit     |  |

| Off Cha                                 | racteristics                          |                                                                                                                                                |                                                                                                   |                                                 |          |      |            |      |          |  |

| BVDSS                                   | Drain-Source Bre                      | akdown Voltage                                                                                                                                 | V <sub>GS</sub> = 0 V, I <sub>D</sub> =                                                           | 250 µA                                          |          | 200  |            |      | V        |  |

| $\Delta BV_{DSS}$<br>/ $\Delta T_J$     | Breakdown Voltag                      | ge Temperature Coeffi-                                                                                                                         | I <sub>D</sub> = 250 μA, Re                                                                       | ferenced to 25                                  | 5°C      |      | 0.28       |      | V/°C     |  |

| IDSS                                    | Zero Gate Voltage                     | e Drain Current                                                                                                                                | V <sub>DS</sub> = 200 V, V <sub>GS</sub> = 0 V<br>V <sub>DS</sub> = 160 V, T <sub>C</sub> = 125°C |                                                 |          |      |            | 10   | μA       |  |

|                                         |                                       |                                                                                                                                                | $V_{DS} = 160 \text{ V}, 1_0$<br>$V_{GS} = 30 \text{ V}, V_{D}$                                   |                                                 |          | 1970 | 1          | 100  | μΑ       |  |

| IGSSF                                   |                                       | ge Current, Forward                                                                                                                            | 00                                                                                                |                                                 |          | 3.00 | 100        | nA   |          |  |

| IGSSR                                   | Gate-Body Leaka                       | ge Current, Reverse                                                                                                                            | V <sub>GS</sub> = -30 V, V <sub>E</sub>                                                           | <sub>S</sub> = 0 V                              | -        |      | -          | -100 | nA       |  |

|                                         | racteristics                          |                                                                                                                                                | F                                                                                                 | 050 4                                           |          |      | i an i     |      |          |  |

| V <sub>GS(th)</sub>                     | Gate Threshold V                      | and the second                               | $V_{DS} = V_{GS}, I_D =$                                                                          | 250 µA                                          |          | 2.0  |            | 4.0  | V        |  |

| R <sub>DS(on)</sub>                     | Static Drain-Source                   |                                                                                                                                                |                                                                                                   | = 4.75 A                                        |          | -    | 0.29       | 0.36 | Ω        |  |

| 9FS                                     | Forward Transcor                      | Forward Transconductance                                                                                                                       |                                                                                                   | V <sub>DS</sub> = 40 V, I <sub>D</sub> = 4.75 A |          |      | 5.5        |      | S        |  |

| Dynami                                  | c Characterist                        | tics                                                                                                                                           |                                                                                                   |                                                 |          |      |            |      |          |  |

| Ciss                                    | Input Capacitance                     | 9                                                                                                                                              | V <sub>DS</sub> = 25 V, V <sub>G</sub>                                                            | = 0 V                                           | 1        |      | 395        | 510  | pF       |  |

| Coss                                    | Output Capacitan                      | ce                                                                                                                                             | f = 1.0 MHz                                                                                       | 5,                                              | 1        | -    | 97         | 125  | pF       |  |

| Crss                                    | Reverse Transfer Capacitance          |                                                                                                                                                |                                                                                                   |                                                 |          |      | 40.5       | 53   | pF       |  |

| Switchi                                 | ng Characteris                        | stics                                                                                                                                          |                                                                                                   |                                                 |          |      |            |      |          |  |

| t <sub>d(on)</sub>                      | Turn-On Delay Time                    |                                                                                                                                                | V = 100 V I                                                                                       | -054                                            |          |      | 11         | 30   | ns       |  |

| tr                                      | Turn-On Rise Tim                      | le                                                                                                                                             | $V_{DD} = 100 \text{ V}, I_D = 9.5 \text{ A},$<br>$R_G = 25 \Omega$                               |                                                 |          |      | 92         | 190  | ns       |  |

| t <sub>d(off)</sub>                     | Turn-Off Delay Ti                     | urn-Off Delay Time                                                                                                                             |                                                                                                   |                                                 |          |      | 70         | 150  | ns       |  |

| t <sub>f</sub>                          | Turn-Off Fall Time                    | 9                                                                                                                                              |                                                                                                   |                                                 | (Note 4) |      | 72         | 160  | ns       |  |

| Qg                                      | Total Gate Charge                     | 8                                                                                                                                              | V <sub>DS</sub> = 160 V, I <sub>D</sub>                                                           | = 9 5 A                                         |          |      | 20         | 26   | nC       |  |

| Qgs                                     | Gate-Source Cha                       | rge                                                                                                                                            | V <sub>GS</sub> = 10 V                                                                            | 1000                                            |          |      | 3.1        |      | nC       |  |

| Q <sub>gd</sub>                         | Gate-Drain Charg                      | le                                                                                                                                             | (Note 4)                                                                                          |                                                 | (Note 4) |      | 10.5       |      | nC       |  |

| Drain-S                                 | ource Diode C                         | haracteristics and                                                                                                                             | l Maximum R                                                                                       | atings                                          |          |      |            |      |          |  |

| Is                                      |                                       | uous Drain-Source Diode                                                                                                                        |                                                                                                   |                                                 | -        |      |            | 9.5  | A        |  |

| I <sub>SM</sub>                         |                                       | Drain-Source Diode For                                                                                                                         |                                                                                                   |                                                 |          |      | 1.4        | 38   | A        |  |

| V <sub>SD</sub>                         |                                       | de Forward Voltage                                                                                                                             | V <sub>GS</sub> = 0 V, I <sub>S</sub> =                                                           | 9.5 A                                           |          |      |            | 1.5  | v        |  |

| trr                                     | Reverse Recover                       |                                                                                                                                                | V <sub>GS</sub> = 0 V, I <sub>S</sub> =                                                           |                                                 |          |      | 158        |      | ns       |  |

| Qrr                                     | Reverse Recover                       |                                                                                                                                                | dl <sub>F</sub> / dt = 100 A                                                                      |                                                 |          |      | 0.97       |      | μC       |  |

| L = 3.5 mH,<br>I <sub>SD</sub> ≤ 9.5 A, | AS = 9.5 A, V <sub>DD</sub> = 50 V, I | by maximum junction temperati<br>$B = 25 \Omega_c$ starting $T_j = 25^{\circ}C$ .<br>$B V_{DSS}$ starting $T_j = 25^{\circ}C$ .<br>emperature. | ure.                                                                                              |                                                 |          |      |            |      |          |  |

|                                         |                                       |                                                                                                                                                |                                                                                                   |                                                 |          |      |            |      |          |  |

FQP10N20C / FQPF10N20C — N-Channel QFET® MOSFET

©2003 Fairchild Semiconductor Corporation FQP10N20C / FQPF10N20C Rev. C1

9

www.fairchildsemi.com

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably

expected to result in a significant injury of the user.

A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ANTI-COUNTERFEITING POLICY

ANTI-COUNTERFEITING POLICY Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.Fairchildsemi.com, under Sales Support. Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handing and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand berlind all warranties and will appropriately address and warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                                |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                             |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later<br>date. Fairchild Semiconductor reserves the right to make changes at any time without<br>notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                                     |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild<br>Semiconductor. The datasheet is for reference information only.                                                       |

©2003 Fairchild Semiconductor Corporation FQP10N20C / FQPF10N20C Rev. C1

10

www.fairchildsemi.com

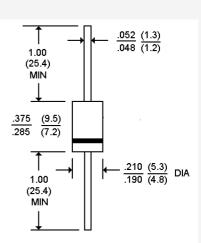

# MR850 THRU MR856

# SOFT RECOVERU, FAST SWITCHING PLASTIC RECTIFIER VOLTAGE - 50 to 600 Volts CURRENT - 3.0 Amperes

# **FEATURES**

- High surge current capability

- Plastic package has Underwriters Laboratory Flammability Classification 94V-O

- Void-free molded plastic package

- 3.0 ampere operation at T<sub>A</sub>=50 ¢J with no thermal runaway

- Exceeds environmental standards of MIL-S-19500/228

- Fast switching for high efficiency

# MECHANICAL DATA

Case: JEDEC DO-201AD molded plastic Terminals: Plated Axial leads, solderable per MIL-STD-750, Method 2026 Polarity: Color Band denotes end Mounting Position: Any

Weight: 0.04 ounce, 1.1 gram

Dimensions in inches and (millimeters)

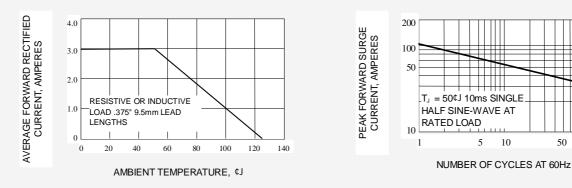

# MAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICS

Ratings at 25 ¢J ambient temperature unless otherwise specified.

Resistive or inductive load.

|                                                                                                     | SYMBOLS           | MR850 | MR851 | MR852     | MR854 | MR856 | UNITS |

|-----------------------------------------------------------------------------------------------------|-------------------|-------|-------|-----------|-------|-------|-------|

| Maximum Recurrent Peak Reverse Voltage                                                              | V <sub>RRM</sub>  | 50    | 100   | 200       | 400   | 600   | Volts |

| Maximum RMS Voltage                                                                                 | V <sub>RMS</sub>  | 35    | 70    | 140       | 280   | 480   | Volts |

| Maximum DC Blocking Voltage                                                                         | V <sub>DC</sub>   | 50    | 100   | 200       | 400   | 600   | Volts |

| Maximum Average Forward Rectified Current<br>.375"(9.5mm) Lead Length at T <sub>A</sub> =50 ¢J      | I <sub>(AV)</sub> |       | V     | 3.0       |       |       | Amps  |

| Peak Forward Surge Current 10ms single half sine-<br>wave superimposed on rated load at $T_A=25$ ¢J | I <sub>FSM</sub>  | Ś     | 1     | 100.0     |       |       | Amps  |

| Maximum Repetitive Peak Forward Surge(Note1)                                                        | I <sub>FRM</sub>  |       |       | 10.0      | 5     |       | Amps  |

| Maximum Instantaneous Forward Voltage at 3.0A                                                       | VF                |       | 1     | 1.25      |       | Volts |       |

| Maximum DC Reverse Current T <sub>A</sub> =25 ¢J                                                    | I <sub>R</sub>    |       |       | 10.0      |       |       | £g A  |

| at Rated DC Blocking Voltage T <sub>A</sub> =100 ¢J                                                 | $\sim 1 $         |       |       | 500.0     |       |       | £g A  |

| Maximum Reverse Recovery Time(Note 3) TJ=25 CJ                                                      | T <sub>RR</sub>   |       |       | 150       |       |       | ns    |

| Typical Junction capacitance (Note 2)                                                               | CJ                |       |       | 60        |       |       | ₽F    |

| Typical Thermal Resistance (Note 4)                                                                 | R £KJA            |       |       | 15.0      |       |       | ¢J/W  |

| Operating Junction Temperature Range                                                                | TJ                |       | -     | 50 to +12 | 5     |       | ¢J    |

| Storage Temperature Range                                                                           | T <sub>STG</sub>  |       | -     | 50 to +15 | 0     |       | ¢J    |

NOTES:

- 1. Repetitive Peak Forward Surge Current at f<15KHz

- 2. Measured at 1 MHz and applied reverse voltage of 4.0 Volts

- 3. Reverse Recovery Test Conditions:  $I_F=0.5A$ ,  $I_R=1.0A$ ,  $I_{rr}=0.25A$

- 4. Thermal Resistance From Junction to Ambient at 0.375" (9.5mm) lead length with both leads to heat sink

# DO-201AD

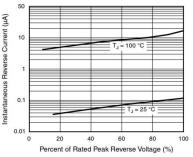

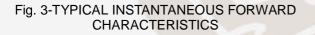

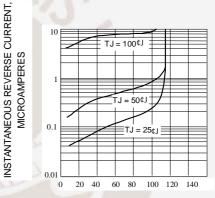

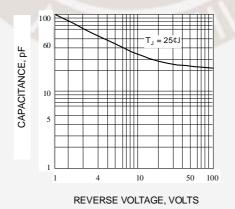

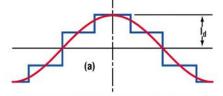

# RATING AND CHARACTERISTIC CURVES

MR850 THRU MR856

Fig. 1-FORWARD CURRENT DERATING CURVE

100

INSTANTANEOUS FORWARD VOLTAGE, VOLTS

PERCENT OF RATED PEAK REVERSE VOLTAGE

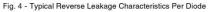

## Fig. 4-TYPICAL REVERSE CHARACTERISTICS

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

**Vishay Semiconductors**

# High Speed Optocoupler, 1 MBd, **Photodiode with Transistor Output**

8 C (V<sub>cc</sub>)

7 B (V<sub>B</sub>)

6 C (V\_)

5 E (GND)

### FEATURES

Isolation test voltages: 5300 V<sub>RMS</sub>

- TTL compatible

- · High bit rates: 1 Mbit/s

- · High common-mode interference immunity

- Bandwidth 2 MHz

- · Open-collector output

- · External base wiring possible

- · Material categorization:

for definitions of compliance please see www.vishay.com/doc?99912

#### AGENCY APPROVALS

- UL1577 file no. E52744, double protection

- DIN EN 60747-5-5 (VDE0884-5) available with option 1

- cUL components acceptance service no. 5A

- CQC GB8898-2011, GB4943.1-2011

### DESCRIPTION

The 6N135 and 6N136 are optocouplers with a GaAlAs infrared emitting diode, optically coupled with an integrated photo detector which consists of a photo diode and a high-speed transistor in a DIP-8 plastic package.

NC 1

A 2

C 3

NC 4

18.

DD

6VE

COC

Signals can be transmitted between two electrically separated circuits up to frequencies of 2 MHz. The potential difference between the circuits to be coupled should not exceed the maximum permissible reference voltages.

| 6 N 1 3 #                  | - X 0 # #                  | TAPE<br>AND<br>REEL Option 7<br>Option 9<br>Option 9<br>Option 9<br>Option 9<br>Option 9<br>Option 9<br>Option 9<br>Option 9 |  |  |  |

|----------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AGENCY CERTIFIED / PACKAGE | CTR                        | 12 va min                                                                                                                    |  |  |  |

| UL, CSA                    | ≥7                         | ≥ 19                                                                                                                         |  |  |  |

| DIP-8                      | 6N135                      | 6N136                                                                                                                        |  |  |  |

| DIP-8, 400 mil, option 6   | -                          | 6N136-X006                                                                                                                   |  |  |  |

| SMD-8, option 7            | 6N135-X007T (1)            | 6N136-X007T (1)                                                                                                              |  |  |  |

| SMD-8, option 9            | ÷                          | 6N136-X009T (1)                                                                                                              |  |  |  |

| VDE, UL, CSA               | ≥7                         | ≥ 19                                                                                                                         |  |  |  |

| DIP-8                      |                            | 6N136-X001                                                                                                                   |  |  |  |

|                            |                            |                                                                                                                              |  |  |  |

| SMD-8, option 7            | 6N135-X017T <sup>(1)</sup> | 6N136-X017T                                                                                                                  |  |  |  |

Note (1) Also available in tubes; do not add T to end

Document Number: 83604 1 For technical questions, contact: optocoupleranswers@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

HALOGEN

FREE

GREEN

VISHAY.

# 6N135, 6N136

www.vishay.com

### Vishay Semiconductors

| PARAMETER                     | CONDITION                                               | SYMBOL           | VALUE       | UNIT |

|-------------------------------|---------------------------------------------------------|------------------|-------------|------|

| INPUT                         | *                                                       |                  |             |      |

| Reverse voltage               |                                                         | VR               | 5           | V    |

| Forward current               |                                                         | IF               | 25          | mA   |

| Peak forward current          | t = 1 ms, duty cycle 50 %                               | IFSM             | 50          | mA   |

| Maximum surge forward current | t ≤ 1 µs, 300 pulses/s                                  |                  | 1           | A    |

| Thermal resistance            |                                                         | Rth              | 700         | K/W  |

| Power dissipation             | T <sub>amb</sub> = 70 °C                                | Pdiss            | 45          | mW   |

| OUTPUT                        | ······································                  | •                |             |      |

| Supply voltage                |                                                         | Vs               | -0.5 to 15  | V    |

| Output voltage                |                                                         | Vo               | -0.5 to 15  | V    |

| Emitter base voltage          |                                                         | VEBO             | 5           | V    |

| Output current                |                                                         | lo               | 8           | mA   |

| Maximum output current        |                                                         |                  | 16          | mA   |

| Base current                  |                                                         | IB               | 5           | mA   |

| Thermal resistance            |                                                         |                  | 300         | K/W  |

| Power dissipation             | T <sub>amb</sub> = 70 °C                                | Pdiss            | 100         | mW   |

| COUPLER                       |                                                         |                  |             |      |

| Storage temperature range     |                                                         | T <sub>stg</sub> | -55 to +150 | °C   |

| Ambient temperature range     |                                                         | Tamb             | -55 to +100 | °C   |

| Soldering temperature         | max. ≤ 10 s, dip soldering<br>≥ 0.5 mm from case bottom | T <sub>sid</sub> | 260         | °C   |

Note

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. Functional operation of the device is not

implied at these or any other conditions in excess of those given in the operational sections of this document. Exposure to absolute

maximum ratings for extended periods of the time can adversely affect reliability.

| PARAMETER                                | TEST CONDITION                                                        | PART  | SYMBOL                    | MIN.    | TYP. | MAX. | UNIT  |

|------------------------------------------|-----------------------------------------------------------------------|-------|---------------------------|---------|------|------|-------|

| INPUT                                    |                                                                       |       |                           |         |      |      |       |

| Forward voltage                          | I <sub>F</sub> = 16 mA                                                |       | VF                        | -       | 1.33 | 1.9  | V     |

| Breakdown voltage                        | I <sub>R</sub> = 10 μA                                                |       | VBR                       | 5       | -    |      | V     |

| Reverse current                          | V <sub>R</sub> = 5 V                                                  |       | IR                        | 1       | 0.5  | 10   | μΑ    |

| Capacitance                              | $V_R = 0 V, f = 1 MHz$                                                |       | Co                        | 17      | 30   | -    | pF    |

| Temperature coefficient, forward voltage | I <sub>F</sub> = 16 mA                                                |       | $\Delta V_F / \Delta T_A$ | 12      | -1.7 | ÷.   | mV/°C |

| OUTPUT                                   |                                                                       |       |                           |         |      |      |       |

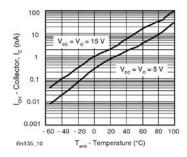

| Logic low supply current                 | I <sub>F</sub> = 16 mA, V <sub>O</sub> = open, V <sub>CC</sub> = 15 V |       | ICCL                      |         | 150  | -    | μΑ    |

| Logic high supply current                | $I_F = 0 \text{ mA}, V_O = \text{open}, V_{CC} = 15 \text{ V}$        |       | Іссн                      |         | 0.01 | 1    | μΑ    |

| Output without a track law               | $I_F = 16 \text{ mA}, I_O = 1.1 \text{ mA}, V_{CC} = 4.5 \text{ V}$   | 6N135 | VOL                       | 12      | 0.1  | 0.4  | V     |

| Output voltage, output low               | $I_F = 16 \text{ mA}, I_O = 3.0 \text{ mA}, V_{CC} = 4.5 \text{ V}$   | 6N136 | VOL                       | 10      | 0.1  | 0.4  | V     |

| O dead annual and a think                | $I_F = 0 \text{ mA}, V_O = V_{CC} = 5.5 \text{ V}$                    |       | I <sub>OH</sub>           |         | 3    | 500  | nA    |

| Output current, output high              | $I_F = 0 \text{ mA}, V_O = V_{CC} = 15 \text{ V}$                     |       | lон                       | (a) (a) | 0.01 | 1    | μΑ    |

| COUPLER                                  |                                                                       |       |                           |         |      |      |       |

| Capacitance (input to output)            | f = 1 MHz                                                             |       | Cio                       | -       | 0.6  | -    | pF    |

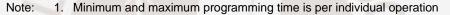

Note

Minimum and maximum values are testing requirements. Typical values are characteristics of the device and are the result of engineering evaluation. Typical values are for information only and are not part of the testing requirements.

Rev. 1.9, 02-Nov-15

2

Document Number: 83604

For technical questions, contact: <u>optocoupleranswers@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

www.vishay.com

### **Vishay Semiconductors**

| PARAMETER        | TEST CONDITION                                                          | PART  | SYMBOL          | MIN. | TYP. | MAX. | UNIT |

|------------------|-------------------------------------------------------------------------|-------|-----------------|------|------|------|------|

| Current transfer |                                                                         | 6N135 | CTR             | 7    | 16   | 100  | %    |

|                  | $I_{\text{F}}$ = 16 mA, $V_{\text{O}}$ = 0.4 V, $V_{\text{CC}}$ = 4.5 V | 6N136 | 6N136 CTR 19 35 |      | %    |      |      |

|                  | $I_F$ = 16 mA, $V_O$ = 0.5 V, $V_{CC}$ = 4.5 V                          | 6N135 | CTR             | 5    | -    | 140  | %    |

|                  |                                                                         | 6N136 | CTR             | 15   |      |      | %    |

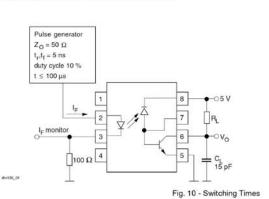

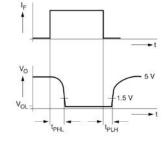

| SWITCHING CHARACTERISTICS (Tamb = 25 °C, unless otherwise specified) |                                                                        |       |                  |      |      |      |      |

|----------------------------------------------------------------------|------------------------------------------------------------------------|-------|------------------|------|------|------|------|

| PARAMETER                                                            | TEST CONDITION                                                         | PART  | SYMBOL           | MIN. | TYP. | MAX. | UNIT |

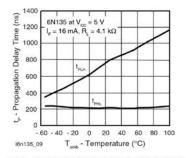

| High to low                                                          | $I_F = 16 \text{ mA}, V_{CC} = 5 \text{ V}, R_L = 4.1 \text{ k}\Omega$ | 6N135 | t <sub>PHL</sub> | 040  | 0.3  | 1.5  | μs   |

|                                                                      | $I_F = 16 \text{ mA}, V_{CC} = 5 \text{ V}, R_L = 1.9 \text{ k}\Omega$ | 6N136 | t <sub>PHL</sub> | -    | 0.2  | 0.8  | μs   |

| Low to high                                                          | $I_F=16~mA,~V_{CC}=5~V,~R_L=4.1~k\Omega$                               | 6N135 | tPLH             |      | 0.3  | 1.5  | μs   |

|                                                                      | $I_F = 16 \text{ mA}, V_{CC} = 5 \text{ V}, R_L = 1.9 \text{ k}\Omega$ | 6N136 | t <sub>PLH</sub> | -    | 0.2  | 0.8  | μs   |

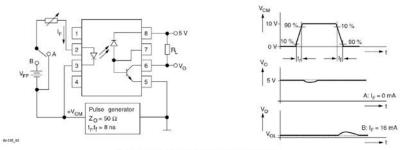

| COMMON MODE TRANSIENT IMMUNITY (T <sub>amb</sub> = 25 °C, unless otherwise specified) |                                                                                                             |       |                 |      |      |      |      |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|-----------------|------|------|------|------|

| PARAMETER                                                                             | TEST CONDITION                                                                                              | PART  | SYMBOL          | MIN. | TYP. | MAX. | UNIT |

| T P 2422                                                                              | $I_F = 0 \text{ mA}, V_{CM} = 10 \text{ V}_{P-P}, V_{CC} = 5 \text{ V}, R_L = 4.1 \text{ k}\Omega$          | 6N135 | CM <sub>H</sub> |      | 1000 |      | V/µs |

| High                                                                                  | $I_F = 0 \text{ mA}, V_{CM} = 10 \text{ V}_{P-P}, V_{CC} = 5 \text{ V}, R_L = 1.9 \text{ k}\Omega$          | 6N136 | CM <sub>H</sub> | 122  | 1000 | - 00 | V/µs |

|                                                                                       | $I_F = 16 \text{ mA}, V_{CM} = 10 \text{ V}_{P-P}, V_{CC} = 5 \text{ V}, \text{ R}_L = 4.1 \text{ k}\Omega$ | 6N135 | [CML]           |      | 1000 | -    | V/µs |

| Low                                                                                   | $I_F = 16 \text{ mA}, V_{CM} = 10 \text{ V}_{P-P}, V_{CC} = 5 \text{ V}, R_L = 1.9 \text{ k}\Omega$         | 6N136 | [CML]           | 1940 | 1000 |      | V/µs |

| PARAMETER                                    | TEST CONDITION                                    | SYMBOL          | VALUE              | UNIT  |

|----------------------------------------------|---------------------------------------------------|-----------------|--------------------|-------|

| Climatic classification                      | According to IEC 68 part 1                        |                 | 55/100/21          |       |

| Pollution degree                             | According to DIN VDE 0109                         |                 | 2                  |       |

| Comparative tracking index                   | Insulation group Illa                             | CTI             | 175                |       |

| Maximum rated withstanding isolation voltage | According to UL1577, t = 1 min                    | Viso            | 5300               | VRMS  |

| Maximum transient isolation voltage          | According to DIN EN 60747-5-5                     | VIOTM           | 8000               | Vpeak |

| Maximum repetitive peak isolation voltage    | According to DIN EN 60747-5-5                     | VIORM           | 890                | Vpeak |

|                                              | T <sub>amb</sub> = 25 °C, V <sub>IO</sub> = 500 V | R <sub>IO</sub> | ≥ 10 <sup>12</sup> | Ω     |

| Isolation resistance                         | $T_{amb} = 100 \ ^{\circ}C, \ V_{IO} = 500 \ V$   | R <sub>IO</sub> | ≥ 10 <sup>11</sup> | Ω     |

| Output safety power                          |                                                   | Pso             | 500                | mW    |

| Input safety current                         |                                                   | Isi             | 300                | mA    |

| Input safety temperature                     |                                                   | Ts              | 175                | °C    |

| Creepage distance                            | DIP-8                                             |                 | ≥7                 | mm    |

| Clearance distance                           | DIP-8                                             |                 | ≥7                 | mm    |

| Creepage distance                            | DIP-8, 400 mil, option 6                          |                 | ≥ 8                | mm    |

| Clearance distance                           | DIP-8, 400 mil, option 6                          |                 | ≥ 8                | mm    |

| Creepage distance                            | SMD-8, option 7                                   |                 | ≥ 8                | mm    |

| Clearance distance                           | SMD-8, option 7                                   |                 | ≥ 8                | mm    |

| Creepage distance                            | SMD-8, option 9                                   |                 | ≥ 8                | mm    |

| Clearance distance                           | SMD-8, option 9                                   |                 | ≥ 8                | mm    |

| Insulation thickness                         |                                                   | DTI             | ≥ 0.4              | mm    |

Note

As per IEC 60747-5-5, § 7.4.3.8.2, this optocoupler is suitable for "safe electrical insulation" only within the safety ratings. Compliance with the safety ratings shall be ensured by means of protective circuits.

Rev. 1.9, 02-Nov-15

Document Number: 83604

3 THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc291000

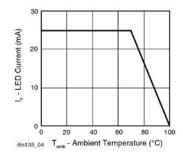

Vishay Semiconductors

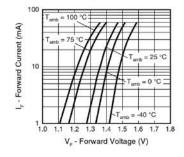

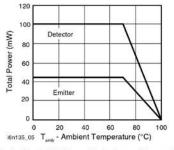

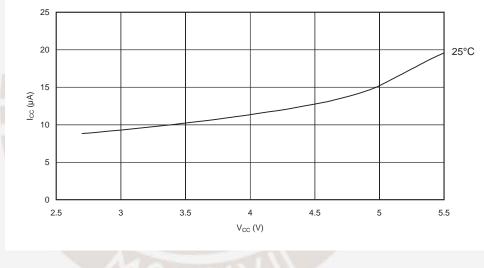

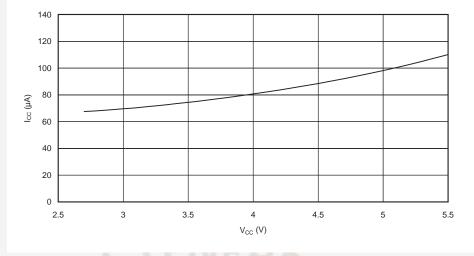

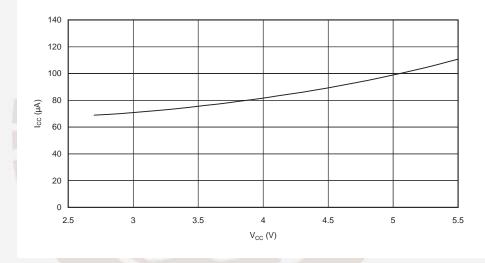

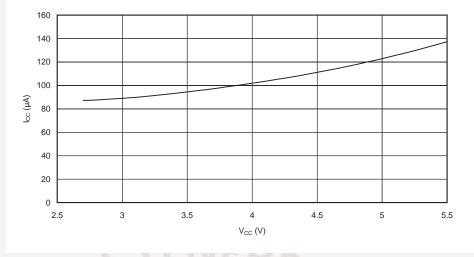

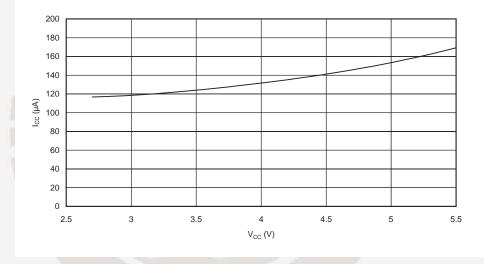

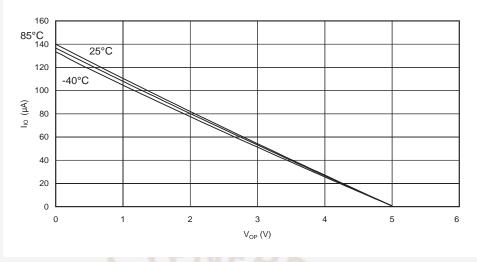

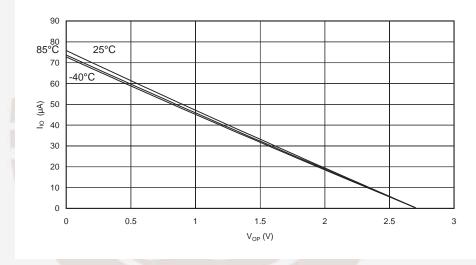

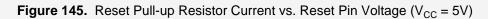

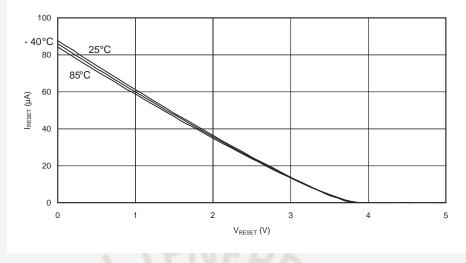

Fig. 1 - LED Forward Current vs. Forward Voltage

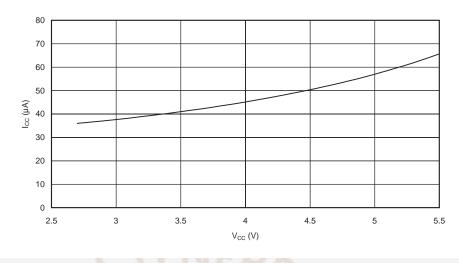

Fig. 2 - Permissible Forward LED Current vs. Temperature

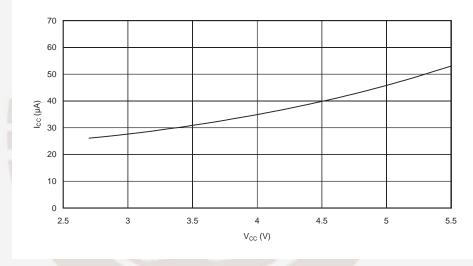

Fig. 3 - Permissible Power Dissipation vs. Temperature

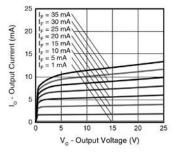

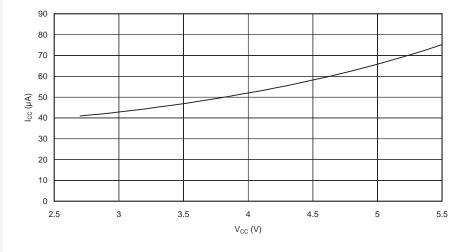

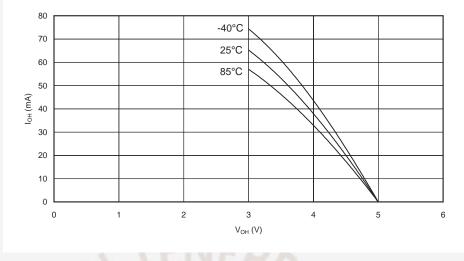

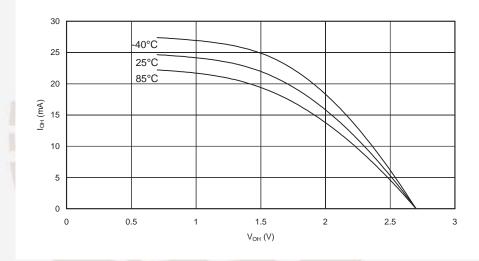

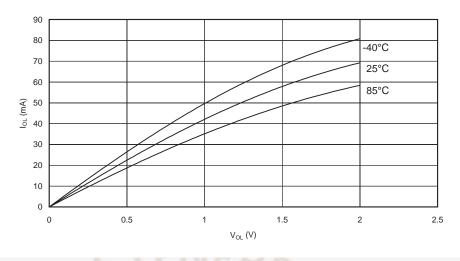

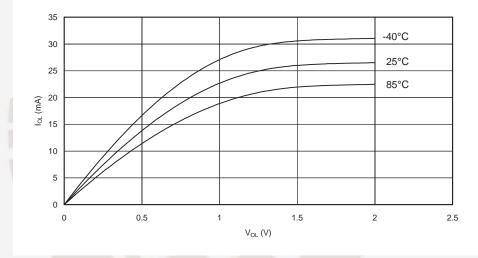

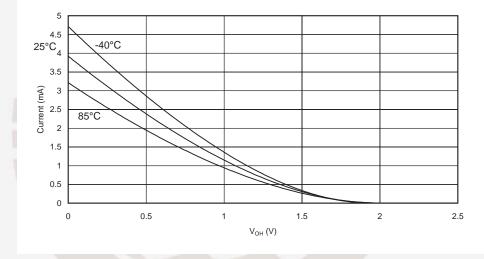

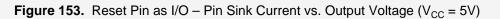

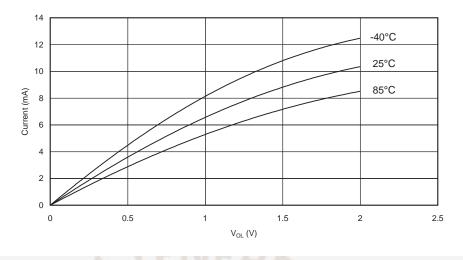

Fig. 4 - Output Current vs. Output Voltage

Rev. 1.9, 02-Nov-15

Document Number: 83604

4 For technical questions, contact: optocoupleranswers@vishay.com THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Vishay Semiconductors

$V_{cc}=5~V,~R_{L}=100~\Omega$

I<sub>F</sub> - Forward Current (mA)

Fig. 9 - Small Signal Current Transfer Ratio vs. Quiescent Input Current

0.6

0.5

0.4

0.3

0.2

0.1

i6n135\_11

0

0 5 10 15 20 25

∆l<sub>F</sub>/∆l<sub>o</sub> - Small Signal Current Transfer Ratio

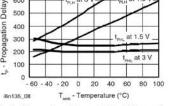

Fig. 7 - Propagation Delay vs. Ambient Temperature

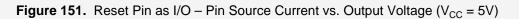

Fig. 8 - Logic High Output Current vs. Temperature

Vishay Semiconductors

Fig. 11 - Common-Mode Interference Immunity

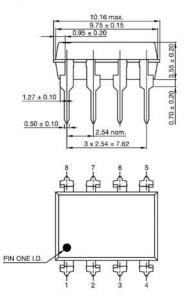

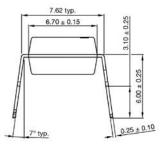

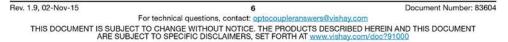

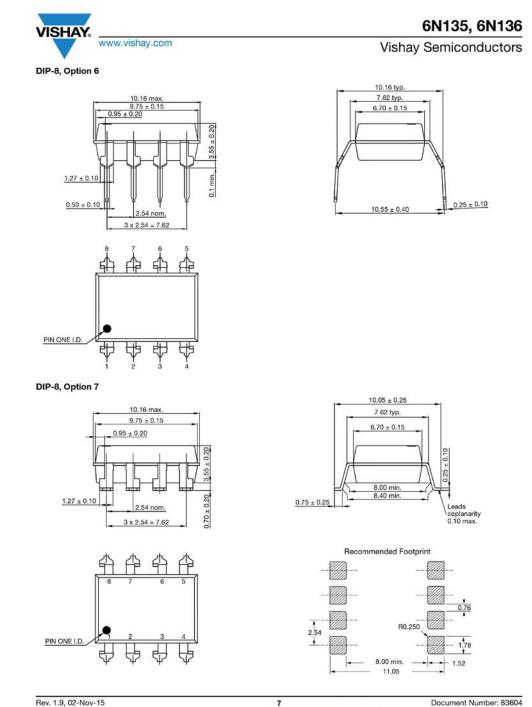

### PACKAGE DIMENSIONS (in millimeters)

DIP-8, Standard

Rev. 1.9, 02-Nov-15

Document Number: 83604

For technical questions, contact: <u>optocoupleranswers@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc291000</u>

Document Number: 83604

Rev. 1.9, 02-Nov-15

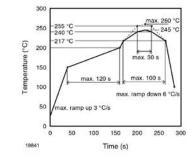

SOLDER PROFILES

300

250

200

150

50

94 8626

Temperature (°C)

35 °C

ca. 200 K

00 °C to

. .

50 100 150 200

130 100

5 s

ead temperatu

full line: typica

process limits

250

dotted line:

5 K/s • •

Time (s)

Fig. 14 - Wave Soldering Double Wave Profile According to J-STD-020 for DIP-8 Devices

8 For technical questions, contact: <u>optocoupleranswers@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc291000</u>

Vishay Semiconductors

### HANDLING AND STORAGE CONDITIONS

ESD level: HBM class 2 Floor life: unlimited Conditions:  $T_{amb} <$  30 °C, RH < 85 % Moisture sensitivity level 1, according to J-STD-020

Rev. 1.9, 02-Nov-15

9

Document Number: 83604

For technical questions, contact: <u>optocoupleranswers@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

Vishay

### Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular application with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

## Material Category Policy

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.

Revision: 02-Oct-12

1

Document Number: 91000

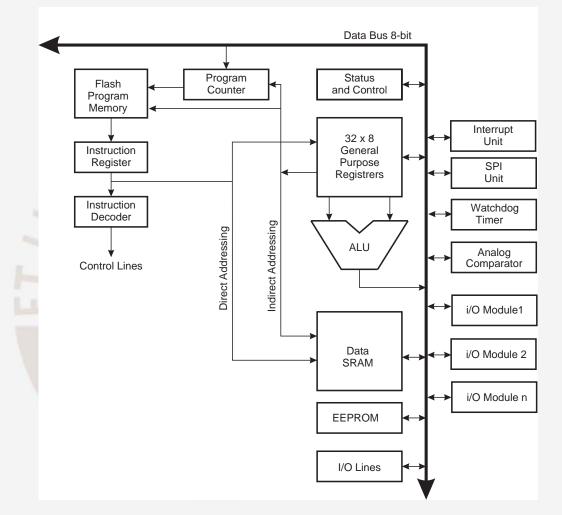

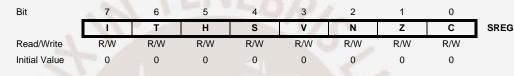

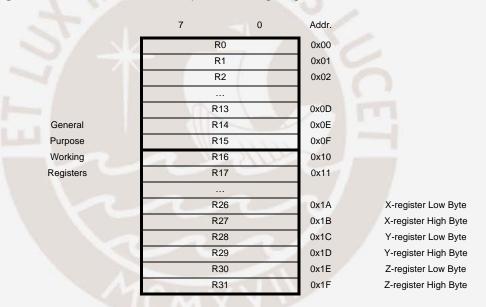

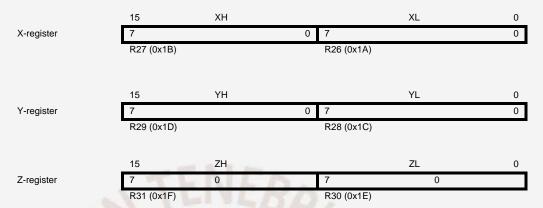

### **Features**

- High-performance, Low-power Atmel<sup>®</sup>AVR<sup>®</sup> 8-bit Microcontroller

- Advanced RISC Architecture

- 130 Powerful Instructions Most Single-clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16MIPS Throughput at 16MHz

- On-chip 2-cycle Multiplier

- High Endurance Non-volatile Memory segments

- 8Kbytes of In-System Self-programmable Flash program memory

- 512Bytes EEPROM

- 1Kbyte Internal SRAM

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C<sup>(1)</sup>

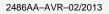

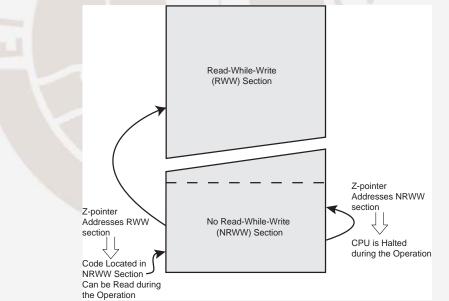

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program **True Read-While-Write Operation**

- Programming Lock for Software Security

- Peripheral Features

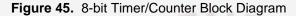

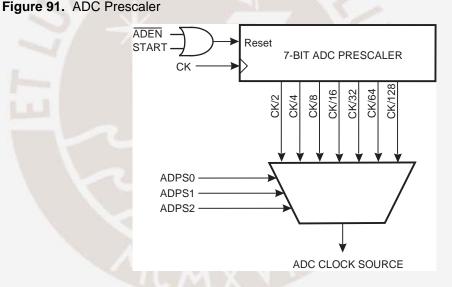

- Two 8-bit Timer/Counters with Separate Prescaler, one Compare Mode

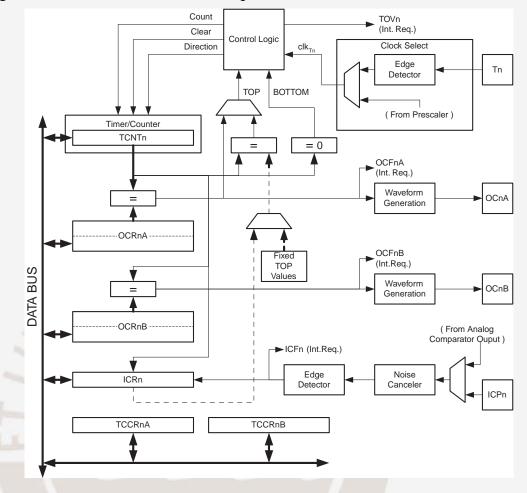

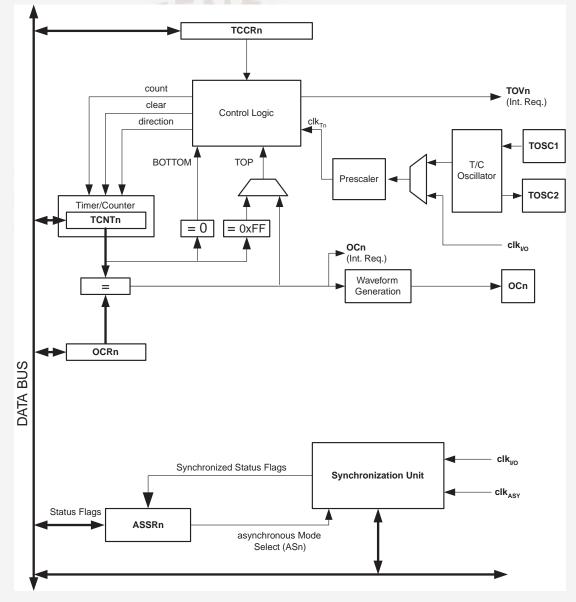

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Three PWM Channels

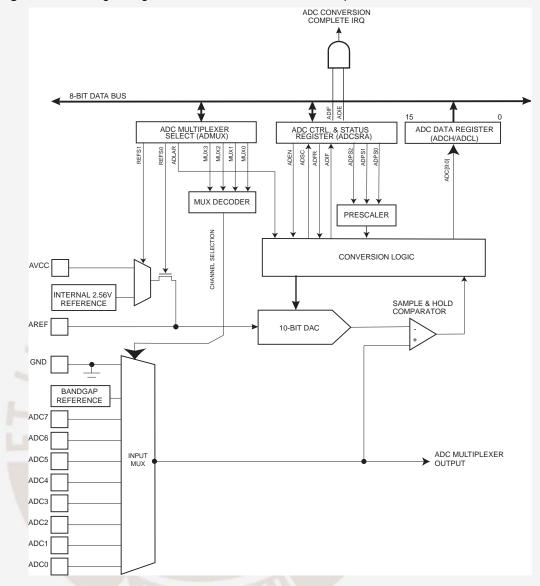

- 8-channel ADC in TQFP and QFN/MLF package Eight Channels 10-bit Accuracy

- 6-channel ADC in PDIP package Six Channels 10-bit Accuracy

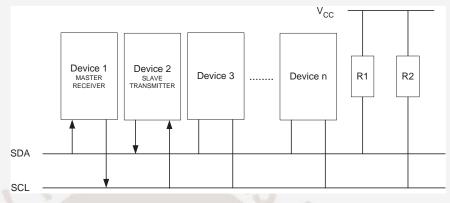

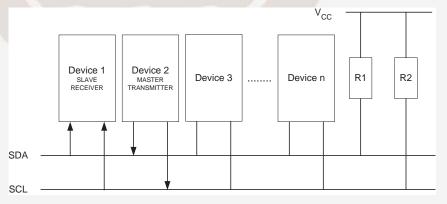

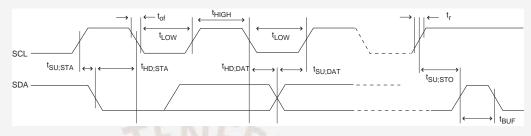

- Byte-oriented Two-wire Serial Interface

- Programmable Serial USART

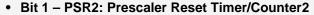

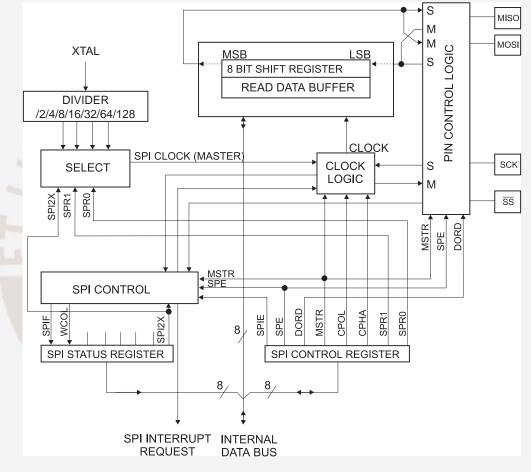

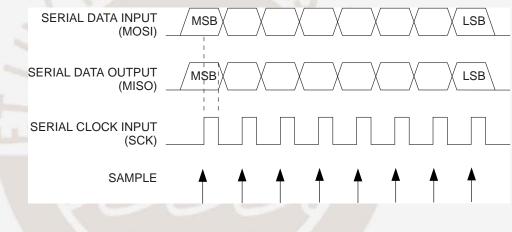

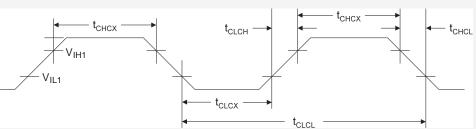

- Master/Slave SPI Serial Interface

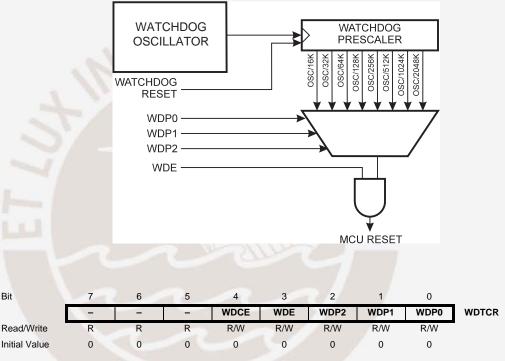

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

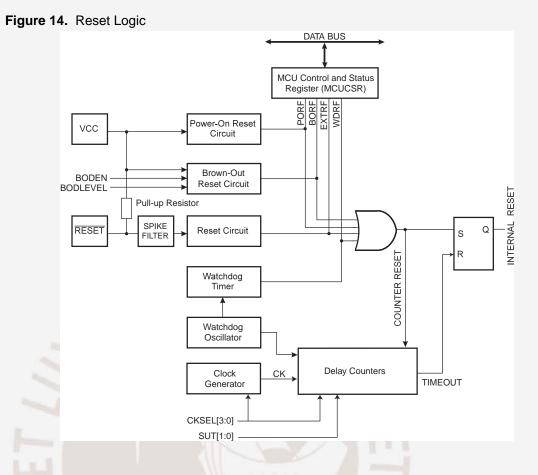

- Power-on Reset and Programmable Brown-out Detection

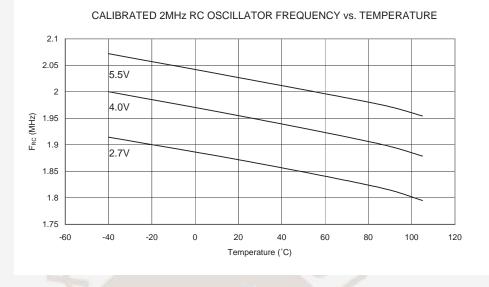

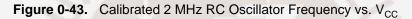

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Five Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, and

- Standby

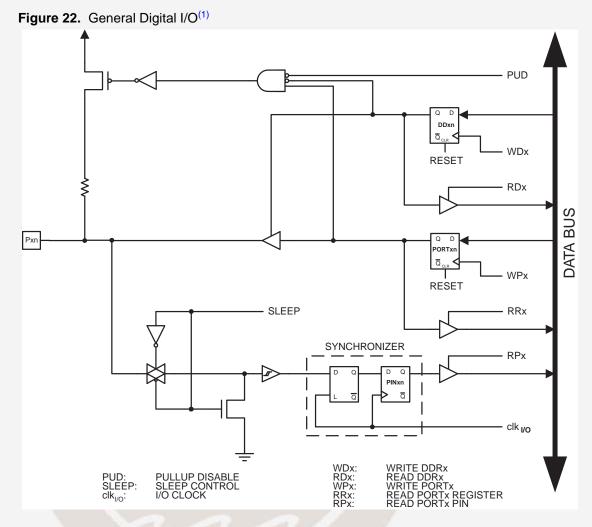

- I/O and Packages

- 23 Programmable I/O Lines

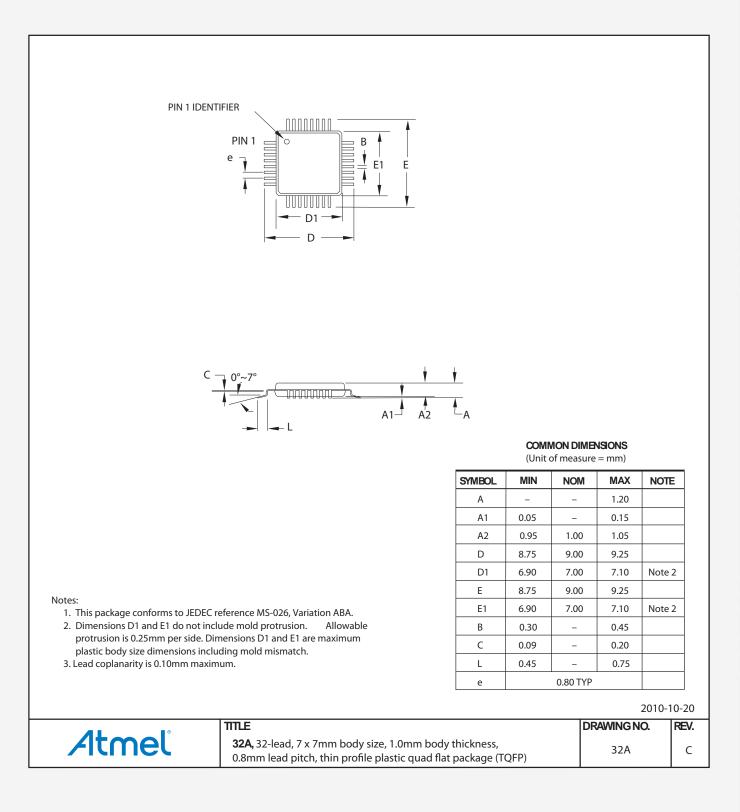

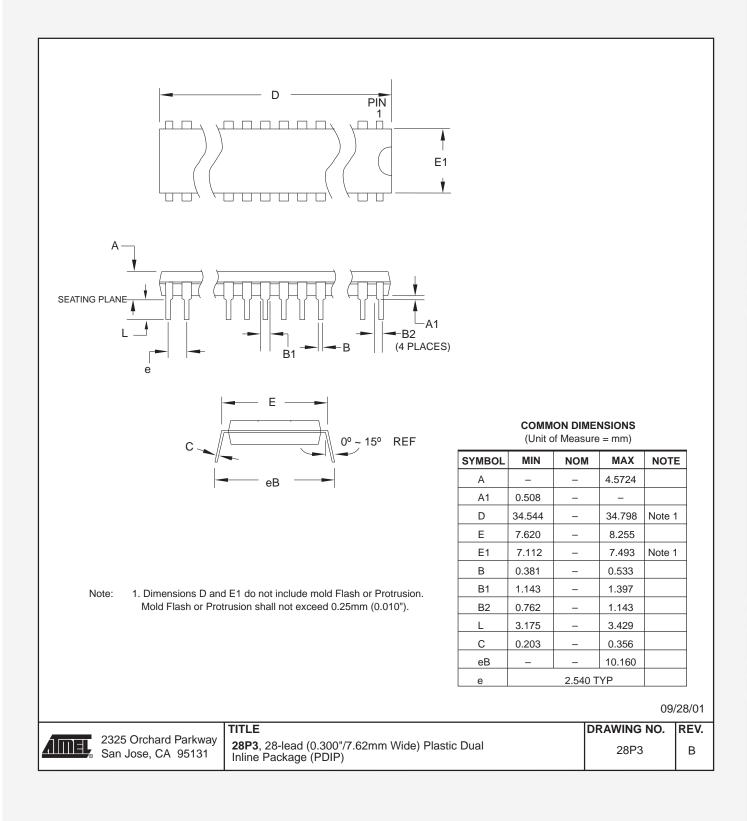

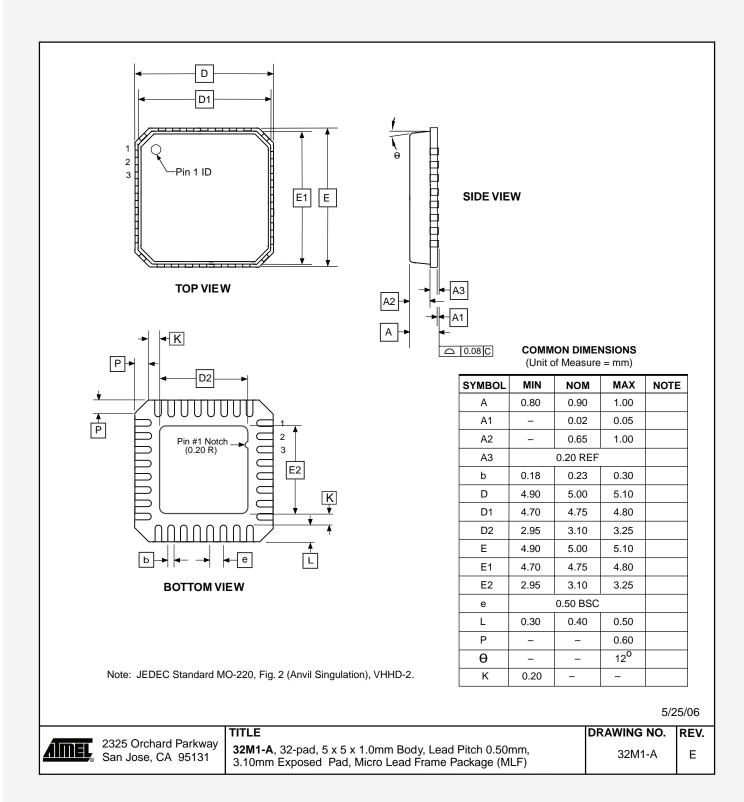

- 28-lead PDIP, 32-lead TQFP, and 32-pad QFN/MLF

- Operating Voltages

- 2.7V 5.5V (ATmega8L)

- 4.5V 5.5V (ATmega8)

- Speed Grades

- 0 8MHz (ATmega8L)

- 0 16MHz (ATmega8)

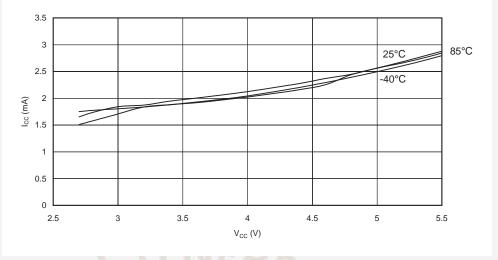

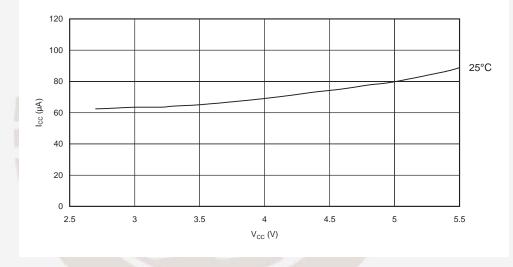

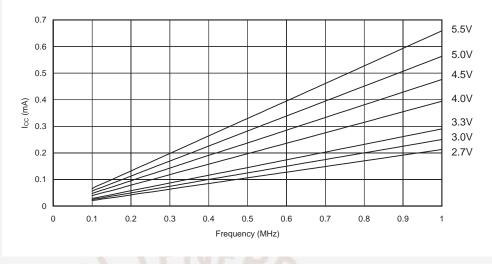

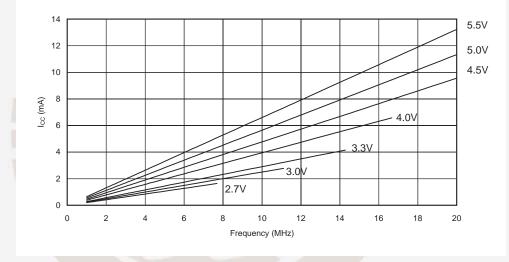

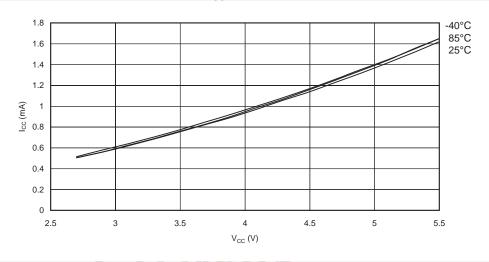

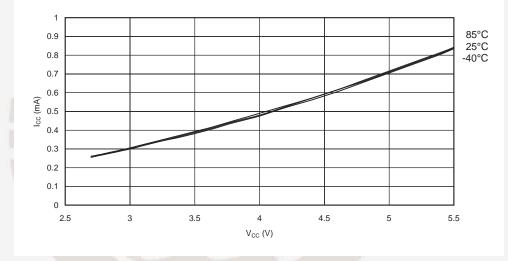

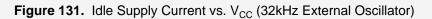

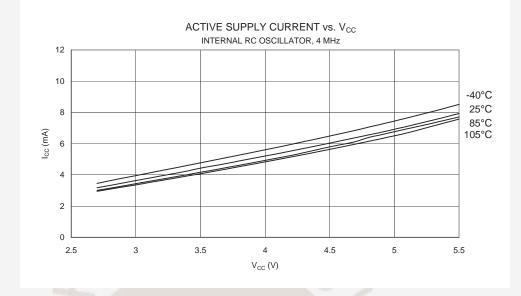

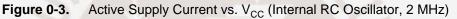

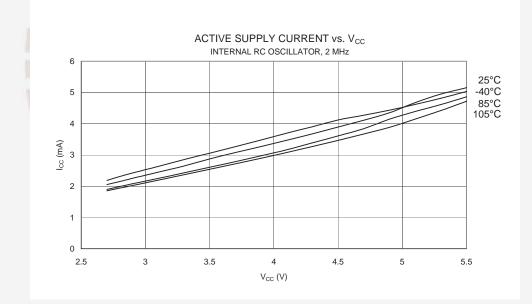

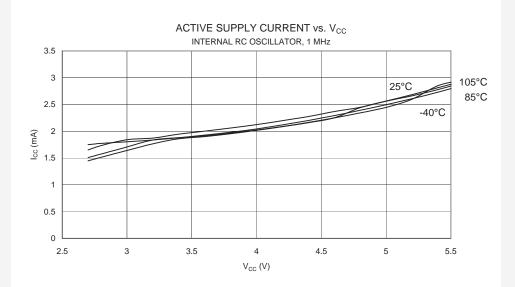

- Power Consumption at 4Mhz, 3V, 25°C

- Active: 3.6mA

- Idle Mode: 1.0mA

- Power-down Mode: 0.5µA

Atmel

8-bit Atmel with **8KBytes In-System** Programmable Flash

ATmega8 ATmega8L

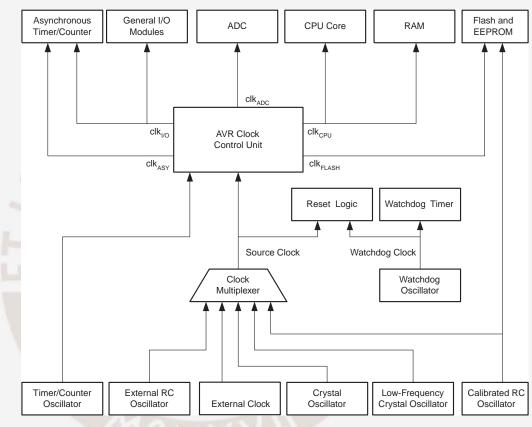

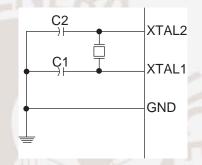

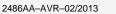

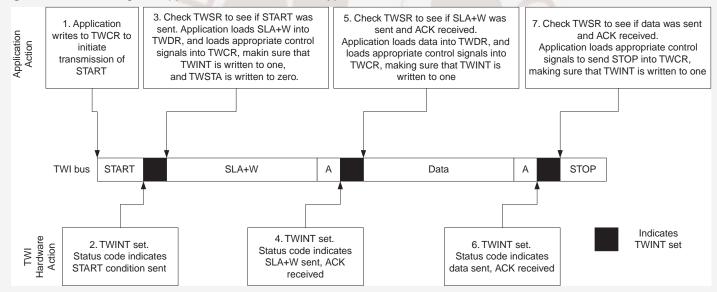

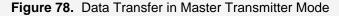

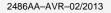

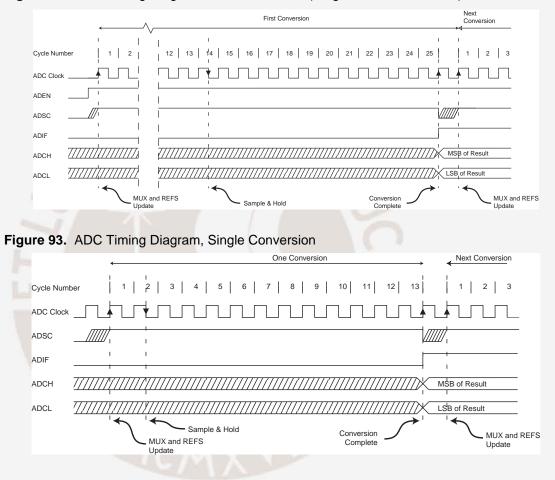

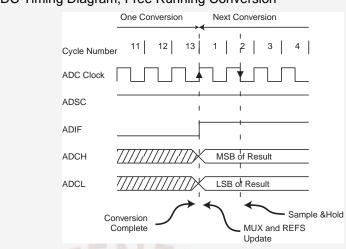

Rev.2486AA-AVR-02/2013

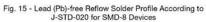

### Pin Configurations

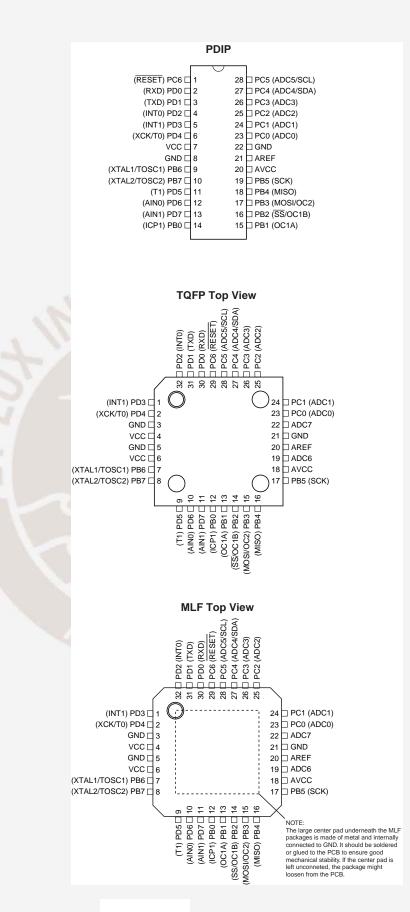

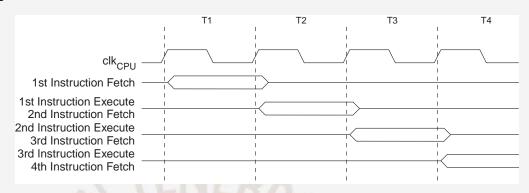

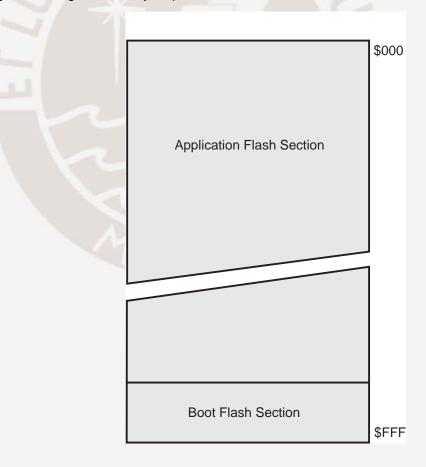

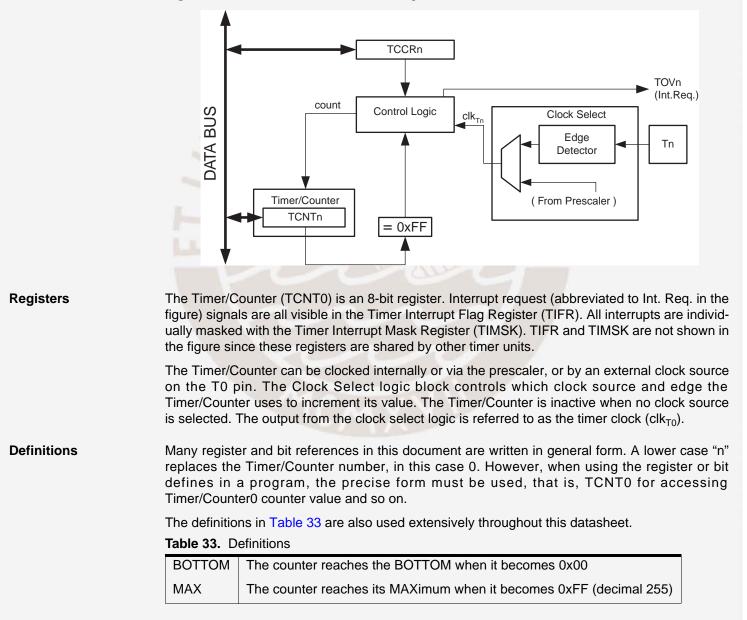

**Overview** The Atmel<sup>®</sup>AVR<sup>®</sup> ATmega8 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega8 achieves throughputs approaching 1MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed.

The Atmel<sup>®</sup>AVR<sup>®</sup> core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

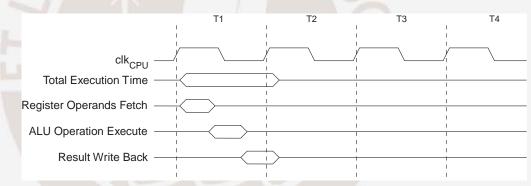

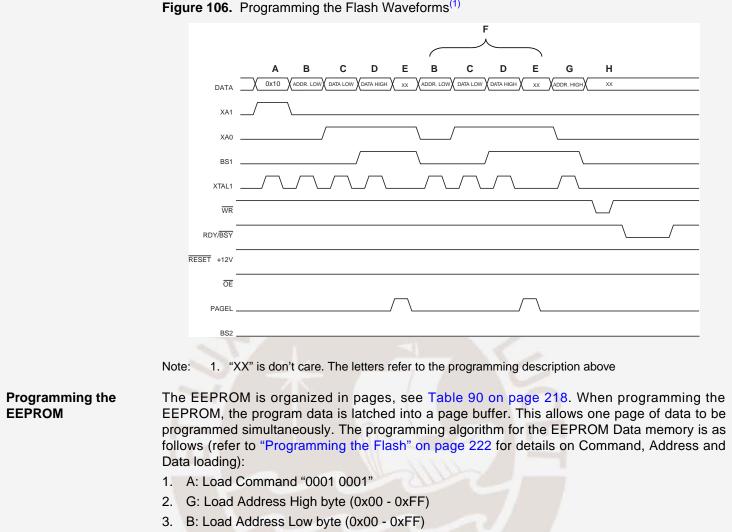

The ATmega8 provides the following features: 8 Kbytes of In-System Programmable Flash with Read-While-Write capabilities, 512 bytes of EEPROM, 1 Kbyte of SRAM, 23 general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, a 6-channel ADC (eight channels in TQFP and QFN/MLF packages) with 10-bit accuracy, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and five software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Powerdown mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next Interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption.

The device is manufactured using Atmel's high density non-volatile memory technology. The Flash Program memory can be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash Section will continue to run while the Application Flash Section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega8 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega8 is supported with a full suite of program and system development tools, including C compilers, macro assemblers, program simulators, and evaluation kits.

**Disclaimer** Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Minimum and Maximum values will be available after the device is characterized.

Atmel

### **Pin Descriptions**

|  | VCC | Digital supply voltage. |

|--|-----|-------------------------|

|--|-----|-------------------------|

Ground.

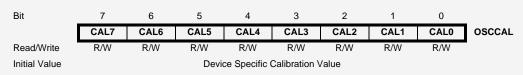

GND