### PONTIFICIA UNIVERSIDAD CATÓLICA DEL PERÚ

Esta obra ha sido publicada bajo la licencia Creative Commons

Reconocimiento-No comercial-Compartir bajo la misma licencia 2.5 Perú.

Para ver una copia de dicha licencia, visite

http://creativecommons.org/licenses/by-nc-sa/2.5/pe/

### PONTIFICIA UNIVERSIDAD CATÓLICA DEL PERÚ FACULTAD DE CIENCIAS E INGENIERÍA

# DISEÑO DE UNA ARQUITECTURA PARA UNA RED NEURONAL ARTIFICIAL PERCEPTRON MULTICAPA SOBRE UN FPGA APLICADA AL RECONOCIMIENTO DE CARACTERES

Tesis para optar el Título de Ingeniero Electrónico

Presentado por:

MANUEL ALEJANDRO MONGE OSORIO

Lima - PERÚ 2008

#### **RESUMEN**

El presente trabajo realizó el diseño genérico y modular de una red neuronal artificial perceptron multicapa MLP orientada al reconocimiento de dígitos manuscritos en un FPGA mediante el lenguaje de descripción de hardware VHDL. El entrenamiento de esta red se realizó externo al chip, en software, mediante la herramienta de Redes Neuronales del Matlab 7.1 y utilizando como imágenes de entrenamiento la base de datos modificada del NIST (MNIST database). Con esto, se logra que el FPGA se dedique solamente a la tarea de reconocimiento, mas no al aprendizaje de la red. Si se quisiera que se cumpla con otra aplicación, bastará con su re-entrenamiento en software para obtener los parámetros necesarios e introducirlos en su descripción y configuración.

Según esto, el diseño se desarrolló en tres partes. La primera muestra el proceso seguido para encontrar los parámetros requeridos por la red neuronal, como son sus dimensiones, pesos sinápticos y umbrales. La segunda consiste en el diseño de la neurona artificial, bloque fundamental de la red y en la cual, debido a la importancia de los decimales y a la presencia de valores elevados en los pesos sinápticos, se trabajó separando las partes enteras y decimales. De esta manera se reducen las dimensiones de los multiplicadores, factor importante en el desempeño. Finalmente, la tercera muestra la arquitectura de una capa neuronal y las consideraciones a tener en cuenta para realizar la unión entre los datos de entrada y las neuronas componentes de la capa. También, se desarrollaron bloques adicionales para que la red neuronal pueda interactuar con la imagen de entrada y para que el resultado obtenido sea codificado y validado.

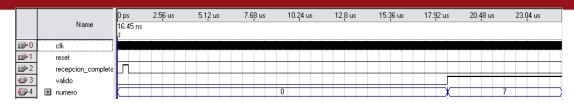

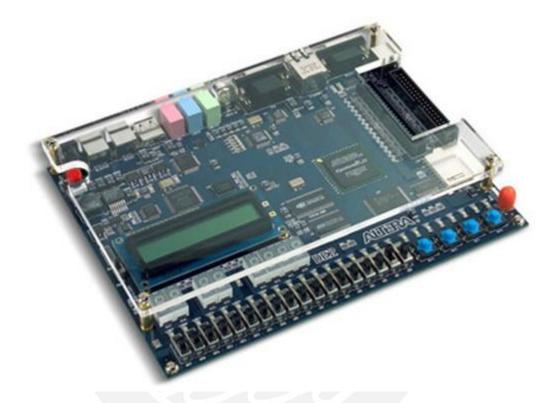

La red neuronal fue implementada en la tarjeta de desarrollo DE2 basada en el FPGA Cyclone II EP2C35F672C6 de Altera con una frecuencia de 50 MHz. En esta etapa se utilizaron las herramientas disponibles en el Quartus II v. 7.1., así como el Signal Tap II Logic Analyzer. Se obtuvo que el tiempo requerido para reconocer un dígito es 18.26us y que de este tiempo, tan solo 2.04us son utilizados por la red neuronal. En comparación con los 7.089ms que demora una aplicación en Matlab 7.1, podemos observar la principal ventaja presente en las implementaciones en hardware de las redes neuronales.

A Margarita... mi madre... y más que una madre.

A Jesús Alberto y Jesús Augusto... grandes hermanos.

A mis incondicionales Cynthia, Lucía, Romina, Michael, Marcelo, Alonso... amigos como pocos.

A mi asesor Dr. Carlos Silva, por toda la confianza y todo el apoyo mostrado.

A mi querido Grupo de Microelectrónica (GuE), por haberme permitido descubrir mi verdadera vocación.

A Julio César Saldaña, Mario Raffo, Jorge Luis Lagos, Gerard Santillán, Walter Calienes, Héctor Villacorta, Heiner Alarcón, Erick Raygada, Jorge Lucio Tonfat, Joel Muñoz, Jorge Benavides, José Daniel Alcántara, José Francisco Quenta; por todos los consejos y enseñanzas, por todo el apoyo, paciencia y sincera amistad.

A mis profesores... por todos sus consejos y enseñanzas.

A todos... Gracias!

"Caminante, son tus huellas el camino y nada más;

el camino y nada mas; caminante, no hay camino, se hace camino al andar.

Al andar se hace camino y al volver la vista atrás se ve la senda que nunca se ha de volver a pisar.

Caminante no hay camino sino estelas en el mar..."

Antonio Machado

#### <u>ÍNDICE</u>

| INTRODUCCION                                             | 1  |

|----------------------------------------------------------|----|

| CAPÍTULO 1                                               |    |

| ASPECTOS GENERALES SOBRE LA IMPLEMENTACIÓN DE REDES      |    |

| NEURONALES                                               | 2  |

| 1.1.PROCESOS Y PROBLEMAS DE ELEVADA COMPLEJIDAD          | 2  |

| 1.1.1.Utilización y aplicaciones de las Redes Neuronales | 2  |

| 1.2.IMPLEMENTACIONES DE LAS REDES NEURONALES             | 3  |

| 1.2.1.Implementación en Hardware                         | 3  |

| 1.2.2.Implementación en Software                         | 4  |

| CAPÍTULO 2                                               |    |

| REDES NEURONALES Y SU IMPLEMENTACIÓN EN HARDWARE         | 5  |

| 2.1.ESTADO DEL ARTE                                      |    |

| 2.1.1.Presentación del asunto de estudio                 | 5  |

| 2.1.2.Estado de la investigación                         | 6  |

| 2.1.3.Síntesis sobre el asunto de estudio                | 11 |

| 2.2.RECONOCIMIENTO DEL CARÁCTER DENTRO DE UN OCR         |    |

| 2.3.Redes Neuronales                                     |    |

| 2.3.1.Redes Multicapa                                    | 13 |

| 2.3.2.Red Perceptron Multicapa (MLP)                     |    |

| 2.3.3.Paradigmas de Aprendizaje                          |    |

| 2.3.4.Aprendizaje Error-Corrección                       | 16 |

| 2.3.5.Algoritmo Backpropagation                          | 16 |

| 2.4.DISPOSITIVO LÓGICO PROGRAMABLE FPGA                  | 16 |

| 2.4.1.Arquitectura genérica                              | 17 |

| 2.4.2.Arquitectura del FPGA CYCLONE II de ALTERA         | 18 |

| 2.5.LENGUAJE DE DESCRIPCIÓN DE HARDWARE VHDL             | 19 |

| 2.6.MODELO TEÓRICO                                       | 20 |

| 2.6.1.Definiciones Operativas                            | 20 |

#### **CAPÍTULO 3**

| PLANTEAMIENTOS PARA EL DISEÑO DE LA RED NEURONAL PERCEP                 | TRON |

|-------------------------------------------------------------------------|------|

| MULTICAPA                                                               | 23   |

| 3.1.HIPÓTESIS DE LA INVESTIGACIÓN                                       | 23   |

| 3.1.1.Hipótesis principal                                               | 23   |

| 3.1.2.Hipótesis secundarias                                             | 23   |

| 3.2.OBJETIVOS DE LA INVESTIGACIÓN                                       | 24   |

| 3.2.1.Objetivo general                                                  | 24   |

| 3.2.2.Objetivos específicos                                             | 24   |

| 3.3.METODOLOGÍA DE LA INVESTIGACIÓN                                     | 25   |

| 3.4.ANÁLISIS DEL SISTEMA Y DETERMINACIÓN DE REQUERIMIENTOS              |      |

| 3.5.CONSIDERACIONES PARA EL DISEÑO                                      | 29   |

| CAPÍTULO 4                                                              |      |

| DISEÑO DE LA ARQUITECTURA PARA LA RED NEURONAL PERCEPTR                 |      |

| MULTICAPA                                                               | 32   |

| 4.1.DISEÑO DE LA RED NEURONAL MEDIANTE SOFTWARE                         |      |

| 4.1.1.Desarrollo y entrenamiento de la red neuronal                     | 33   |

| 4.1.2.Pruebas y validación de la red neuronal.                          | 43   |

| 4.1.3.Extracción de los pesos sinápticos y umbrales                     | 46   |

| 4.2.DISEÑO DE LA RED NEURONAL SOBRE EL FPGA CYLONE II DE ALTERA         | 47   |

| 4.2.1.Descripción y diseño de la arquitectura de una Neurona Artificial | 49   |

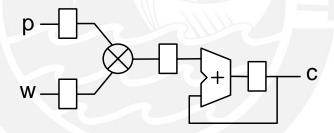

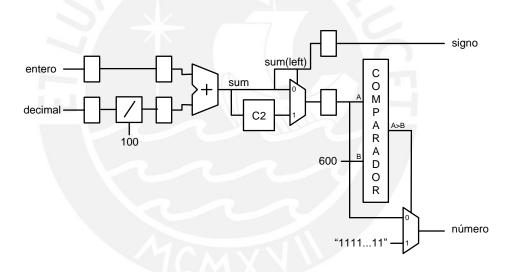

| 4.2.1.1.Multiplicador-Acumulador                                        | 51   |

| 4.2.1.2.Bloque Convierte                                                | 52   |

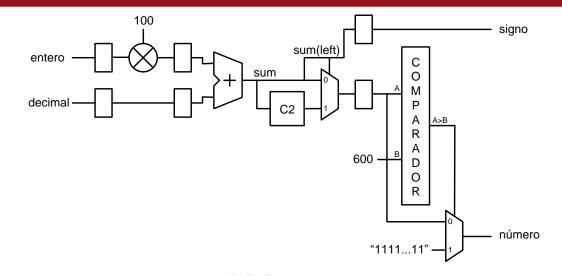

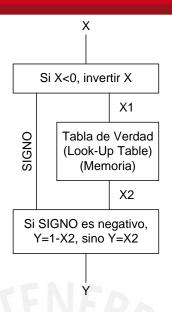

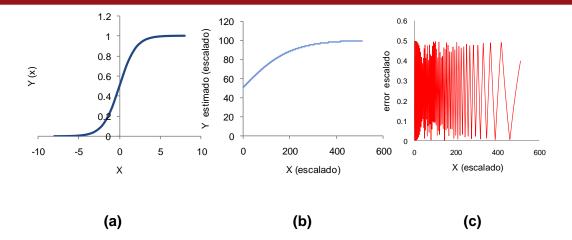

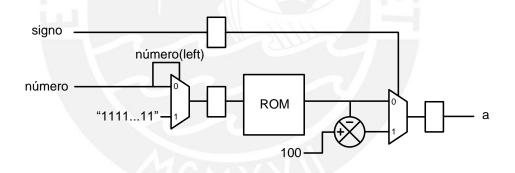

| 4.2.1.3.Función Sigmoide                                                | 53   |

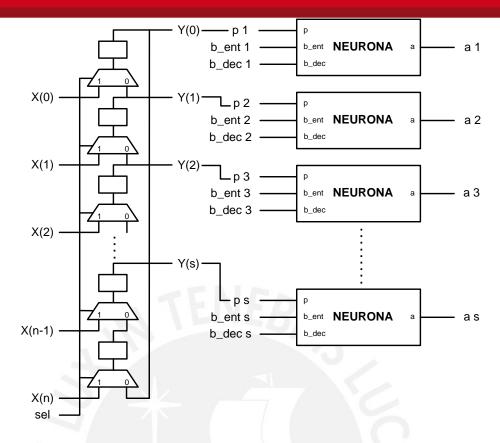

| 4.2.2.Descripción de la arquitectura de la red neuronal                 | 55   |

| 4.2.2.1.Capa Neuronal                                                   | 56   |

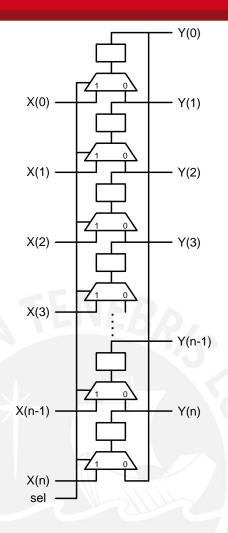

| 4.2.2.2.Registro de Desplazamiento Circular                             | 57   |

| 4.2.2.3.Bloque Convierte2                                               |      |

| 4.2.2.4.Controlador                                                     | 59   |

| 4.2.3. Diseño en VHDL de la arquitectura de la red neuronal             | 61   |

#### **CAPITULO 5**

| SIMULACIONES Y RESULTADOS                                         | 64 |

|-------------------------------------------------------------------|----|

| 5.1.DISEÑO Y DESARROLLO DE COMPONENTES Y HERRAMIENTAS ADICIONALES | 64 |

| 5.1.1.Etapa de pre-procesamiento                                  | 65 |

| 5.1.2.Etapa de post-procesamiento                                 | 66 |

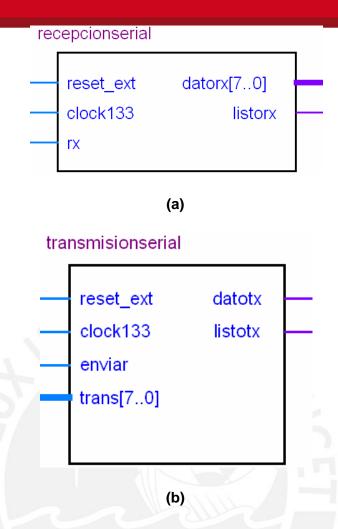

| 5.1.3.Interfaz serial FPGA-PC                                     | 67 |

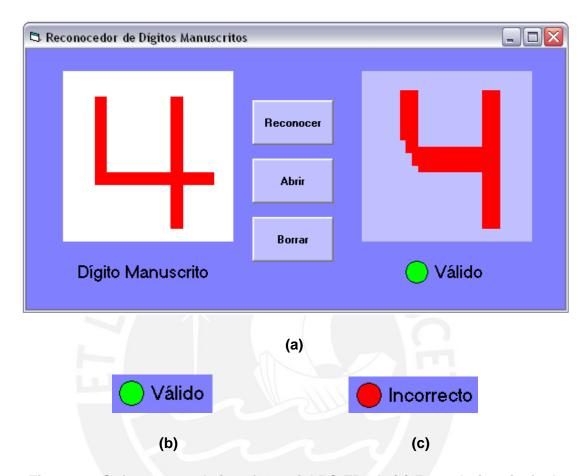

| 5.1.4.Software para la interacción con la red neuronal            | 69 |

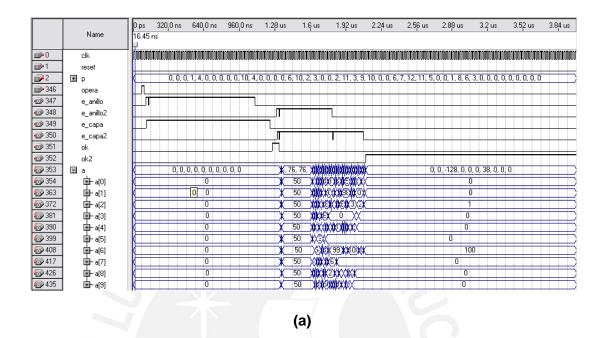

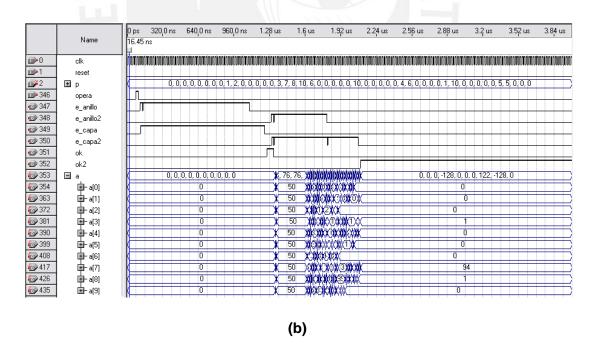

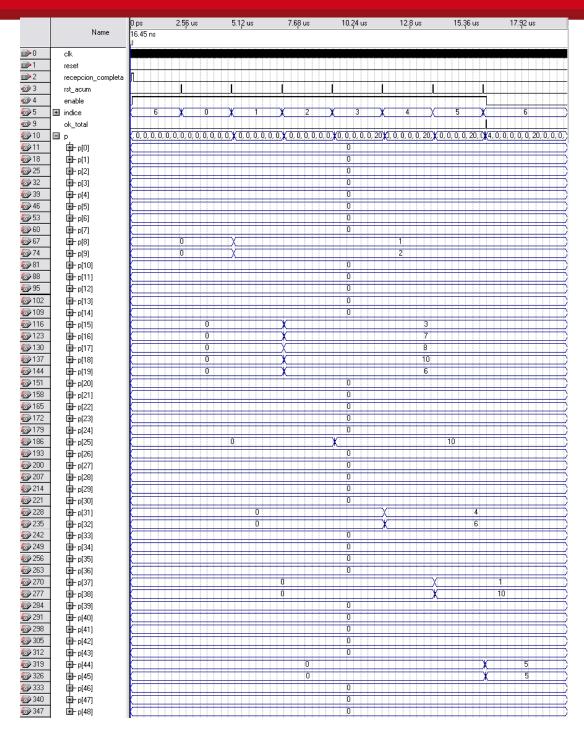

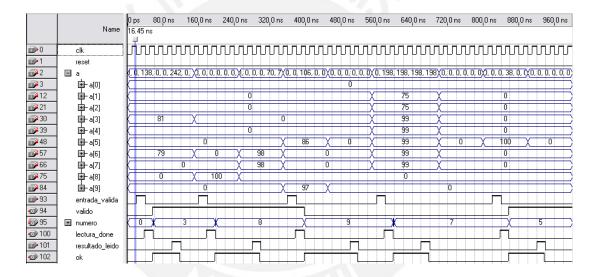

| 5.2.SIMULACIONES                                                  | 71 |

| 5.3.Resultados                                                    | 75 |

| CONCLUSIONES                                                      | 79 |

| RECOMENDACIONES                                                   | 81 |

| BIBLIOGRAFIA                                                      | 82 |

| ANEXOS                                                            |    |

#### INTRODUCCIÓN

Las redes neuronales son una teoría de procesamiento de información perteneciente a la inteligencia artificial que busca emular el comportamiento del sistema nervioso en el procesamiento de la información. Se basa en las múltiples interconexiones que se generan entre sus elementos básicos, denominados neuronas. De esta forma, según esta interacción pueden formar diferentes tipos de arreglos para cumplir una tarea específica.

Así, en la actualidad son utilizadas en muchas áreas debido a su gran flexibilidad y variedad de aplicaciones que presentan. Si bien la mayoría de estas se realizan en software, la importancia y vigencia de las implementaciones en hardware se mantiene y radica en aprovechar mejor las ventajas propias de las redes neuronales y en que son usadas en aplicaciones que requieren un alto desempeño.

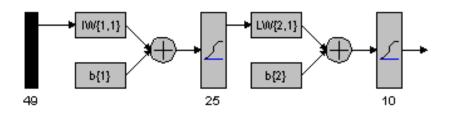

El presente trabajo muestra el desarrollo en hardware de una red neuronal artificial perceptron multicapa (MLP) aplicada al reconocimiento de dígitos manuscritos. La red MLP 49-25-10 fue entrenada en software con la herramienta de redes neuronales del Matlab (Neural Networks Toolbox). Para este proceso se utilizó la base de datos modificada del NIST (MNIST) que cuenta con 60000 imágenes binarias representativas de dígitos manuscritos de 28x28 pixeles, las que son umbralizadas antes de la entrada a la red neuronal.

Teniendo en cuenta estas dimensiones de la red, se diseña la arquitectura combinando el planteamiento expuesto por Volnei A. Pedroni con la idea propia de separar las partes enteras y decimales de los pesos sinápticos y umbrales encontrados en el entrenamiento. De esta forma se puede tener mayor exactitud con los decimales y mayor facilidad para realizar escalamientos si se tiene magnitudes muy elevadas en la parte entera.

Así, el diseño se realiza de manera modular y genérica para que pudiese ser adaptado fácilmente a un nuevo requerimiento con un re-entrenamiento de la red en software, extracción de los parámetros necesarios para el sistema e ingreso de los mismos en la descripción del circuito para su posterior síntesis e implementación en el FPGA. Adicionalmente, se pretende que esta arquitectura de propósito general sirva de base para futuras investigaciones y trabajos en el tema. De esta forma estaremos contribuyendo con la difusión de estas técnicas en nuestra industria.

#### **CAPÍTULO 1**

## ASPECTOS GENERALES SOBRE LA IMPLEMENTACIÓN DE REDES NEURONALES

#### 1.1. Procesos y problemas de elevada complejidad

En la actualidad, los nuevos requerimientos de la sociedad en función de sus nuevas necesidades de tratamiento de información y cómputo, no son cubiertos a cabalidad por los computadores vigentes. Incluso no son lo suficientemente eficaces para resolver tareas comunes de la actividad humana, pese al avance tecnológico alcanzado y a su continuo desarrollo.

Sin embargo, gracias a este avance de la tecnología y a la atmósfera de necesidad generada se han desarrollado nuevas teorías de procesamiento y se han retomado algunas ya estudiadas, las cuales resuelven dichos inconvenientes mediante la aplicación de nuevos algoritmos y nuevos paradigmas. Dentro de ellas se encuentran las Redes Neuronales, las cuales presentan un gran número de aplicaciones a través de su implementación tanto en hardware como en software.

Asimismo, es conveniente aplicar dichas tecnologías en nuestro país, para que de esta forma podamos contribuir en su desarrollo y modernización.

#### 1.1.1. Utilización y aplicaciones de las Redes Neuronales

Las redes neuronales son utilizadas para el procesamiento de señales, reconocimiento y clasificación de patrones, síntesis y reconocimiento de voz, control de procesos y equipos, predicción, aproximación, direccionamiento, en el campo de la medicina, los negocios, en el ámbito industrial, social y científico. Algunas aplicaciones son los sistemas de control, sistemas de predicción, sistemas de seguridad, identificación, videoconferencia, procesamiento de documentos, reconocimiento de patrones como voz, caracteres, objetos.

La potencialidad presente en las redes neuronales y la existencia de un mercado y de clientes por satisfacer, debido a las necesidades actuales, genera una sostenibilidad económica que permite la implementación de las aplicaciones teniendo en cuenta su costo de inversión tecnológica.

#### 1.2. Implementaciones de las redes neuronales

Las redes neuronales se implementan tanto en hardware como en software. Ambos tipos de desarrollo presentan un campo de acción definido, el cual depende de los requerimientos específicos de la aplicación; por lo cual, ella debe ser analizada para realizar una correcta elección. Un análisis costo-beneficio también debe llevarse a cabo para contar con una visión global de la aplicación.

Sin embargo, y pese a que la mayoría de implementaciones se realizan en software, la importancia y vigencia de la implementación en hardware se mantiene y radica en aprovechar mejor las ventajas propias de las redes neuronales, y en que sus aplicaciones necesitan de un elevado desempeño, y características inherentes al desarrollo en hardware, que no presenta la implementación en software [1] [2].

#### 1.2.1. Implementación en Hardware

Si bien la implementación de redes neuronales en software se esta convirtiendo en la más apropiada y utilizada para la resolución de aplicaciones reales (real-world applications), las implementaciones sobre hardware siguen siendo esenciales e importantes debido a que permiten un procesamiento en tiempo real y que son utilizadas en pequeñas áreas específicas donde un muy alto rendimiento es requerido (por ejemplo: física de alta energía), en aplicaciones embebidas de redes simples (por ejemplo: chips de reconocimiento de voz), y en sistemas neuromórficos, los cuales implementan directamente una función deseada (por ejemplo: touchpad y silicon retinas)[1], aprovechando al máximo las ventajas inherentes del paralelismo masivo de las redes neuronales.

Sin embargo, la implementación en hardware de redes neuronales es aun un tema abierto a investigación, pues se debe optimizar la relación entre su eficiencia y exactitud, y el área utilizada en el chip [3]. De esta forma, su etapa de diseño no se encuentra completamente desarrollada y provoca deficiencias en comparación a la implementación en software.

Cabe mencionar que las limitaciones propias del software y la aparición de dispositivos lógicos programables más capaces vuelven necesarias a las implementaciones en hardware pese a sus propias limitaciones como son un mayor costo, mayor tiempo de diseño y mayor tiempo de puesta en el mercado (time-to-market).

#### 1.2.2. Implementación en Software

Como ya mencionamos, las implementaciones en software vienen ganando aceptación debido a sus ventajas sobre las implementaciones en hardware en aplicaciones reales, como por ejemplo el reconocimiento de caracteres dentro de un sistema de restauración de libros o dentro de un sistema en el cual se cuenta con un computador que realiza distintas labores no críticas. Otra aplicación se da en el campo de control de procesos, o en las predicciones y aproximaciones, donde el tiempo de procesamiento no es un requerimiento del sistema. También se aprecia en el campo de la medicina, donde se utiliza como ayuda para el diagnóstico de enfermedades debido a su capacidad de detectar y clasificar patrones (señales del electroencefalograma o electrocardiograma, o diagnóstico por imágenes). En todos estos casos, las aplicaciones se realizan sobre software en un computador [1].

Dentro de las ventajas que presenta se encuentran las herramientas de diseño (Toolbox) y contar con herramientas de programación de alto nivel, que permiten un diseño en menor tiempo. Sin embargo, presenta limitaciones debido a que recarga al procesador (CPU) en una sola aplicación que le lleva "mucho tiempo", pues tareas como clasificación y localización son de alto consumo de procesador; lo cual disminuye el desempeño global del sistema completo. Además, según la aplicación, no permite aplicaciones en tiempo real; pues la mayoría se realizan en hardware porque aprovechan mejor todas las ventajas de las redes neuronales [2].

#### **CAPÍTULO 2**

#### REDES NEURONALES Y SU IMPLEMENTACIÓN EN HARDWARE

#### 2.1. Estado del arte

#### 2.1.1. Presentación del asunto de estudio

Las nuevas teorías de procesamiento de información buscan cubrir las carencias que muestran los sistemas actuales de cómputo en la resolución de diversos problemas, los cuales son cada vez más complejos y sofisticados, debido a la gran cantidad de variables que deben manejar y a la dificultad intrínseca del problema. La inteligencia artificial es un claro ejemplo de esto, y de cómo dichas teorías van desplazando a las actuales pues presentan una mejor eficacia en estos campos.

Dentro de este grupo, se encuentran las redes neuronales artificiales, las cuales pretenden emular el comportamiento del cerebro en el procesamiento de información. Estas redes se conforman de varios elementos de procesamiento simples llamados neuronas, quienes se encuentran conectadas entre sí y procesan la información con un paralelismo masivo, logrando resolver varios y diversos problemas en distintas aplicaciones de diferentes áreas.

Para tal fin, las redes neuronales son implementadas tanto en software como en hardware según la aplicación. De esta forma, si es una actividad estática, se cuenta con un computador y el tiempo de procesamiento no es crítico, una aplicación en software será la adecuada; mientras que si se requiere un procesamiento veloz o en tiempo real, se necesita de un equipo portátil, ligero y de pequeñas dimensiones, una implementación en hardware es la mejor opción.

Según esto, el desarrollo de redes neuronales implementadas en hardware presenta un amplio campo de acción tanto a nivel industrial como comercial. La gran diversidad de aplicaciones hace indispensable contar con una arquitectura base, con la cual sea factible realizar posteriores trabajos de investigación para aplicaciones específicas.

Por lo tanto, el presente estudio busca el diseño de una arquitectura de una red neuronal, la cual será la base de posteriores desarrollos en el mismo campo y en el campo de los sistemas neuromórficos. Según dichos requerimientos, la arquitectura debe estar realizada en base a módulos y además debe tener diversas aplicaciones. De esta forma, se diseñará una arquitectura de una red neuronal conocida como Perceptron Multicapa o "Multi-Layer Perceptron" y, para probar su

correcto funcionamiento, se escogió una de sus principales aplicaciones, y que además se encuentra muy difundida, como es la etapa de reconocimiento del carácter de un sistema de reconocimiento óptico de caracteres o "Optical Character Recognition" (OCR).

#### 2.1.2. Estado de la investigación

Para el proceso especifico del reconocimiento del carácter, dentro de las implementaciones hechas en hardware, existen diversas formas y métodos para su realización. Esto se debe también a la diversidad de la tecnología actual y a su continuo avance, lo cual permite el desarrollo de teorías ya existentes y de nuevas formas de procesamiento.

Entre estas podemos mencionar las redes neuronales, las cadenas ocultas de Markov, el voto mayoritario, sistemas basados en microprocesadores, transformada de Fourier, transformada de wavelet, métodos estadísticos de Bayes, árboles de decisión, lógica difusa, algoritmos genéticos, etc. Dentro de las cuales, destaca en este campo la implementación del sistema mediante redes neuronales, pues presentan un mejor desempeño, logrando tasas de éxito superiores al 99% para caracteres impresos [4], y capacidades de aprendizaje y adaptación. Por estas razones es el método más utilizado en la actualidad, encontrándose tanto en dispositivos específicos como en programas para el reconocimiento de caracteres.

La razón por la cual se desarrolla este modelo es por la poca eficiencia de los métodos tradicionales de procesamiento para resolver las tareas comunes de la actividad humana, pese a contar con una mayor capacidad que el cerebro humano [5]. Las neuronas, a pesar de ser mucho más lentas que las compuertas lógicas (pues los eventos en un chip ocurren en el orden de nanosegundos; mientras que los neuronales en milisegundos), procesan mejor la información y en mucho menor tiempo [6]. Esto lo logran debido al gran número de interconexiones o sinapsis que existen entre ellas mismas. Según esto, las Redes Neuronales Artificiales (ANN: Artificial Neural Networks) o simplemente Redes Neuronales (NN: Neural Networks) buscan modelar el comportamiento del sistema nervioso biológico a partir del conocimiento del mismo y de la biología de la neurona; utilizando sus respectivos modelos matemáticos.

Así, las redes neuronales son un procesador distribuido masivamente en paralelo que tiene la tendencia natural de almacenar conocimiento de forma experimental y

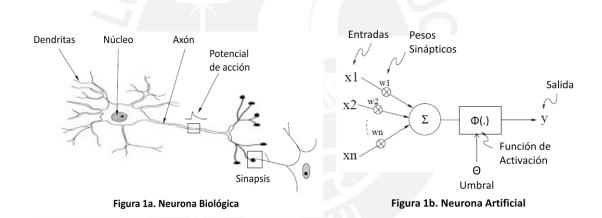

volverla disponible para su uso [7]. Su unidad de procesamiento de información es la neurona, la cual es fundamental para el funcionamiento de la red. Consta de las siguientes partes:

- Sinapsis o interconexiones, cada una caracterizada por un "peso sináptico" o fuerza de conexión. Dicho peso será positivo si la sinapsis es excitadora y será negativo si es inhibidora.

- Un sumador para sumar las señales entrantes multiplicadas por sus respectivos pesos sinápticos.

- Una función de activación, para limitar la amplitud de la salida de la neurona.

La figura 1 muestra las representaciones de una neurona biológica y una neurona artificial.

Figura 1. Neurona biológica y Neurona Artificial [8].

Su utilización satisface las demandas de los sistemas actuales, cuyos procesos son muy complejos y requieren de una mayor eficacia en su resolución. Las características de las redes neuronales que permiten lo dicho anteriormente son las siguientes [5] [6] [9]:

- Estructura distribuida masivamente paralela.

- Habilidad de aprendizaje.

- Habilidad de generalización.

#### **TESIS PUCP**

- No linealidad.

- Mapeo entre entrada-salida.

- Adaptabilidad.

- Procesamiento de información local.

- Respuesta de confiabilidad.

- Información contextual.

- Memoria distribuida.

- Memoria a largo plazo se encuentra en los pesos sinápticos.

- Memoria a corto plazo corresponde a las señales enviadas por las neuronas.

- La fuerza de la sinapsis puede ser modificada por la experiencia.

- Los neurotransmisores pueden ser excitadores o inhibidores.

- Tolerancia a fallas.

- Capacidad de implementación VLSI.

- Uniformidad de análisis y diseño.

- Analogía neurobiológica.

Estas ventajas son aprovechadas en su mayoría por los sistemas actuales y son el motivo principal por la cual se prefieren frente a los métodos de procesamiento tradicionales. Por esto, las aplicaciones y usos de las redes neuronales son muy diversas y se encuentran en varios campos como son la robótica, control, reconocimiento de patrones, medicina, síntesis de voz, reconocimiento de voz, aproximación de funciones, predicción, optimización, reconstrucción de patrones, negocios y el entendimiento del procesamiento del cerebro humano [5][9][10].

El reconocimiento de caracteres es un caso particular del reconocimiento de patrones, razón por la cual dichas redes neuronales son capaces de realizar dicha labor; y, como ya mencionamos, son las más utilizadas debido a su gran eficiencia

#### **TESIS PUCP**

y confiabilidad. En este tipo de tarea, se tiene un número fijo de categorías o clases dentro de las cuales las muestras deben ser clasificadas. De esta forma, la ventaja que presenta este método reside en el hecho que se pueden separar regiones no lineales de decisión tan complicadas como se requiera dependiendo del número de neuronas y/o de la cantidad de capas [7].

Las arquitecturas que realizan dicha tarea son las redes de una sola capa, las redes de múltiples capas o multicapas (MLP: MultiLayer Perceptron), las redes de base radial (RBF: Radial Basis Function network), redes ART (Adaptive Resonance Theory models) y Neocognitron [5] [9]. Sin embargo, la red más utilizada para esta tarea es la MLP, debido a que utiliza el algoritmo de aprendizaje que se encuentra actualmente más extendido, el algoritmo o regla BackPropagation [7].

En cuanto al hardware, las redes neuronales se encuentran implementadas de diversas formas, ya sean analógicas o digitales. En las primeras, se puede citar a los dispositivos analógicos programables, como los FPAA (Field Programmable Analog Array); mientras que en las segundas destacan los dispositivos lógicos programables como los FPGA (Field Programmable Gate Array), donde también se desarrollan los conceptos de FPNA (Field Programmable Neural Array) y FPNN (Field Programmed Neural Network), con los cuales el diseño de redes neurales más complejas se facilita en gran medida [11]. Finalmente, se tiene la tecnología ASIC (Application Specific Integrated Circuit, Circuito Integrado de Aplicación Específica) en donde, ya sea analógico o digital, se obtienen chips con un diseño y aplicación específica; y en este caso, de una red neuronal.

La tabla 1 muestra el compromiso existente entre algunos parámetros del diseño y algunas tecnologías para la implementación de redes neuronales. Observamos que los FPGAs poseen buenas prestaciones en la mayoría de los campos, siendo un dispositivo adecuado para dicha aplicación.

Tabla 1. Dispositivos apropiados/inapropiados para la implementación de redes neuronales [11].

|               | ASIC<br>analógico | ASIC<br>digital | FPGA | Basado en procesador | Computador paralelo |

|---------------|-------------------|-----------------|------|----------------------|---------------------|

| Velocidad     | +++               | ++              | +    | -                    | +                   |

| Área          | +++               | ++              | +    | -                    |                     |

| Costo         |                   |                 | ++   | ++                   |                     |

| Tiempo de     |                   |                 |      |                      |                     |

| Diseño        |                   |                 | ++   | +++                  | +                   |

| Confiabilidad |                   | +               | ++   | ++                   | ++                  |

--: muy desfavorable +: favorable

- : desfavorable ++ : muy favorable

+++: extremadamente favorable

En la actualidad, los FPGAs son muy utilizados en diversas aplicaciones, y también han sido usados para el diseño e implementación de redes neuronales de diversas arquitecturas. La más utilizada es la red multicapa (MLP) y el algoritmo de aprendizaje Backpropagation, por las razones mencionadas previamente y por las características inherentes propias del FPGA y los componentes que presenta; los cuales facilitan su implementación. Así, es utilizado para el reconocimiento de caracteres, dígitos, caras, firmas, etc.

#### 2.1.3. Síntesis sobre el asunto de estudio

Los nuevos requerimientos de los procesos actuales y la incapacidad mostrada por los computadores para resolverlos generan la necesidad de buscar nuevos métodos para el procesamiento de información. Dentro de este ámbito, las Redes Neuronales Artificiales surgen como una alternativa eficaz ante este inconveniente, pues presentan un mejor desempeño en un menor tiempo y una gran variedad de aplicaciones. Para lograr tal fin, dichas redes neuronales deben pasar por un proceso de aprendizaje (entrenamiento) y luego por un proceso de prueba (test) para que finalmente sean colocadas en la aplicación deseada.

Por tal motivo, el presente estudio propone el diseño sobre un FPGA de una arquitectura de una red neuronal para que sea el precedente de posteriores desarrollos tanto en el campo de las redes neuronales como en el campo de los sistemas y circuitos neuromórifcos.

La arquitectura neuronal planteada es el perceptron multicapa, conocido como MLP, debido a que es una red genérica y resuelve un gran número de problemas en diversas áreas. Adicionalmente, para verificar su funcionamiento, será aplicado a la etapa de reconocimiento del carácter de un sistema de reconocimiento óptico de caracteres (OCR).

El diseño se llevará a cabo con el lenguaje de descripción de hardware VHDL (Very High Speed Integrated Circuit Hardware Description Language, Lenguaje de Descripción de Hardware de Circuitos Integrados de Alta Velocidad), el cual permite describir circuitos y sistemas digitales mediante el desarrollo de un código que es transparente frente a las diversas herramientas EDA (Electronic Design Automation). Además, se utilizará un entorno de desarrollo proporcionado por el fabricante que permite la interacción entre el diseñador y el FPGA.

Un punto importante que cabe resaltar es el hecho que el diseño depende del FPGA a utilizar, pues ellos presentan diferentes estructuras, componentes y limitaciones según la familia a la cual pertenezcan y la empresa que los desarrolla. De esta forma, debemos conocer a fondo los recursos que presenta el dispositivo para tenerlos en cuenta durante el desarrollo del diseño.

Finalmente, se obtendrán conclusiones a partir de los resultados obtenidos durante todo el proceso y a la finalización del mismo; los cuales serán útiles para futuros estudios e investigaciones en el mismo campo y en temas relacionados.

#### 2.2. Reconocimiento del carácter dentro de un OCR

Un Reconocedor Óptico de Caracteres OCR (Optical Character Recognition) es un sistema que convierte la imagen de textos escritos o impresos en una forma tal que el computador pueda procesarlos posteriormente. Generalmente, se almacenan como caracteres ASCII dentro de un archivo de texto. Consta, básicamente, de las siguientes etapas: adquisición de la imagen, análisis del formato, segmentación, extracción de características y reconocimiento del carácter [12] [13].

La adquisición de la imagen es el proceso por el cual la imagen del texto es obtenida, por lo que es el punto de inicio de todo el proceso. Generalmente se emplean escáneres, pero también pueden emplearse cámaras [12] [13].

Seguidamente, el análisis del formato consiste en identificar los títulos, subtítulos, columnas, gráficos y formas del documento para realizar una adecuada lectura. De esta forma se evitan resultados erróneos [12] [13].

Posteriormente, la segmentación es el proceso que consiste en la separación o partición de un objeto en varias partes de menor magnitud. En el caso de la separación de caracteres, involucra reconocer los límites entre un carácter y otro y generar una nueva imagen para cada carácter segmentado. En este proceso, puede incluirse una etapa de normalización de la imagen, al poder existir diferencias en los tamaños de los caracteres [12] [13].

Después se prosigue con la extracción de características, la cual consiste en la obtención de parámetros que permitan realizar adecuadamente los respectivos análisis de las imágenes. Una primera tarea es la umbralización, que determina si un punto pertenece o no al carácter; si es así, le asigna un 1 lógico, caso contrario un 0 lógico. Posteriormente, se calcula la altura, el ancho, el área, la relación entre ancho y alto, la orientación; es decir, las características del carácter [12] [13].

Finalmente se realiza el reconocimiento del carácter, que consiste en la clasificación del carácter dentro de las clases posibles que lo definan como tal. En otras palabras, es la etapa que nos dice que carácter es y nos da a la salida dicho carácter en un formato que sea manipulable por la computadora, como es el ASCII [12] [13].

Esta última etapa es una de las más importantes, pues se encarga de realizar la clasificación, y es de quien depende el éxito o fracaso del proceso; convirtiéndola en factor importante de la eficiencia total del sistema.

#### 2.3. Redes Neuronales

Una Red Neuronal Artificial es un paradigma de procesamiento de información que busca emular el comportamiento en el cual el sistema nervioso biológico procesa la información [1].

Adicionalmente, podemos decir que una red neuronal es un procesador distribuido paralelamente masivo que posee la tendencia natural de almacenar el conocimiento experimental y volverlo utilizable. Se asemeja al cerebro en dos aspectos:

- El conocimiento es adquirido por la red neuronal a través de un proceso de aprendizaje.

- Las fortalezas de las interconexiones, conocida como "pesos sinápticos" son usadas para almacenar el conocimiento [6].

Como ya se menciono, la unidad de procesamiento de la red es la neurona artificial, y su adecuado funcionamiento se logra a través del proceso de entrenamiento o aprendizaje. Según el ordenamiento de las neuronas de la red y del tipo de aprendizaje utilizado, se encuentran diversas clases de redes neuronales.

Según su arquitectura, pueden ser redes de una sola capa, redes multicapa y redes recurrentes. Según su método de aprendizaje se tiene dos tipos:a) según el paradigma usado puede ser supervisado, no supervisado o híbrido; y b) según el algoritmo de aprendizaje, este puede ser de error-corrección, Boltzmann, Hebbian, competitivo. Además, las funciones de activación utilizadas son la identidad, escalón unitario, sigmoide, tangente hiperbólica, de probabilidad Gaussiana [5] [6].

#### 2.3.1. Redes Multicapa

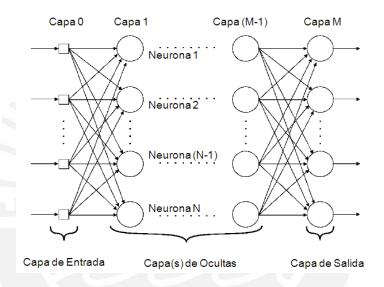

Es aquella red que posee una capa de entrada, una capa de salida y una o más capas ocultas. Existen la red Perceptron Multicapa (Multi-Layer Perceptron, MLP) y la red de Base Radial (Radial-Basis Function Networks, RBF).

La red MLP "es una generalización del perceptron y surgió como consecuencia de las limitaciones de dicha arquitectura en lo referente al problema de la separabilidad no lineal" [15]; mientras que la red RBF posee una única capa oculta y sus neuronas tienen un carácter local; es decir, cada una de ellas se activa en una

región diferente del espacio de patrones de entrada, lo cual se debe al uso de las llamadas funciones de base radial como función de activación [14].

Estas redes multicapa se utilizan en aplicaciones como reconocimiento de patrones, aproximación de funciones, predicción, control [9].

#### 2.3.2. Red Perceptron Multicapa (MLP)

Es aquella red que contiene una o más capas ocultas, muestra un alto grado de conectividad y sus funciones de activación son diferenciables [6].

Figura 2. Red Neuronal Perceptron Multicapa (MLP) [11].

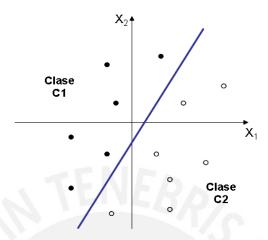

Se encuentra conformada por un arreglo de perceptrones, los cuales son la forma más simple de una red neuronal, inventada por Rosenblatt en 1958. El Perceptron consiste básicamente en una neurona simple con pesos sinápticos ajustables y un umbral de activación, y es utilizado para clasificar patrones linealmente separables.

El principio y sustento del perceptron se encuentra en el Teorema de convergencia del Perceptron:

"Dadas dos clases C1 y C2, dichas clases son linealmente separables si existe un vector de pesos sinápticos configurado para tal fin. También, si se conoce que dos clases C1 y C2 son linealmente separables, entonces existe un vector de pesos sinápticos que lo permita. Para lograr tal fin, los pesos sinápticos son ajustados (actualizados) según el error generado, las entradas y el parámetro razón de aprendizaje" [6].

La figura 3 muestra dos conjuntos de datos perteneciente a dos clases que son linealmente separables. Este diagrama ilustra el teorema de convergencia del perceptron, pues es este último quien establece la separación de las clases según sus pesos sinápticos.

Figura 3. Teorema de Convergencia del Perceptron [6].

#### 2.3.3. Paradigmas de Aprendizaje

Son las formas en la cuales se realiza el proceso de aprendizaje de la red neuronal. Pueden ser supervisado, no supervisado e híbrido [9] [15].

Es supervisado cuando la información es presentada a la red en forma de patrones de entrada y los resultados deseados son conocidos previamente. Un supervisor (profesor) verifica la salida de la red y la compara con la esperada. Por lo tanto, minimiza esta diferencia mediante la modificación de los pesos sinápticos.

Es no supervisado cuando la información es presentada a la red bajo forma de patrones de entrada y los resultados no son conocidos previamente, pues no requiere de la salida correcta a cada patrón de entrada. Este método explora la relación o correlación existente entre los patrones de los datos y los organiza agrupándolos en diferentes categorías según características en común.

El paradigma híbrido combina los aprendizajes supervisado y no supervisado aplicándolos en distintas capas de la red; es decir, algunos pesos sinápticos son ajustados a través del aprendizaje supervisado y los otros mediante el aprendizaje no supervisado [9] [15].

#### 2.3.4. Aprendizaje Error-Corrección

En este método se genera la señal de error mediante la comparación entre la salida de la red ante el estímulo de un ejemplo y la señal deseada. Así, el objetivo es minimizar esta señal de error a través de la "función de costo" (cost function). De esta forma, el aprendizaje es estrictamente un problema de optimización mediante el ajuste de los pesos sinápticos [6].

Entre los algoritmos de aprendizaje que utilizan este método se encuentran el algoritmo LMS (Least Mean Square, Mínimo Error Cuadrático Medio), Backpropagation, Adaline, Madaline.

#### 2.3.5. Algoritmo Backpropagation

Consiste en dos procesos, uno hacia adelante (forward pass) y uno hacia atrás (backward pass) [6].

En el primero, se coloca a la entrada de la red una señal de entrenamiento, la cual atraviesa la misma generando una salida que es comparada con la salida deseada, produciéndose una señal de error por cada neurona de la capa de salida.

En el segundo, dicha señal de error es propagada desde la salida hacia atrás, donde se realiza la actualización y modificación de los pesos sinápticos en función de la razón de aprendizaje, el gradiente local y la entrada de la neurona específica. Este proceso termina según un criterio de parada, el cual permite un error mínimo en la red.

#### 2.4. <u>Dispositivo lógico programable FPGA</u>

Un Dispositivo Lógico Programable (Programmable Logic Device, PLD) es un chip de propósito general para la implementación de circuitos lógicos. Contiene un conjunto de elementos lógicos agrupados de diversas maneras. Puede ser visto como una "caja negra" que contiene compuertas lógicas e interruptores programables, los cuales permiten a las compuertas conectarse entre sí para formar cualquier circuito lógico requerido [16].

Se clasifican según el grado de complejidad y cantidad de recursos lógicos presentes en el dispositivo. Así, existen SPLD (Simple PLD), dentro de los cuales

están los PLA (Programmable Logic Array), PAL (Programmable Array Logic), PLA/PAL Registradas (Registered PLA/PAL), GAL (Generic PAL); CPLD (Complex PLD); FPGA (Fiel-Programmable Gate Array) [16][17].

Dentro de este contexto, un FPGA (Arreglo de puertas programable en campo) es un PLD que soporta implementaciones de circuitos lógicos y sistemas digitales relativamente grandes y son programables en campo, es decir, en el lugar del diseño, junto al diseñador [16]. Presenta una arquitectura virgen, la cual puede ser configurada a necesidad, logrando una gran diversidad de aplicaciones. El almacenamiento de estas conexiones se realiza en una SRAM en la mayoría de los casos, pero también puede realizarse mediante FLASH o antifuse [16][17].

#### 2.4.1. Arquitectura genérica

Básicamente, un FPGA contiene bloques lógicos, recursos de interconexión y unidades de entrada y salida [16] [17].

Los bloques lógicos están conformados por tablas de verdad (Look-Up Table, LUT), la cual es un circuito programable que permite implementar cualquier función lógica de un número determinado de entradas, por flip-flops y multiplexores.

Para controlar las conexiones necesarias entre los bloques lógicos, los recursos de interconexión y las unidades de entrada y salida se programan dichas conexiones mediante técnicas de programación, siendo la más utilizada la tecnología de celdas SRAM.

Adicionalmente, según el FPGA, este puede contar con elementos adicionales y bloques dedicados como memorias, PLL, multiplicadores, MAC's, DSP's, microprocesadores.

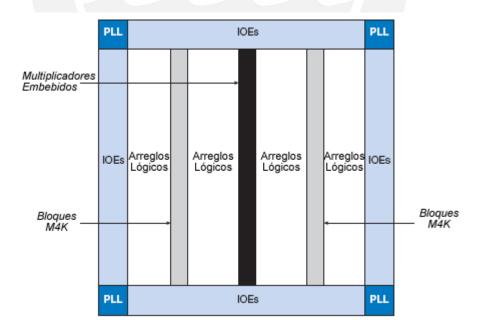

#### 2.4.2. Arquitectura del FPGA CYCLONE II de ALTERA

Es un FPGA basado en un proceso SRAM de 1.2V, 90nm con una alta densidad de elementos lógicos (Logic Elements, LE's) entre 4608 y 68416, y hasta 1.1Mbits de memoria RAM embebida [18].

Además de los elementos básicos, cuenta con bloques dedicados adicionales como bloques de memorias RAM embebidas de 4K, multiplicadores embebidos de 18x18, PLL's y unidades de entrada/salida avanzadas. La cantidad de cada uno de ellos depende del dispositivo elegido, pues estas características están presentes en toda la familia.

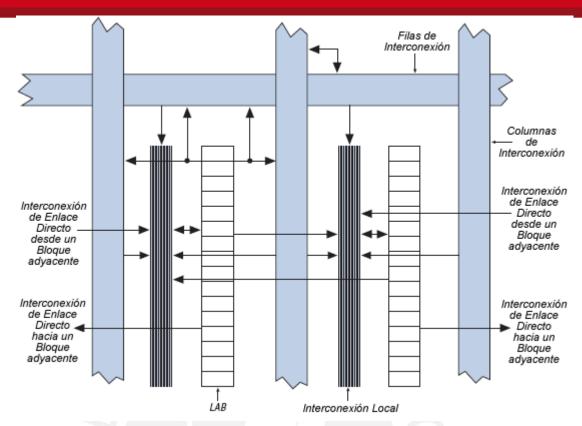

La disposición de sus componentes se muestra en la figura 4. Se aprecia los bloques de memoria, los multiplicadores embebidos, los PLL's, los arreglos lógicos y los bloques de entrada/salida (Input-Output Element, IOE).

Los arreglos lógicos están estructurados en base a los arreglos de bloques lógicos (Logic Array Blocks, LAB's), que son un arreglo de LE's, y a los recursos de interconexión locales (Local Interconnect) [18].

Además, se cuentan con filas y columnas de interconexión para realizar conexiones entre LE's de diferentes LAB's. La estructura del LAB se muestra en la figura 5.

Figura 4. Diagrama de bloques del FPGA Cyclone II EP2C20 [18].

Figura 5. Estructura del LAB del FPGA Cyclone II [18].

#### 2.5. Lenguaje de descripción de hardware VHDL

Es un Lenguaje de Descripción de Hardware (HDL: Hardware Description Language) que describe el comportamiento de un circuito o sistema electrónico; cuyo circuito o sistema físico (real) puede ser implementado en el dispositivo respectivo.

Es utilizado principalmente, junto con Verilog, para implementar circuitos en FPGA's, CPLD's y en el campo de los ASIC's, siendo este diseño portable y reusable.

Cabe mencionar que las sentencias VHDL son inherentemente concurrentes, es decir, se ejecutan simultáneamente. Solamente las que se encuentren dentro de procesos, funciones o procedimientos son ejecutadas de manera secuencial.

Para realizar esta labor, utiliza las denominadas herramientas EDA (Electronic Design Automation) creadas especialmente para las tareas de síntesis, implementación y simulación de circuitos descritos. Algunas son ofrecidas dentro de los entornos de desarrollo de los fabricantes (Quartus II, MAXPLUS II, ISE)

mientras que otros son desarrollados y ofrecidos por compañías EDA especializadas como Leonardo Spectrum (sintetizador de Mentor Graphics), Synplify (sintetizador de Synplicity) y ModelSim (simulador de Mentor Graphics) [17].

#### 2.6. Modelo teórico

El constante incremento de las capacidades de procesamiento requeridas para los procesos y necesidades actuales conlleva al desarrollo de nuevas teorías y tecnologías que puedan suplir las carencias provocadas por la falta de eficacia de las técnicas empleadas. Las redes neuronales son capaces de resolver gran parte de estos problemas mediante su implementación tanto en hardware como en software, pues son utilizadas en diversos campos como son el control, la industria, el reconocimiento de patrones, la medicina, los negocios y demás. Sin embargo, existen aplicaciones en las cuales necesariamente se requiere de una implementación en hardware para que dicha tarea pueda ser llevada a cabo.

Así, los dispositivos (hardware) donde implementemos dichas redes deben ocupar el área mínima posible con las mayores prestaciones posibles para garantizar una mejor eficiencia; consiguiendo mayor velocidad y confiabilidad al utilizar hardware digital dedicado.

Dentro de dichos dispositivos mencionados, destacan los FPGA's, pues pueden ser configurados según la necesidad y los requerimientos del sistema; y también pueden ser reconfigurados, permitiendo una gran flexibilidad tanto en el diseño como en la implementación. Para configurar el FPGA utilizaremos los llamados lenguajes de descripción de hardware (HDL), y específicamente VHDL. Un posterior avance sería el desarrollo de un circuito integrado de aplicación específica (ASIC) mediante la tecnología VLSI, pues el diseño del sistema en un FPGA es un paso previo para este fin. De esta forma, se alcanzaría un chip con mejores prestaciones en aspectos como velocidad, área ocupada y consumo de potencia.

#### 2.6.1. Definiciones Operativas

El presente diseño de una red neuronal en un FPGA debe ser evaluado para medir su desempeño y verificar su funcionamiento. De esta forma, los criterios más

importantes son los referidos a la efectividad del sistema y a la arquitectura planteada.

#### Estructura de la red neuronal

Indica el número de capas utilizadas en la red neuronal propuesta, así como el número de neuronas en cada una de ellas. Es de importancia porque es la base de la arquitectura lógica a plantear, además de ser la que va a resolver el problema planteado.

#### Entrenamiento de la red neuronal

Corresponde a la cantidad de datos (base de datos) con la cual se va a entrenar a la red neuronal. Este es un factor importante pues, dado que la red requiere conocimientos, a una mayor cantidad de datos de entrenamiento (mejor entrenamiento) el sistema se comportará de una manera más eficiente y producirá menos errores. Caso contrario, la red no se comportará según lo previsto.

#### Recursos utilizados

Corresponde a la cantidad de compuertas, flip-flops, multiplicadores, memorias (recursos lógicos) utilizados por el diseño. Es una forma indirecta de medir el área ocupada en el FPGA. Según este parámetro escogeremos al FPGA. En el diseño se procurará que sea el mínimo posible para reducir el área utilizada.

#### Frecuencia de trabajo

Es la frecuencia a la cual va a trabajar el sistema diseñado. Es una medida de la velocidad del sistema.

#### Tiempo de respuesta del sistema

Indica el tiempo que se demora el sistema en cumplir con la labor asignada y otorgar un valor válido a la salida.

#### Porcentaje de Error

Corresponde a la cantidad de errores que genera el sistema respecto a la cantidad de salidas que genera en un periodo de operación. Es un indicador de la calidad del sistema, razón por la cual debe ser el menor posible.

#### Portabilidad del diseño

Indica si el diseño realizado con VHDL es transparente o no a los diferentes FPGA's. Esto quiere decir que un código será portable si puede ser sintetizado en cualquier FPGA. Significa que es independiente del dispositivo, pues no ha utilizado recursos propios del FPGA, los cuales pueden diferir entre las diferentes familias y fabricantes. De esta forma se logra que el sistema pueda ser implementado en cualquier FPGA que cumpla con los requerimientos mínimos del mismo sistema.

#### **CAPÍTULO 3**

# PLANTEAMIENTOS PARA EL DISEÑO DE LA RED NEURONAL PERCEPTRON MULTICAPA

#### 3.1. Hipótesis de la investigación

#### 3.1.1. Hipótesis principal

Dado que los procesos y problemas actuales son cada vez más complejos y que buena parte de estos pueden ser resueltos con aplicaciones basadas en redes neuronales tanto en hardware como en software; entonces, el diseño de la arquitectura de una red neuronal Perceptron Multicapa sobre un FPGA permite el desarrollo de un sistema modular en hardware de propósito general que puede ser configurado para dar solución a tareas específicas; y en este caso, aplicarla en un sistema de reconocimiento de caracteres.

#### 3.1.2. <u>Hipótesis secundarias</u>

- Contar con una implementación en hardware de una red neuronal permite liberar de un procesamiento intenso al procesador (CPU) y utilizarlo en otras tareas.

- La red neuronal multicapa (MLP) es una arquitectura de propósito general pues puede ser configurada para cumplir diferentes tareas según sean requeridas.

- Dadas las características propias de las redes neuronales, el desarrollo de una red neuronal sobre un FPGA permite obtener una arquitectura flexible y adaptable a distintas aplicaciones.

#### 3.2. Objetivos de la investigación

#### 3.2.1. Objetivo general

Diseñar una arquitectura para una red neuronal Perceptron Multicapa en un FPGA y verificar su funcionamiento mediante su implementación en un sistema de reconocimiento de caracteres.

#### 3.2.2. Objetivos específicos

- Diseñar la red neuronal artificial para el reconocimiento de caracteres en un software como MATLAB con ayuda de su herramienta para redes neuronales (Neural Networks Toolbox) y entrenarla mediante el algoritmo Backpropagation.

- Diseño de la arquitectura de una neurona artificial, describirla en el FPGA y verificar su funcionamiento.

- Buscar en todo momento la optimización de los recursos del FPGA, así como diseños modulares de cada componente. Además, que el diseño global sea lo más portable posible.

#### 3.3. Metodología de la investigación

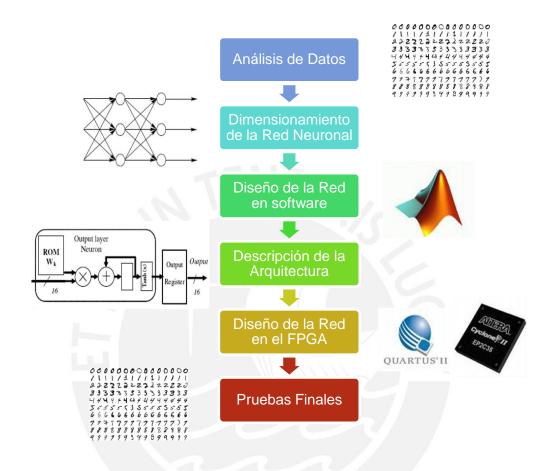

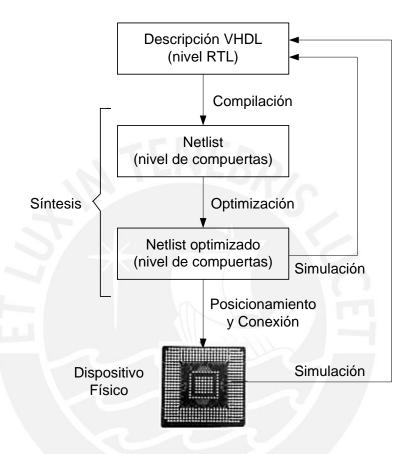

El diseño de la arquitectura se desarrollará siguiendo el siguiente esquema, el cual muestra la secuencia de pasos para la obtención del sistema.

Figura 6. Metodología de diseño.

El primer paso consiste en analizar los datos que son objeto de estudio. Así podremos obtener información necesaria que será utilizada en la siguiente etapa. Aquí, el tipo de imagen, así como su tamaño, dimensiones y otras características son extraídos, definidos y considerados dentro de los parámetros de diseño.

Con la información obtenida y con los parámetros definidos se procede a dimensionar la red neuronal. Las dimensiones que pueden ser definidas son la cantidad de entradas y la cantidad de salidas de la red, puesto que se infieren directamente de los requerimientos del sistema.

A partir de este punto comienza el diseño. Al tratarse de una red MLP, las incógnitas a resolver son la cantidad de capas ocultas y la cantidad de neuronas de cada capa oculta. El Teorema de Aproximación Universal (Cybenko, 1989;

Funahashi, 1989; Hornik et al., 1989) nos otorga el fundamento matemático para la aproximación a realizar:

Sea  $\varphi(\cdot)$  una función continua no constante, acotada y monótonamente creciente. Sea  $I_p$  el espacio p-dimensional unitario  $[0,1]^p$  y  $C(I_p)$  el espacio de funciones continuas sobre  $I_p$ . Entonces, dada cualquier función  $f \in C(I_p)$  y  $\varepsilon > 0$  existe un entero M y un grupo de constantes reales  $\alpha_i$ ,  $\theta_i$  y  $w_{ij}$  donde  $i \in [1,M]$  y  $j \in [1,p]$  con los que podemos definir

$$F(x_1, ..., x_p) = \sum_{i=1}^{M} \alpha_i \varphi \left( \sum_{j=1}^{p} w_{ij} x_j - \theta_i \right)$$

(1)

como una aproximación de la función  $f(\cdot)$  , tal que

$$\left| F(x_1, ..., x_p) - f(x_1, ..., x_p) \right| < \varepsilon \tag{2}$$

para todo  $\{x_1,...,x_p\} \in I_p$  [6].

Esta definición se ajusta perfectamente a una red MLP con una capa oculta, pues cuenta con p entradas, M neuronas en la capa oculta, pesos sinápticos  $w_{ij}$  y umbrales  $b_i$ , una función de activación sigmoide que cumple con lo anterior y la salida que es función lineal de las salidas de las neuronas ocultas. Hay que tener en cuenta que el teorema no dice que utilizar una única capa oculta sea lo más óptimo, pero nos garantiza la existencia de una solución [6].

Además, la cantidad de neuronas en la capa oculta debe ser escogida según cumpla los requerimientos establecidos. Esto quiere decir que el diseño puede empezar con dos neuronas en la capa oculta, generar la red neuronal y verificar si cumple lo determinado. Caso contrario, se aumenta la cantidad de neuronas hasta cumplir con los requerimientos. Es importante mencionar que se debe buscar, en lo posible, el menor número de neuronas para esta capa, pues de no ser así estaríamos perdiendo la capacidad de generalización de la red neuronal, pues el sistema estaría aprendiendo también el ruido presente en las imágenes de entrenamiento [6].

De esta forma, se empieza el diseño escogiendo una sola capa oculta con una cantidad de neuronas intermedia entre el número de entradas y el número de salidas.

Tras obtener un diseño satisfactorio, se describe la arquitectura para la red diseñada. En esta etapa hay que tener en cuenta las dimensiones de la red, de sus pesos sinápticos, de la función de activación utilizada y de los formatos utilizados tanto en la entrada como en la salida. Un factor determinante es escoger la representación numérica adecuada y su resolución pues de ello depende el diseño de los posteriores bloques del sistema.

Teniendo la arquitectura completa, se procede a su diseño para su implementación en el FPGA. La arquitectura se describe utilizando VHDL y una herramienta EDA que realice la síntesis del circuito y su posterior implementación en el dispositivo. Para esta labor, se deben considerar los objetivos del diseño en cuanto se quiera un diseño portable u optimizado al dispositivo, o específico a los requerimientos o genérico. Cada uno de los módulos diseñados debe ser simulado para verificar su funcionamiento y buscar garantizar que no va a generar errores al momento de unir el sistema completo. Adicionalmente, es de esperar que en cualquiera de los casos exista un balance adecuado entre los recursos lógicos utilizados y la frecuencia de trabajo del sistema.

Por último, se realizan las simulaciones finales del sistema y se procede a su implementación en el FPGA. En este punto se realizan pruebas adicionales para comprobar que la red neuronal cumple con lo esperado.

Cabe mencionar que se realiza el diseño de la red en software debido a que el aprendizaje no se realizará en hardware, pues el FPGA será destinado solo a la tarea de reconocimiento mas no se implementará la etapa de entrenamiento. Es por este motivo que el entrenamiento se realiza en software y se extraen los resultados obtenidos del proceso, los pesos sinápticos y la cantidad de neuronas y capas ocultas.

#### 3.4. Análisis del sistema y determinación de requerimientos

La red neuronal va a ser entrenada y diseñada para reconocer dígitos manuscritos por lo cual requiere de 10 salidas, cada una de las cuales identificará a un digito en particular.

La etapa de entrenamiento se realizará con la base de datos modificada del Instituto Nacional de Estándares y Tecnología, MNIST (Modified National Institute of Standards and Technology database), la cual consta de 30000 ejemplos de la base

de datos especial 1 del NIST (SD-1) y 30000 de la base de datos especial 3 del NIST (SD-3) para el entrenamiento y de 5000 de cada uno para el test; es decir, de 60000 imágenes de dígitos manuscritos para la etapa de entrenamiento y 10000 para la etapa de test. La base de datos SD-3 es más fácil de reconocer que la SD-1 debido a que la primera fue realizada a partir de empleados (Census Bureau employees) y la segunda a partir de estudiantes de colegio [19].

Dichas imágenes se encuentran en escala de grises y además, están normalizadas en un tamaño de 20x20 pixeles y el centro de masa de cada una está centrado en un campo de 28x28 pixeles [19].

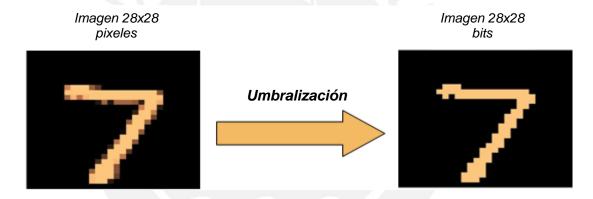

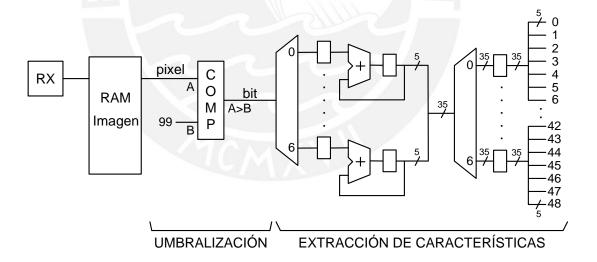

Según esto, el sistema recibe de entrada una imagen de 28x28 pixeles, por lo cual, los datos serán umbralizados y agrupados para disminuir la cantidad de entradas a la red. Así, gracias a la umbralización, disminuimos la cantidad de datos de 784 pixeles a 784 bits.

Figura 7. Proceso de umbralización.

La red neuronal a utilizar es una red MLP, y el algoritmo de entrenamiento es el de backpropagation; por lo cual la función de activación requerida por el algoritmo es una función diferenciable, pues se utiliza su gradiente para la actualización de los pesos sinápticos.

La magnitud de los pesos obtenidos en este proceso determina la cantidad de bits así como el formato de la representación numérica. También, la cantidad de neuronas y la cantidad de capas ocultas tienen implicancia en la cantidad de recursos lógicos a utilizar.

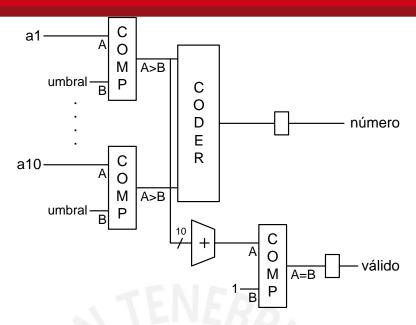

Las salidas de la red neuronal serán validadas comparando los resultados con los rangos esperados para un correcto reconocimiento. De esta forma se eleva el porcentaje de eficiencia del sistema al incorporar una etapa de verificación.

Finalmente, el sistema debe tener una confiabilidad aceptable, pues realiza una tarea crítica dentro de un OCR. De este modo, se espera una eficiencia cercana al 90% en la etapa de test.

Por lo tanto, los parámetros definidos para el sistema son los siguientes:

- Señal de entrada del sistema: Imagen digital de un dígito manuscrito de 28x28 pixeles en escala de grises.

- Señal de salida del sistema: número reconocido y una señal de validación, la cual indica si el número otorgado es válido o no.

- Cantidad de entradas de la red neuronal: se determinará con el proceso de diseño de la red en software.

- Cantidad de salidas de la red neuronal: se tendrán 10 salidas.

- Cantidad de capas ocultas: una capa oculta.

- Cantidad de neuronas de la capa oculta: se determinará con el proceso de diseño de la red en software.

- Función de activación de la red: se utilizará en todas las capas la función

Sigmoide como función de activación, al tratarse de la más utilizada para este tipo de red neuronal.

- Umbralización: este proceso se realizará con un umbral de 100 para convertir los pixeles mayores o iguales que el umbral a un '1' lógico y los menores que el umbral a un '0' lógico.

# 3.5. Consideraciones para el diseño

El sistema desarrollado forma parte de un OCR, y específicamente conforma la etapa de reconocimiento del carácter. Así, se tendrá como entrada a esta etapa la imagen extraída del documento mediante la segmentación, así como centrada y normalizada al tamaño de 28x28 pixeles en escala de grises. Cualquier paso previo se considera ya realizado y no forma parte del desarrollo de la presente tesis.

Como ya se mencionó, la etapa de entrenamiento de la red neuronal no se implementará en el dispositivo. De esta forma se tendrá un hardware dedicado con capacidad de reprogramación, con lo cual, basta con re-entrenar la red en software para que cumpla con la nueva tarea, obtener los parámetros requeridos por el sistema e ingresarlos en la descripción del circuito para su posterior síntesis e implementación en el FPGA.

Para el entrenamiento, se utiliza la herramienta de redes neuronales del software Matlab 7.1 de Mathworks (Neural Networks Toolbox). Se desarrollarán los programas necesarios para la umbralización de la imagen, para la extracción de algunas características, para obtener la red neuronal, su entrenamiento con la base de datos de entrenamiento del MNIST y su posterior etapa de test con la base de datos de test del MNIST. Adicionalmente, se generarán programas para elaborar los archivos necesarios (\*.vhd) que contengan la información de los pesos sinápticos y umbrales obtenidos tras el proceso de aprendizaje. Así, se tendrá una metodología automatizada para que a partir de los resultados obtenidos se tengan los archivos necesarios a incluir en el diseño en hardware de la red neuronal.

El diseño en software se seguirá hasta obtener una eficiencia cercana al 90% teniendo como entrada la base de datos de test del MNIST. Dado que el objetivo principal de la tesis es el de obtener una arquitectura para una red neuronal, una eficiencia de 90% es aceptable para verificar el buen funcionamiento del sistema diseñado. Además, hay que indicar que la base de datos del MNIST es una muestra muy representativa del universo y que con dicho porcentaje no se pierde la visión global de obtener un sistema confiable.

El diseño en hardware se realizará mediante la descripción del mismo utilizando el lenguaje de descripción VHDL en la herramienta EDA Quartus II 7.1 de Altera, al realizarse el diseño en un FPGA Cyclone II de la misma compañía. La descripción será modular y genérica para facilitar el diseño funcional y para que la red diseñada sea fácilmente adaptable para que cumpla en algún futuro una tarea diferente a la actual. Dado que el sistema se basa en suma de productos y acoplo de etapas, las operaciones de multiplicación y división aparecen con frecuencia; por lo tanto, el diseño utilizará recursos dedicados del dispositivo, como son multiplicadores embebidos, lo cual le quita portabilidad al diseño. Si bien esto puede parecer perjudicial, es necesario para la optimización del sistema, pues las operaciones de multiplicación y división son las más críticas y ocasionan los mayores retardos. Pero, el hecho de utilizar recursos dedicados del FPGA no impide que el sistema se implemente en otra familia de dispositivos, pues las herramientas EDA infieren estos bloques dedicados tras interpretar la descripción realizada. Así, solamente se pierde un grado de portabilidad mas no se vuelve no portable.

Por último, hay que mencionar que existe una dependencia entre el tamaño (dimensiones) y requerimientos de la red neuronal y el FPGA a utilizar. Esto se debe a que el dispositivo tiene limitaciones en cuanto a la cantidad de recursos

lógicos que posee y a la cantidad y variedad de bloques dedicados que optimizan el diseño en cuanto a rapidez y área ocupada. Así, el dispositivo debe ser elegido según la aplicación y en este caso según la red neuronal que va a cobijar. Hay que mencionar que las limitaciones de espacio se deben a que en la presente tesis no se considera la característica propia del FPGA de poder reconfigurarse. Sin embargo, la característica que si se aprovechará será la del paralelismo que posee, al implementar todas las capas de la red neuronal y realizar los cálculos lo más paralelo posible.

## **CAPÍTULO 4**

# DISEÑO DE LA ARQUITECTURA PARA LA RED NEURONAL PERCEPTRON MULTICAPA

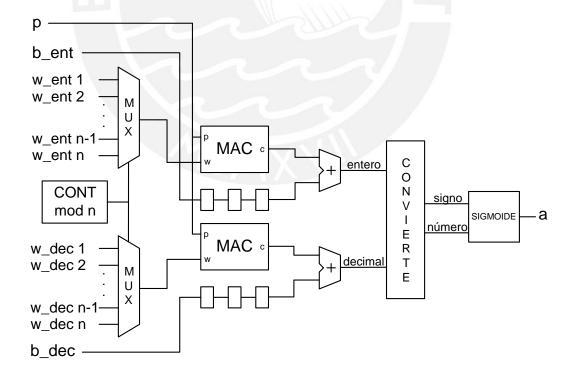

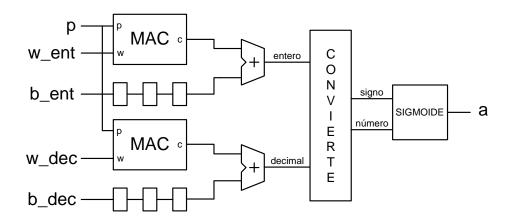

El presente capítulo muestra el proceso de diseño de la red neuronal, lo cual implica la determinación de sus dimensiones, sus parámetros, y la arquitectura en hardware que permita implementar la red neuronal propuesta en el FPGA.

Siguiendo la metodología planteada, se procede al diseño de la red neuronal en software para obtener y extraer sus dimensiones y parámetros. De esta forma se encuentran el número de entradas, el número de neuronas en la capa oculta, y los valores de los pesos sinápticos y umbrales de la red neuronal.

Posteriormente, considerando estos valores encontrados, se diseña la arquitectura digital en base a bloques y componentes modulares y genéricos que permiten una adecuada interacción entre ellos. Así, el diseño global se complementa con el proceso de aprendizaje anterior incorporando los pesos sinápticos y los umbrales de cada neurona.

## 4.1. <u>Diseño de la red neuronal mediante software</u>

Para este proceso se utilizó le herramienta de redes neuronales del software Matlab 7.1 (Neural networks toolbox); con la cual se realizó todas las etapas de este proceso: dimensionamiento, entrenamiento y validación de la red neuronal; y la extracción de los pesos sinápticos y umbrales encontrados.

Si bien el objetivo del presente trabajo es obtener una red neuronal en hardware, este paso es de suma importancia pues nos permite escoger la mejor red neuronal para nuestro propósito, así como encontrar sus parámetros y dimensiones para incorporarlos al diseño en hardware y establecer con ellos la representación numérica adecuada y la arquitectura del circuito.

## 4.1.1. Desarrollo y entrenamiento de la red neuronal.

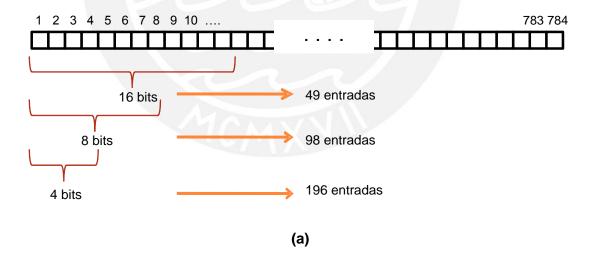

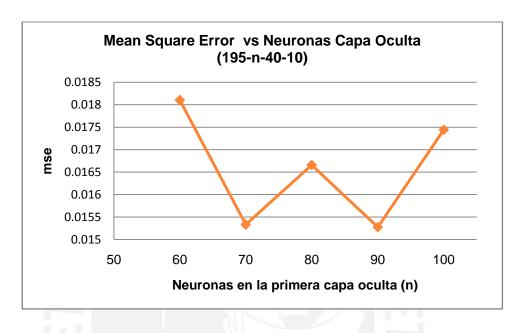

El primer paso consiste en escoger la cantidad de entradas en la capa de entrada de la red neuronal. Para ello, sabemos que la entrada de la red es una imagen de 28x28 bits, es decir, un total de 784 bits.

Con el objetivo de disminuir el número de entradas y la cantidad de datos con la que debe trabajar la red neuronal, los bits de la imagen de entrada son agrupados. Este proceso es denominado "extracción de características", y existen diversas formas de agrupar dichos bits. Debido a esto, se desarrollaron diferentes redes neuronales para encontrar la forma de agrupación óptima en cuanto a cantidad de entradas, cantidad de neuronas, valor absoluto de los datos y eficiencia.

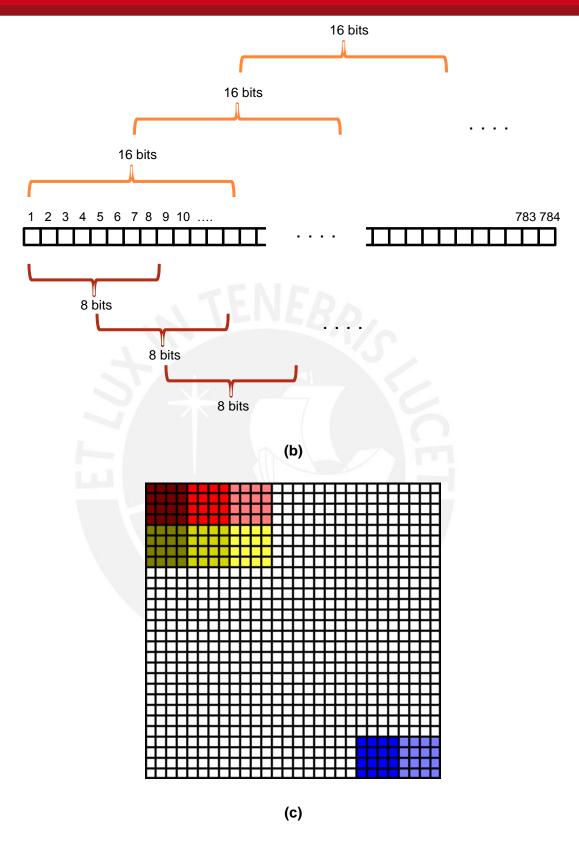

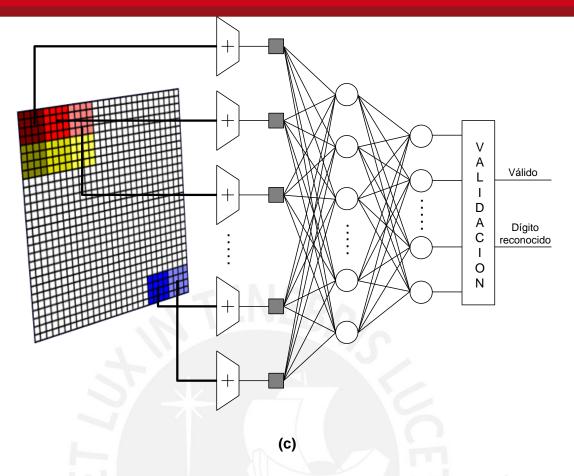

La figura 8 muestra algunas formas de agrupación de bits, donde en (a) los bits de la imagen se juntan para formar un solo vector unidimensional del cual se extraen palabras binarias de la cantidad de bits mostrada; en (b) se procede muy similar a lo anterior, solo que las palabras formadas se sobreponen para contar con una mayor cantidad de datos; mientras que en (c) la forma de agrupación cambia y se divide la imagen en imágenes más pequeñas, sumando los bits de estas sub-imágenes para ingresarlas a la red.

Figura 8. Extracción de características, formas de agrupación de los bits de la imagen de entrada: (a) palabras binarias de un vector unidimensional, (b) palabras binarias sobrepuestas de un vector unidimensional, (c) suma de bits de sub-imágenes de menor tamaño.

#### TESIS PUCP

Con estas formas mencionadas, se procedió a entrenar diversos arreglos de redes neuronales mediante el algoritmo de entrenamiento backpropagation. Todo esto para encontrar la red adecuada para nuestro propósito.

Antes de iniciar el aprendizaje, la base de datos fue adaptada a los requerimientos de cada forma de agrupación. Así, se crearon diversos scripts que lograran lo antes mencionado. También, el archivo de respuestas deseadas fue adaptado para que cumpla con lo estipulado de las 10 neuronas en la capa de salida.

Luego, se procedió al entrenamiento de las redes neuronales. Los parámetros del proceso de entrenamiento fueron escogidos según las recomendaciones hechas por los desarrolladores de la herramienta en software [20]. De esta manera, los únicos factores importantes a decidir son la cantidad de veces que los datos pasan por la red para que los pesos y umbrales sean modificados (epochs) y la función de entrenamiento, que determina el algoritmo a seguir para el proceso y el tiempo de convergencia de la red neuronal según los parámetros establecidos para el entrenamiento.

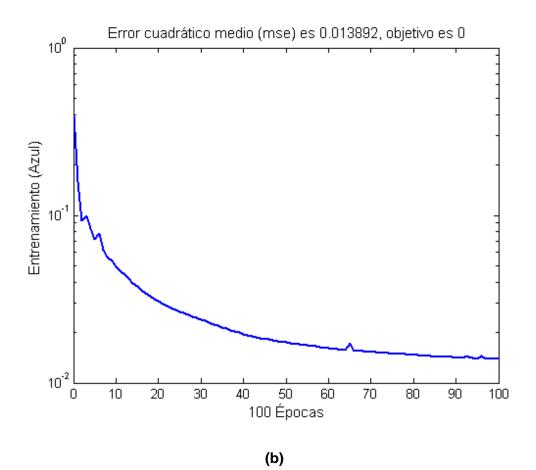

Según [20], para una aplicación de reconocimiento, la mejor opción como función de entrenamiento es el algoritmo "Resilent Backpropagation", cuya función de entrenamiento es llamada "trainrp". Un factor importante en el proceso, y que se relaciona directamente con la eficiencia del sistema es la medida de la función de desempeño (performance function). En este caso, dicha función es la del error cuadrático medio (mse) y nos indicará que cerca se está de conseguir un error promedio de cero.

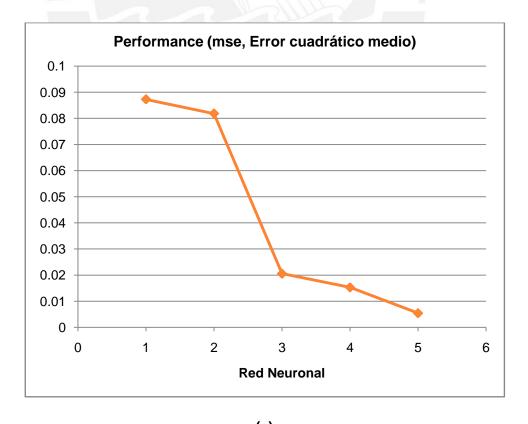

La primera opción que se tuvo en cuenta fue la de formar palabras binarias que no se sobrepongan. La tabla 2 y la figura 9 muestran los resultados obtenidos para 5 redes neuronales. En las tablas, el parámetro performance hace referencia al error cuadrático medio (mse).

En ellas se observa que si bien alcanzan un error bajo en algunos casos, las magnitudes absolutas de los pesos sinápticos son muy elevadas, lo que dificultaría el diseño de la arquitectura al requerir una mayor cantidad de bits. Además, la cantidad de entradas es aún elevada si escogemos trabajar con el error más bajo.

Tabla 2.a. Características de las redes neuronales [Elaboración propia].

| Red<br>Neuronal | #bits /<br>entrada | Neuronas en la<br>capa de entrada | Neuronas en la<br>capa oculta | Neuronas en<br>la capa de<br>salida |

|-----------------|--------------------|-----------------------------------|-------------------------------|-------------------------------------|

| 1               | 16                 | 49                                | 25                            | 10                                  |

| 2               | 16                 | 49                                | 40                            | 10                                  |

| 3               | 8                  | 98                                | 25                            | 10                                  |

| 4               | 8                  | 98                                | 50                            | 10                                  |

| 5               | 4                  | 196                               | 50                            | 10                                  |

Tabla 2.b. Entrenamiento [Elaboración propia].

| Red Neuronal | Epochs | Performance (mse) | Peso máximo |

|--------------|--------|-------------------|-------------|

| 1            | 500    | 0.0872867         | 380         |

| 2            | 500    | 0.0818516         | 23020       |

| 3            | 500    | 0.0205614         | 23260       |

| 4            | 500    | 0.0153069         | 23000       |

| 5            | 500    | 0.00543357        | 15870       |

(a)

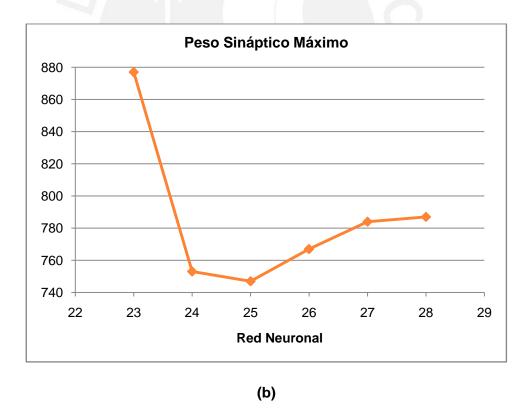

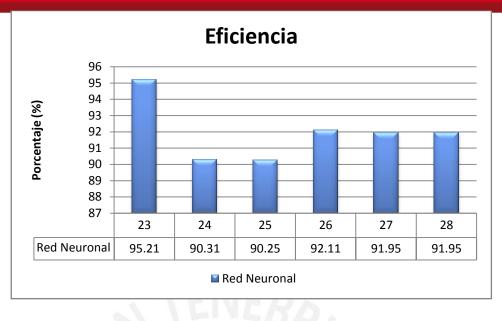

Figura 9. Error cuadrático medio (a) y peso sináptico máximo (b) por red neuronal.

Se llegó a la conclusión que este tipo de agrupación no es la más adecuada para esta aplicación puesto que los pesos que se obtienen son muy elevados para implementar la red neuronal completa dentro del FPGA.

Como segundo caso, se formaron palabras binarias sobrepuestas hasta la mitad de la anterior, según lo muestra la figura 8. Además, tras entrenar una red neuronal, se observó que la magnitud absoluta máxima de los pesos sinápticos no variaba mucho, por lo cual se pensó en añadir una capa oculta adicional para corregir este inconveniente.

Los resultados de este proceso se muestran en la tabla 3. El número de neuronas desarrolladas en este caso fue mayor puesto que se requería una mayor cantidad de datos al tratarse de dos más variables a considerar dentro del análisis.

Tabla 3.a. Características de las redes neuronales [Elaboración propia].

| Red<br>Neuronal | #bits /<br>entrada | Neuronas en<br>la capa de<br>entrada |     | as en la<br>oculta | Neuronas en<br>la capa de<br>salida |

|-----------------|--------------------|--------------------------------------|-----|--------------------|-------------------------------------|

| 6               | 8                  | 195                                  | 5   | 50                 | 10                                  |

| 7               | 8                  | 98                                   | 50  | 20                 | 10                                  |

| 8               | 8                  | 195                                  | 60  | 20                 | 10                                  |

| 9               | 8                  | 195                                  | 50  | 25                 | 10                                  |

| 10              | 8                  | 195                                  | 100 | 40                 | 10                                  |

| 11              | 8                  | 195                                  | 80  | 40                 | 10                                  |

| 12              | 8                  | 195                                  | 60  | 40                 | 10                                  |

| 13              | 8                  | 195                                  | 80  | 20                 | 10                                  |

| 14              | 8                  | 195                                  | 70  | 40                 | 10                                  |

| 15              | 8                  | 195                                  | 90  | 40                 | 10                                  |

| 16              | 8                  | 195                                  | 70  | 35                 | 10                                  |

| 17              | 8                  | 195                                  | 70  | 50                 | 10                                  |

| 18              | 8                  | 195                                  | 70  | 60                 | 10                                  |

| 19              | 8                  | 195                                  | 70  | 30                 | 10                                  |

| 20              | 8                  | 195                                  | 80  | 50                 | 10                                  |

| 21              | 8                  | 195                                  | 80  | 60                 | 10                                  |

| 22              | 8                  | 195                                  | 80  | 30                 | 10                                  |

Tabla 3.b. Entrenamiento [Elaboración propia].

| Red Neuronal | Epochs | Performance (mse) | Peso<br>máximo |

|--------------|--------|-------------------|----------------|

| 6            | 500    | 0.0140425         | 19489          |

| 7            | 500    | 0.0130687         | 23500          |

| 8            | 100    | 0.0179081         | 1800           |

| 9            | 100    | 0.0181599         | 2140           |

| 10           | 100    | 0.017442          | 2536           |

| 11           | 100    | 0.0166598         | 1800           |

| 12           | 100    | 0.0181039         | 1815           |

| 13           | 100    | 0.0186173         | 2056           |

| 14           | 100    | 0.0153329         | 1788           |

| 15           | 100    | 0.0152742         | 2058           |

| 16           | 100    | 0.0160615         | 2264           |

| 17           | 100    | 0.0188552         | 3016           |

| 18           | 100    | 0.0172501         | 2400           |

| 19           | 100    | 0.0176996         | 2311           |

| 20           | 100    | 0.016802          | 1982           |

| 21           | 100    | 0.0184598         | 2058           |

| 22           | 100    | 0.0183491         | 1583           |

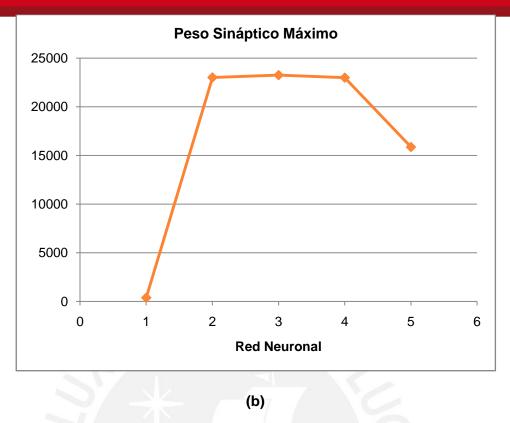

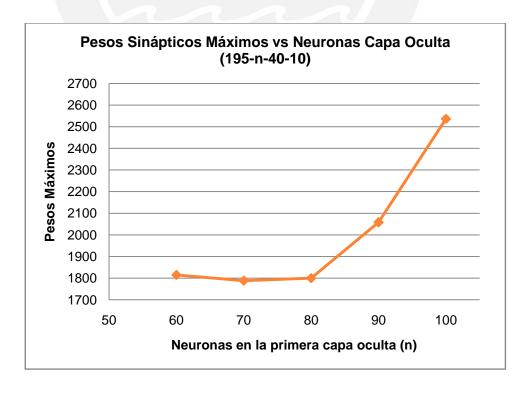

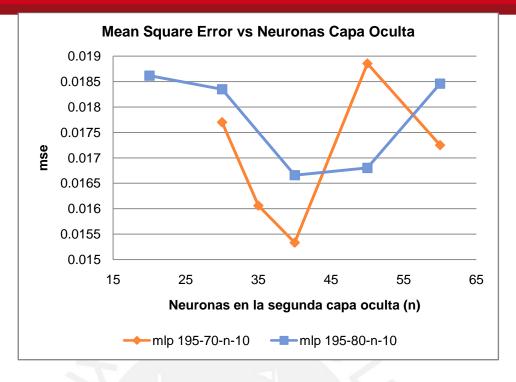

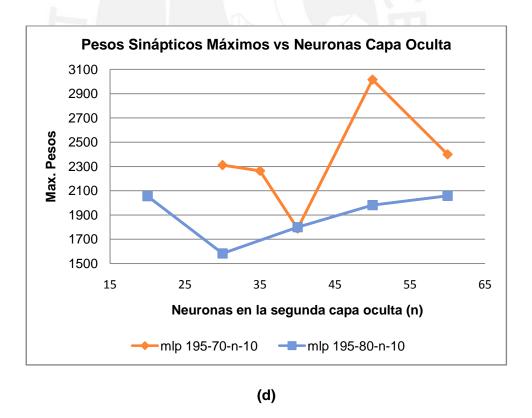

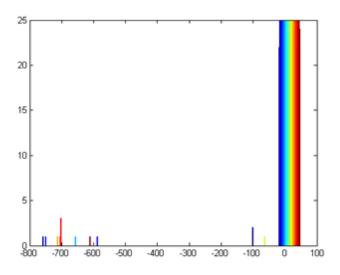

De la tabla presentada se extraen los siguientes gráficos mostrados en la figura 10. En ellos se observa la variación de los parámetros como son la magnitud absoluta de los pesos sinápticos y el error cuadrático medio frente a los cambios en la cantidad de neuronas en las capas ocultas.

(a)

(b)

(c)

Figura 10. Variaciones del error cuadrático medio y del peso sináptico máximo frente a cambios en la cantidad de neuronas en la primera capa oculta (a) y (b), y frente a cambios en la segunda capa oculta (c) y (d).

Podemos observar que para valores similares del error cuadrático medio a los de una sola capa oculta se tiene pesos máximos de mucha menor magnitud. Esto significa un avance, sin embargo, el costo esta en el aumento de neuronas a utilizar, así como de la cantidad de datos a procesar por la red neuronal.

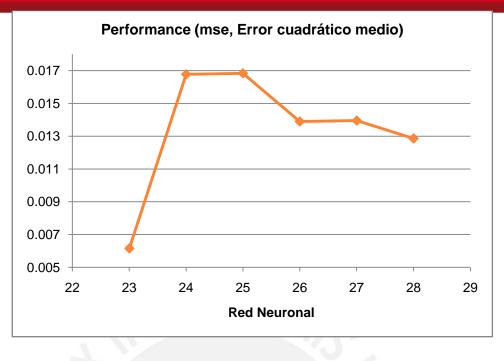

Por último, se procedió a entrenar redes neuronales con la siguiente forma de agrupación de bits. Se obtuvieron los siguientes resultados, los cuales son mostrados en la siguiente tabla 4 y en la figura 11.

Tabla 4.a. Características de las redes neuronales [Elaboración propia].

| Red<br>Neuronal | #bits /<br>entrada | Neuronas en la capa de entrada | Neuronas en la capa oculta | Neuronas en la<br>capa de salida |

|-----------------|--------------------|--------------------------------|----------------------------|----------------------------------|

| 23              | 4                  | 196                            | 50                         | 10                               |

| 24              | 16                 | 49                             | 15                         | 10                               |

| 25              | 16                 | 49                             | 20                         | 10                               |

| 26              | 16                 | 49                             | 25                         | 10                               |

| 27              | 16                 | 49                             | 30                         | 10                               |

| 28              | 16                 | 49                             | 35                         | 10                               |

Tabla 4.b. Entrenamiento [Elaboración propia].

| Red Neuronal | Epochs | Performance (mse) | Peso máximo |

|--------------|--------|-------------------|-------------|

| 23           | 100    | 0.00615423        | 877         |

| 24           | 100    | 0.0167706         | 753         |

| 25           | 100    | 0.01682905        | 747         |

| 26           | 100    | 0.013892          | 767         |

| 27           | 100    | 0.0139489         | 784         |

| 28           | 100    | 0.0128555         | 787         |

(a)