# PONTIFICIA UNIVERSIDAD CATÓLICA DEL PERÚ FACULTAD DE CIENCIAS E INGENIERÍA

Estudio y análisis de un circuito de monitoreo de carga residual para prótesis epirretinal

# TESIS PARA OPTAR EL TÍTULO PROFESIONAL DE INGENIERO ELECTRÓNICO

#### **AUTOR**

DIEGO ANTONIO RODRIGUEZ SANCHEZ

**ASESOR**

MANUEL ALEJANDRO MONGE OSORIO

CO – ASESOR

ERICK LEONARDO RAYGADA VARGAS

Lima, julio del 2019

#### **RESUMEN**

La retina es un tejido del ojo que se encarga de convertir la luz incidente en pulsos eléctricos para luego ser enviados al cerebro. Las células encargadas de dicha conversión son las células fotorreceptoras, estas hacen posible la visión.

La prótesis de retina se encarga de reemplazar la función que realizaban las células fotorreceptoras al recrear la sensación de visión por medio de la estimulación de las células neuronales sanas restantes en la retina por medio del envío de pulsos bifásicos a través de un arreglo de electrodos. No obstante, una de las grandes preocupaciones en cuanto a la estimulación de la prótesis de retina, es que cualquier exceso de acumulación de carga que supere los límites de seguridad tolerables puede causar daño a la retina.

A raíz de lo anterior mencionado, se procedió al estudio de un circuito cuyo objetivo es balancear la carga residual existente de forma controlada. Asimismo, se realizó un análisis de cada etapa del circuito: comparadores dinámicos, latch SR, parte de lógica y la etapa de compensación y se definió la estructura del circuito de seguridad. Por último, gracias a la herramienta *Analog Design Environment* de CADENCE se realizó simulaciones comprobando la funcionalidad de la solución planteada al dimensionar correctamente los transistores y definir una correcta corriente de compensación. Así pues, se obtuvo un circuito capaz de monitorear y corregir la carga del electrodo cuando ésta sale de los límites de seguridad y que presenta una baja disipación de potencia.

Primero, a Dios por sobre todas las cosas.

A mi madre Nieves, por su amor incondicional y por enseñarme a no rendirme hasta alcanzar mis metas.

A mi padre, Marco por demostrarme que no importa que tan dura sea la caída siempre hay que levantarse y seguir.

A mi hermana Claudia por ser un ejemplo a seguir y poder contar con ella para todo.

A mis asesores Manuel y Erick, por todo el apoyo brindado y por confiar en mí.

A Mario, por su incondicional ayuda y consejos.

# ÍNDICE GENERAL

| CAPÍTULO 1                                                                              | 1  |

|-----------------------------------------------------------------------------------------|----|

|                                                                                         |    |

| ASPECTOS GENERALES DE LA PRÓTESIS DE RETINA                                             | 1  |

| 1.1 Enfermedades degenerativas de la retina                                             | 1  |

| 1.1.1 La retina.                                                                        |    |

| 1.1.2 Retinitis pigmentaria y degeneración macular asociada a la edad                   |    |

| 1.2 Prótesis de retina                                                                  | 4  |

| 1.2.1 Concepto de prótesis de retina                                                    | 4  |

| 1.2.2 Tipos de prótesis de retina                                                       | 5  |

| 1.2.2 Tipos de prótesis de retina                                                       | 7  |

| 1.3 Desafíos de seguridad actuales existentes                                           | 8  |

| CAPÍTULO 2                                                                              | 0  |

| CAPITULO 2                                                                              | 9  |

| MÉTODOS DE CALIBRACIÓN PARA EL EQUILIBRIO DE CARGA                                      | 9  |

| 2.1 Modelo del electrodo-tejido de la retina                                            | 9  |

| 2.2 Concepto de carga residual                                                          | 10 |

| 2.2.1 Existencia de la carga residual                                                   | 10 |

| 2.2.2 Consecuencias de la carga residual                                                | 12 |

| 2.3 Métodos de monitoreo de carga residual existentes                                   | 13 |

| 2.3.1 Técnicas pasivas                                                                  |    |

| 2.3.1.1 Resistencia de descarga                                                         |    |

| 2.3.1.2 Capacitor de bloqueo.                                                           |    |

| 2.3.1.3 Cortocircuito del electrodo                                                     |    |

| 2.3.2 Técnicas activas                                                                  |    |

| 2.3.2.1 Inserción de corriente.                                                         |    |

| 2.3.2.2 Variación del pulso de estimulación                                             |    |

| 2.3.2.3 Inserción de pulsos de corriente con control de ancho de pulso de estimulación. |    |

| 2.4 Elección de topología                                                               | 26 |

| CAPÍTULO 3                                           | 28      |

|------------------------------------------------------|---------|

| ANÁLISIS DEL CIRCUITO DE MONITOREO DE CARGA RESI     | IDUAL28 |

| 3.1 Funcionamiento general del circuito de seguridad | 29      |

| 3.1.1 Voltaje del electrodo                          |         |

| 3.1.2 Comparador                                     | 32      |

| 3.1.3 Latch SR                                       |         |

| 3.1.4 Bloque de lógica                               | 35      |

| 3.1.5 Fuentes de corriente                           |         |

| 3.2 Análisis de los bloques del circuito             | 39      |

| 3.2.1 Comparador dinámico                            | 39      |

| 3.2.1.1 Análisis en pequeña señal del comparador     | 41      |

| 3.2.1.2 Capacitancias parásitas                      |         |

| 3.2.1.3 Consideraciones para el dimensionamiento     | 50      |

| 3.2.2 Latch SR                                       |         |

| 3.2.3 Bloque de lógica                               | 53      |

| 3.2.4 Fuentes de corriente                           |         |

| CAPÍTULO 4                                           | 56      |

| SIMULACIONES Y RESULTADOS                            | 56      |

|                                                      |         |

| 4.1 Simulaciones                                     | 56      |

| 4.1.1 Carga del electrodo                            | 56      |

| 4.1.2 Comparador dinámico                            | 57      |

| 4.1.3 Latch SR                                       | 61      |

| 4.1.4 Bloque de lógica                               | 64      |

| 4.1.5 Compensación                                   |         |

| 4.1.6 Análisis de Potencia.                          | 69      |

| 4.1.7 Circuito electrodo tejido                      | 73      |

| CONCLUSIONES                                         | 79      |

| RECOMENDACIONES                                      | 80      |

| BIBLIOGRAFÍA                                         | 81      |

# ÍNDICE DE FIGURAS

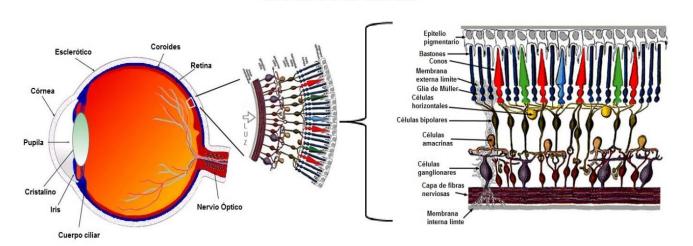

| Figura 1.1 El ojo humano y estructura de la retina [3].                                                                   | 1   |

|---------------------------------------------------------------------------------------------------------------------------|-----|

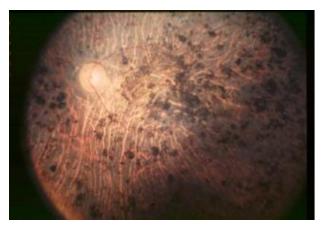

| Figura 1.2 Fondo de ojo humano con retinitis pigmentaria [5][5]                                                           | 3   |

| Figura 1.3 Fondo de ojo sano y con DMAE. Círculo negro indica la mácula: ojo sano, DMAE seca con                          |     |

| despigmentación, DMAE húmeda con los vasos sanguíneos en la retina [7].                                                   | 4   |

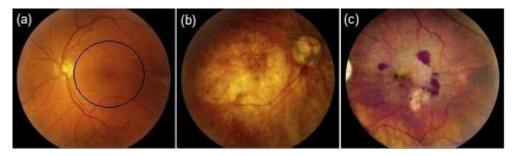

| Figura 1.4 Prótesis visuales. (a) Prótesis cortical, la corteza visual [10]. (b) Prótesis de nervio óptico [8]. (c) Próte | sis |

| de retina [12]                                                                                                            | 5   |

| Figura 1.5 Ubicación de los implantes en los diferentes tipos de prótesis [12]                                            | 6   |

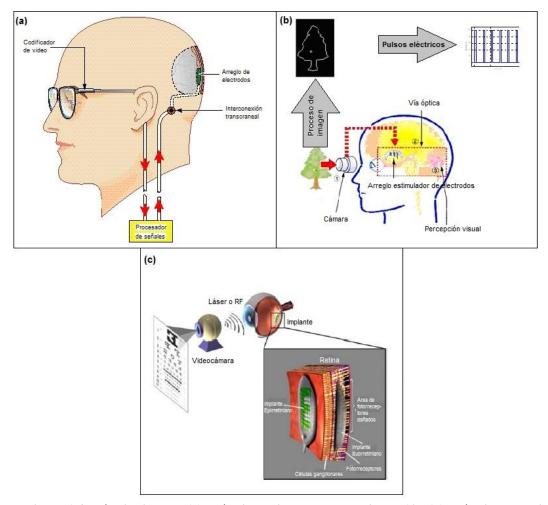

| Figura 1.6 Arquitectura de la prótesis de retina.                                                                         | 8   |

| Figura 2.1 Modelo de interfaz electrodo-electrolito [17]                                                                  |     |

| Figura 2.2 Estimulador [18]                                                                                               | 11  |

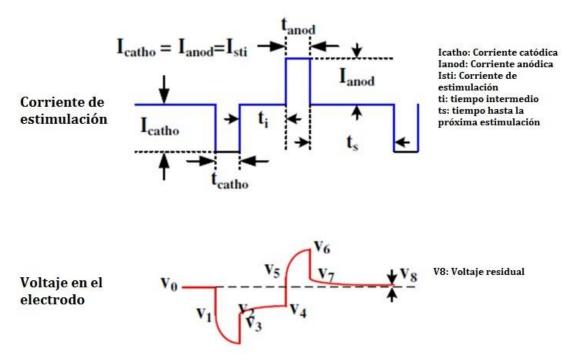

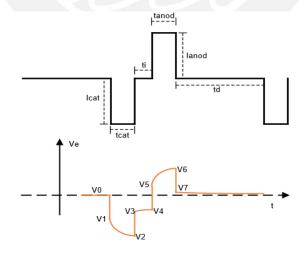

| Figura 2.3 Forma de onda de la corriente de estimulación y del voltaje en el electrodo [19]                               | 12  |

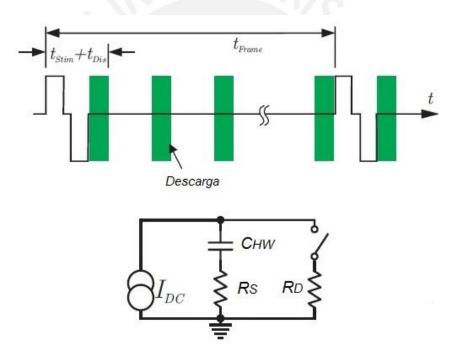

| Figura 2.4 Gráfico de ciclos de descarga y circuito con resistencia de descarga por conmutación [20]                      | 14  |

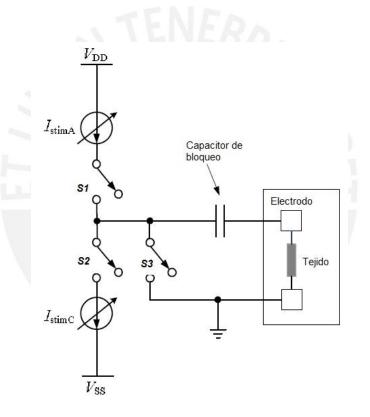

| Figura 2.5 Estimulador bifásico con capacitor de bloqueo conectado al electrodo-tejido [21]                               | 15  |

| Figura 2.6 Circuito de descarga [22]                                                                                      | 16  |

| Figura 2.7 Balance de carga por medio de inserción de pulsos [18]                                                         | 18  |

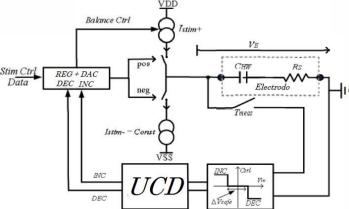

| Figura 2.8 Circuito de balance de carga para inserción de pulso [23]                                                      | 19  |

| Figura 2.9 Circuito de balance de carga con corriente de offset [18]                                                      | 20  |

| Figura 2.10 Formas de onda de un balance de carga permanente [18]                                                         | 20  |

| Figura 2.11 Diagrama del sistema de balanceo de carga por medio del control de amplitud de pulso [17]                     | 21  |

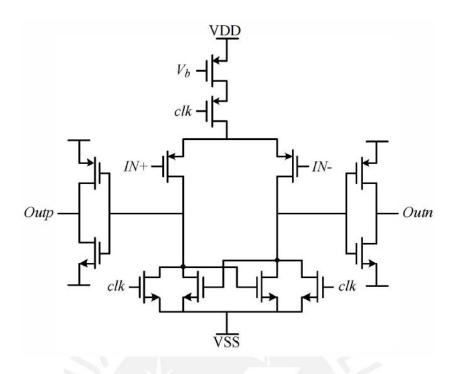

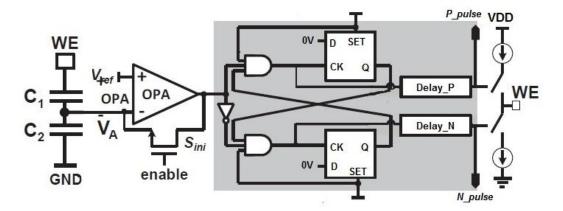

| Figura 2.12 Circuito comparador dinámico [17]                                                                             | 22  |

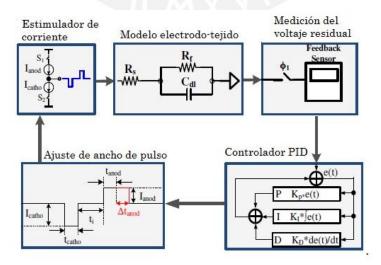

| Figura 2.13 Diagrama del sistema de balanceo de carga por medio del control del ancho de pulso [19]                       | 23  |

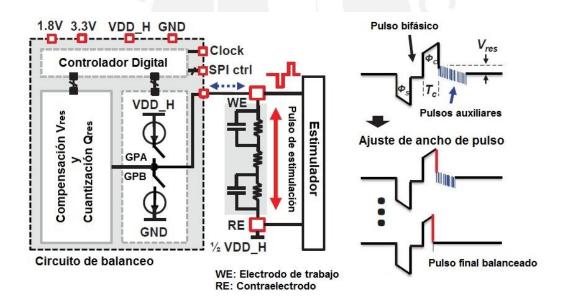

| Figura 2.14 Arquitectura del sistema de balanceo de carga y formas de onda del voltaje residual [24]                      | 24  |

| Figura 2.15 Diagrama del circuito del bloque de compensación y cuantización [24]                                          | 25  |

| Figura 3.1 Diagrama de bloques del circuito de seguridad                                                                  | 28  |

| Figura 3.2 Voltaje del electrodo vs tiempo                                                                                | 29  |

| Figura 3.3 Símbolo del comparador                                                                                         | 32  |

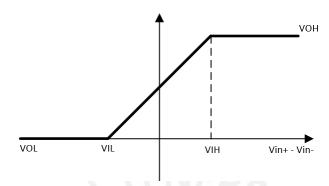

| Figura 3.4 Modelo de primer orden de un comparador                                                                        | 33  |

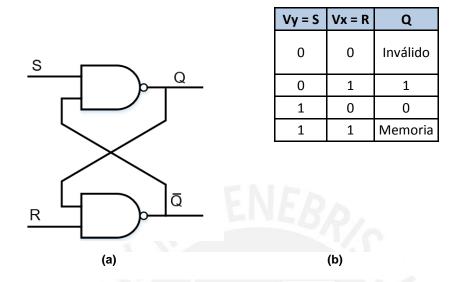

| Figura 3.5 (a) Latch SR de compuertas NAND. (b) Tabla de verdad del latch SR                                              | 35  |

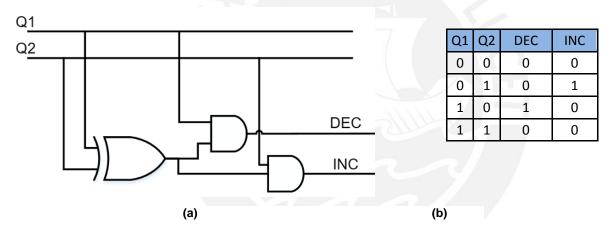

| Figura 3.6 (a) Circuito de lógica. (b) Tabla de verdad del circuito de lógica                                             | 36  |

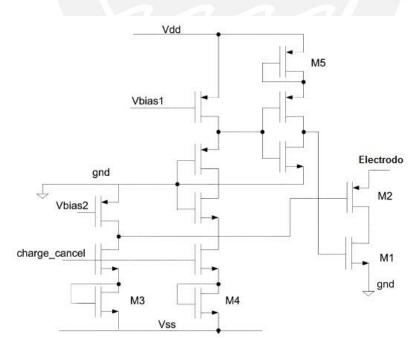

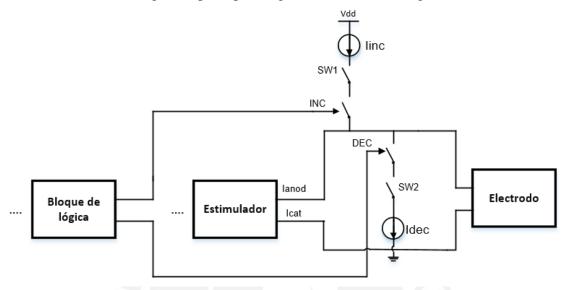

| Figura 3.7 Fuentes de corriente de compensación                                                                           | 37  |

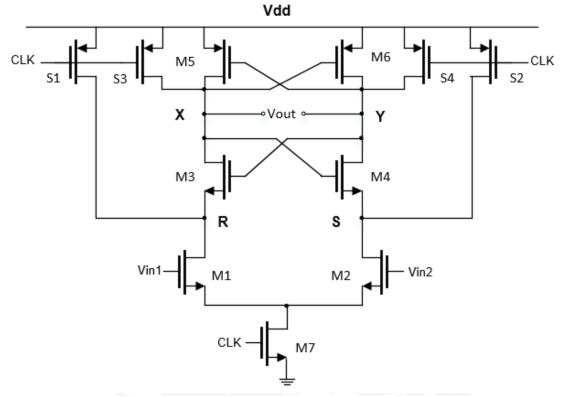

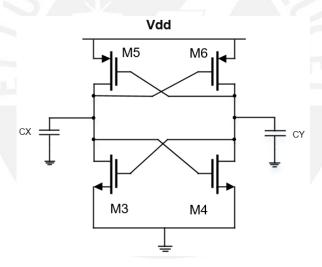

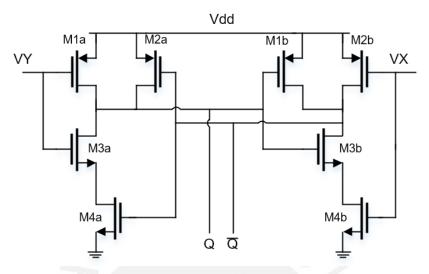

| Figura 3.8 Comparador dinámico StrongARM Latch [26]                                                                       | 40  |

| Figura 3.9 Comparador dinámico cuando el CLK está en baja                                                                 | 40  |

| Figura 3.10 Circuito en pequeña señal del comparador dinámico en el momento de la conmutación de CLK a alta               | 41  |

| Figura 3.11 Circuito en pequeña señal al con los transistores M3 y M4 en saturación                                       | 44  |

| Figura 3.12 Circuito del comparador en la etapa de realimentación positiva                                                | 46  |

| Figura 3.13 Circuito en pequeña señal del comparador en la etapa de realimentación positiva                               | 47  |

| Figura 3.14 Circuito en pequeña señal de los transistores M3 y M5                                                         | 47  |

| Figura 3.15 Representación de las capacitancias parásitas internas de un transistor NMOS cuyo substrato está              |     |

| conectado a GND                                                                                                           | 49  |

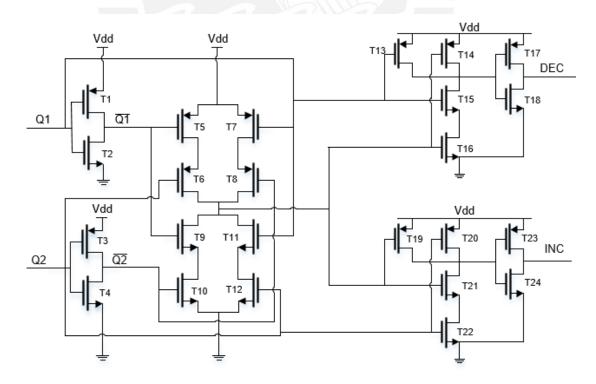

| Figura 3.16 Diagrama esquemático del latch SR                                                                             | 53  |

| Figura 3.17 Diagrama esquemático del bloque de lógica                                                                     | 54  |

| Figura 3.18 Fuentes de corriente para la compensación del pulso anódico                                                   | 55  |

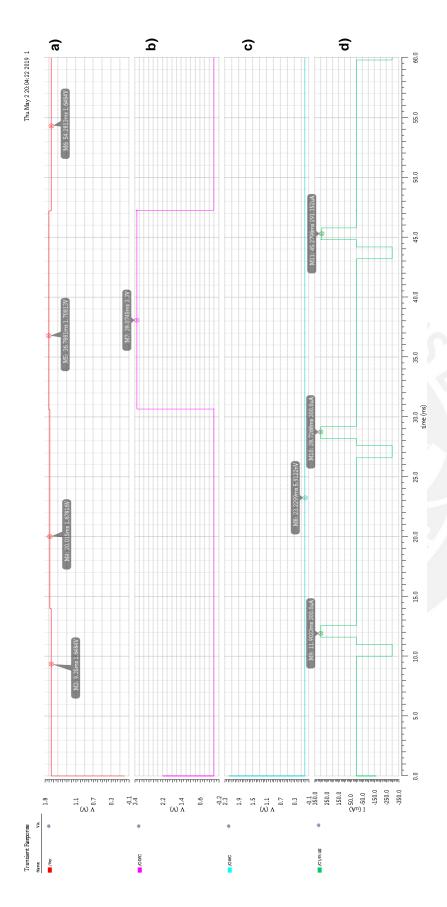

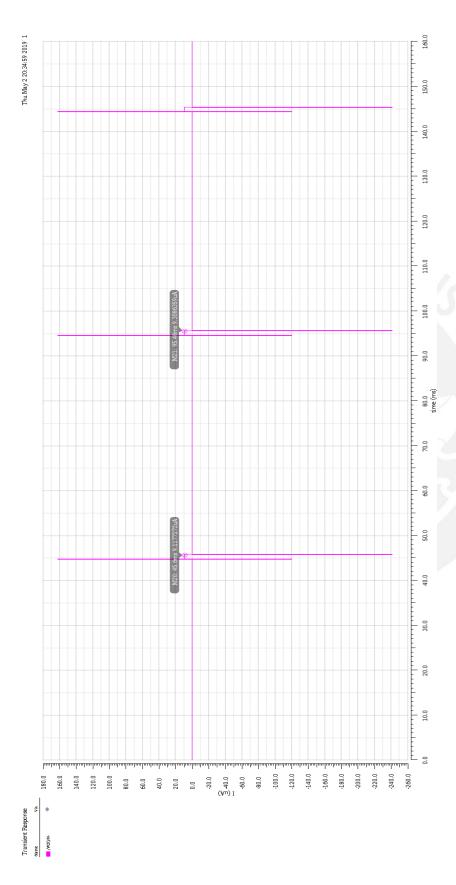

| Figura 4.1 Carga del electrodo al existir 1% de <i>mismatch</i> en los pulsos de estimulación                             | 57  |

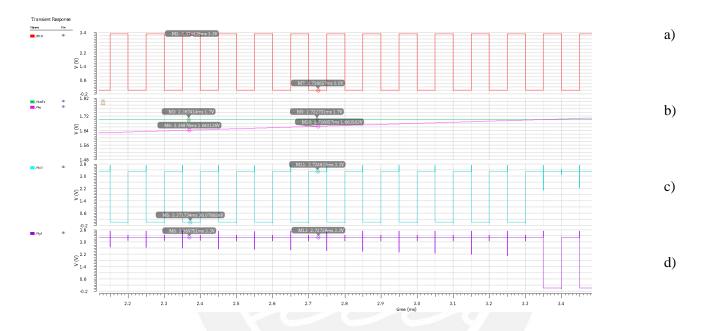

| Figura 4.2 a) Señal de reloj CLK b) Señal de referencia Vin1 (verde) y voltaje del electrodo Vin2 (guinda) c) Volt | taje       |

|--------------------------------------------------------------------------------------------------------------------|------------|

| de salida del nodo X. d) Voltaje de salida del nodo Y                                                              | 58         |

| Figura 4.3 a) Señal de reloj CLK b) Señal de referencia Vin1 (verde) y voltaje del electrodo Vin2 (guinda) c) Volt | taje       |

| de salida del nodo X. d) Voltaje de salida del nodo Y                                                              | 59         |

| Figura 4.4 Circuito del comparador dinámico                                                                        | 60         |

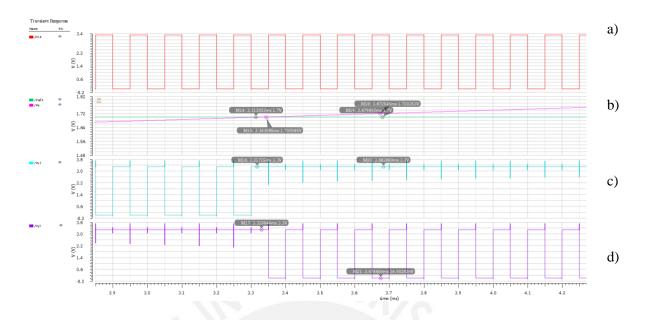

| Figura 4.5 (a) Voltaje en el nodo X (b) Voltaje en el nodo Y (c) Q1, salida del latch SR1                          |            |

| (d) Q2, salida del latch SR2                                                                                       | 62         |

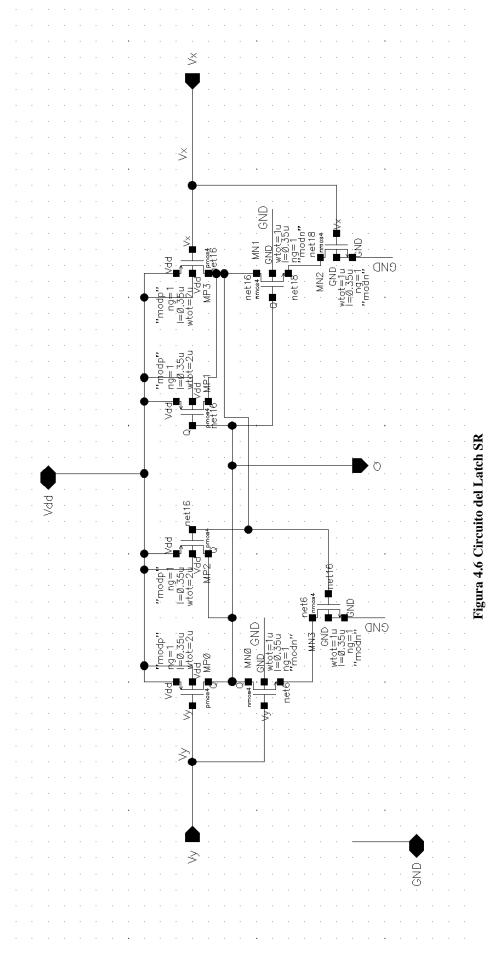

| Figura 4.6 Circuito del Latch SR                                                                                   | .63        |

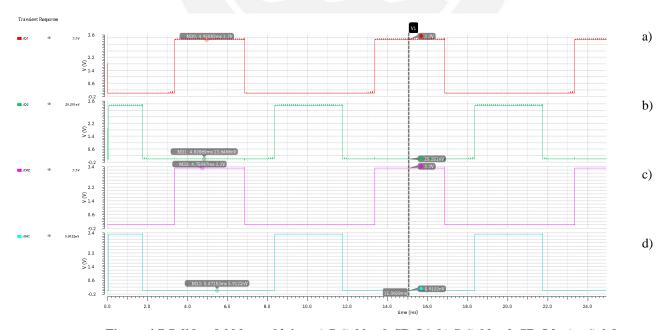

| Figura 4.7 Salidas del bloque lógico. a) Señal latch SR Q1, b) Señal latch SR Q2, c) señal de decremento, d) señal | l de       |

| incremento                                                                                                         | 64         |

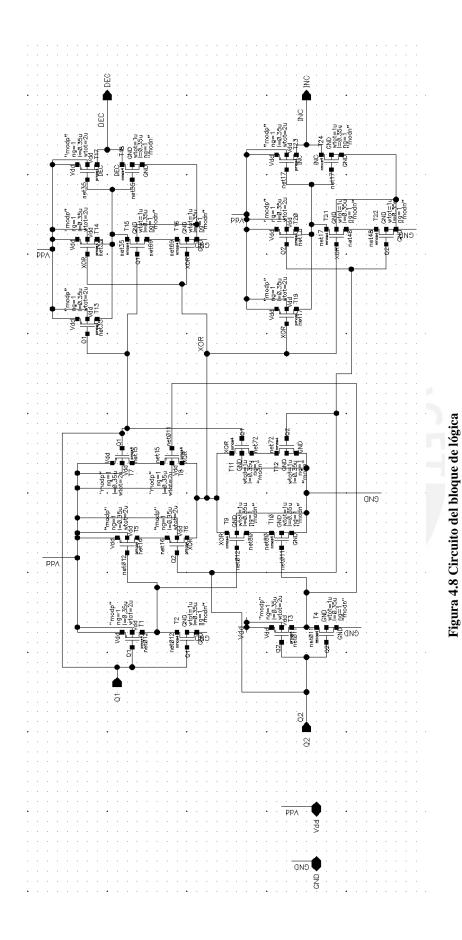

| Figura 4.8 Circuito del bloque de lógica                                                                           | 67         |

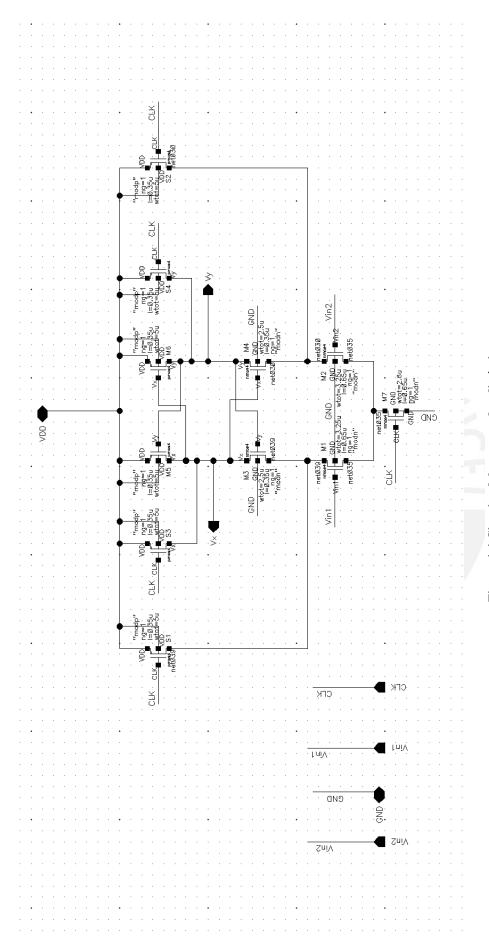

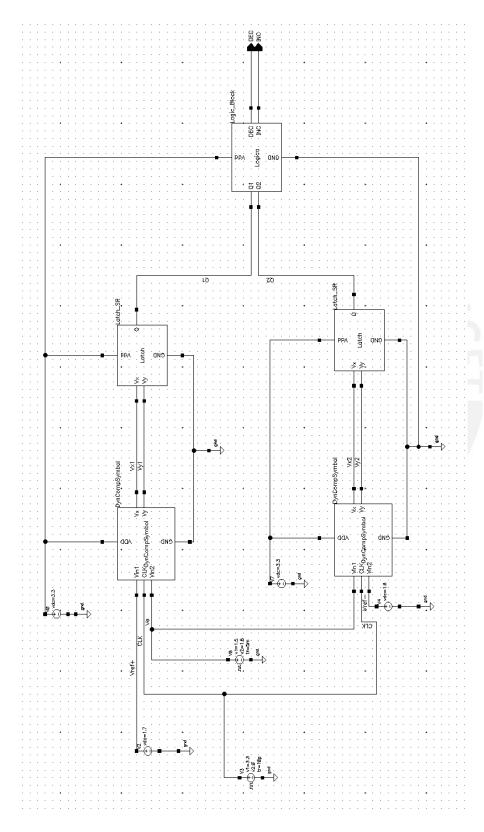

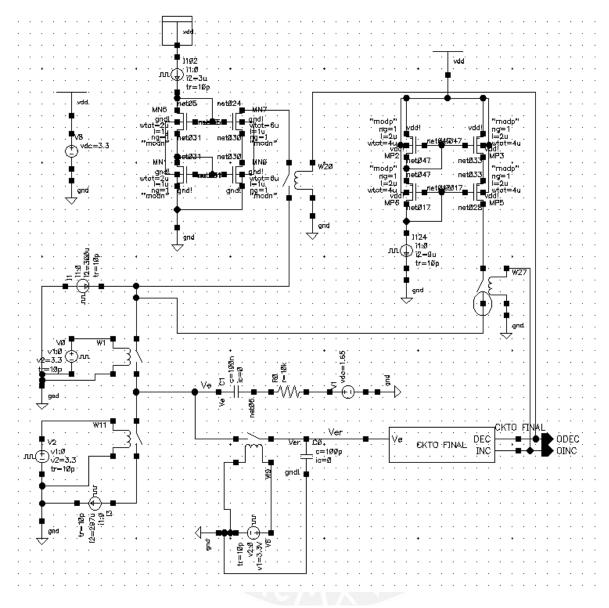

| Figura 4.9 Circuito total, incluye comparadores dinámicos, latch SR y bloque de lógica                             | 68         |

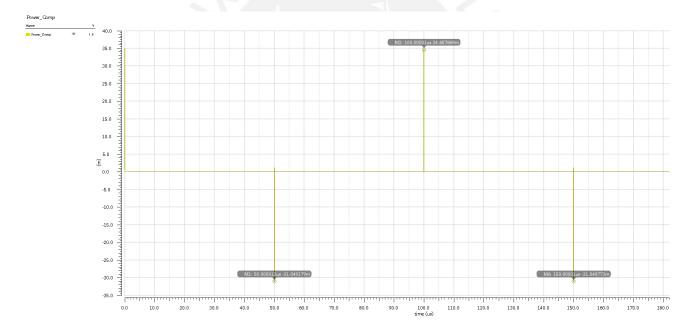

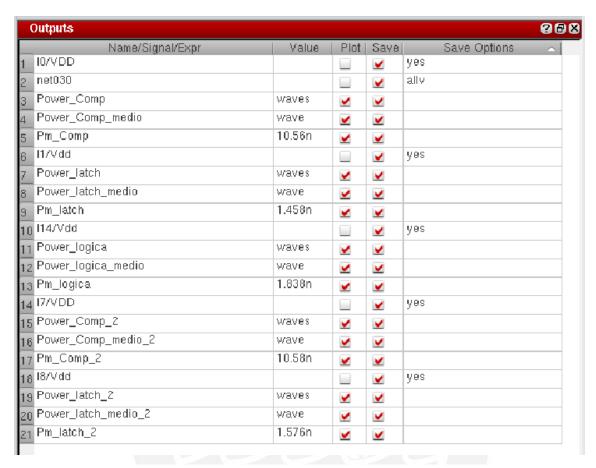

| Figura 4.10 Señal Power_Comp, producto de tensión por corriente del comparador dinámico                            | .69        |

| Figura 4.11 Señal Power_latch, producto de tensión por corriente del latch SR                                      | 70         |

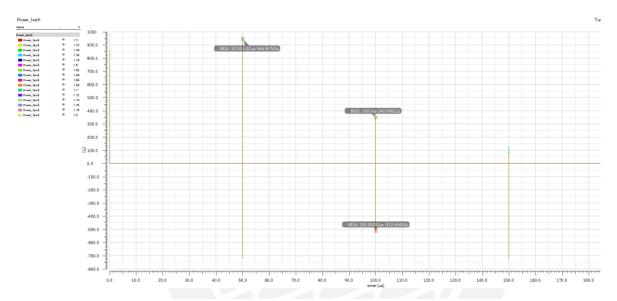

| Figura 4.12 Señal Power_logica, producto de tensión por corriente del bloque de lógica                             | 70         |

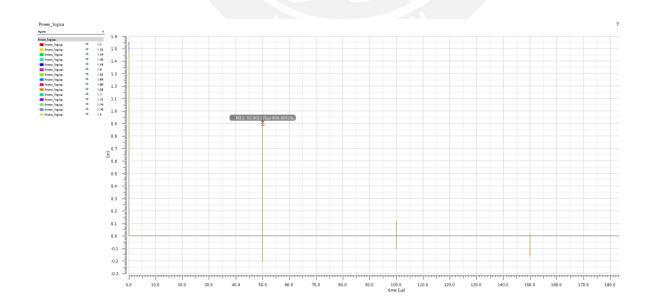

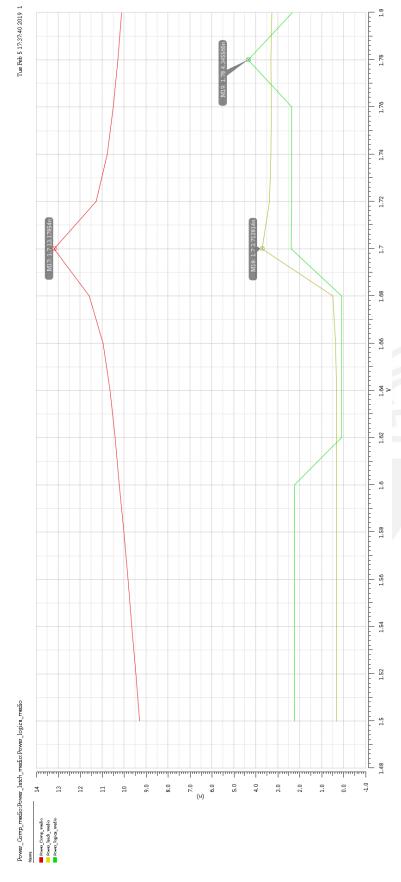

| Figura 4.13 Potencia del comparador dinámico (rojo), latch SR (amarillo) y bloque de lógica (verde) entre 45us y   |            |

| 160us                                                                                                              | <b>7</b> 1 |

| Figura 4.14 Potencia consumida de cada circuito analizado                                                          |            |

| Figura 4.15 Circuito final para la simulación                                                                      | 74         |

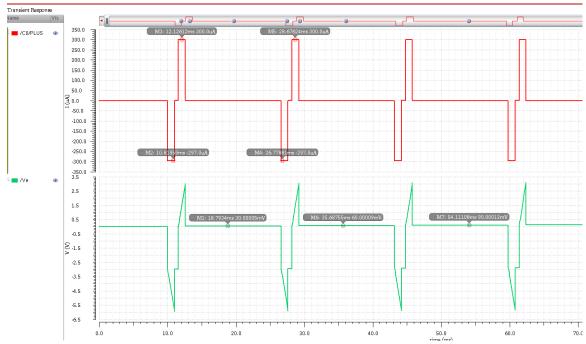

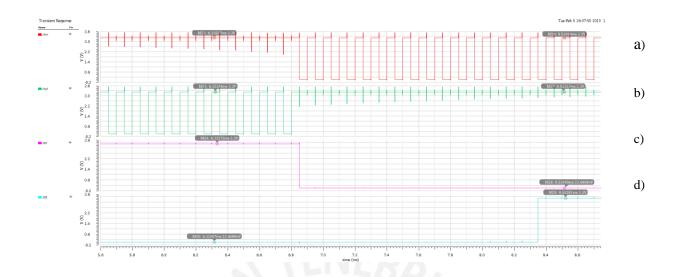

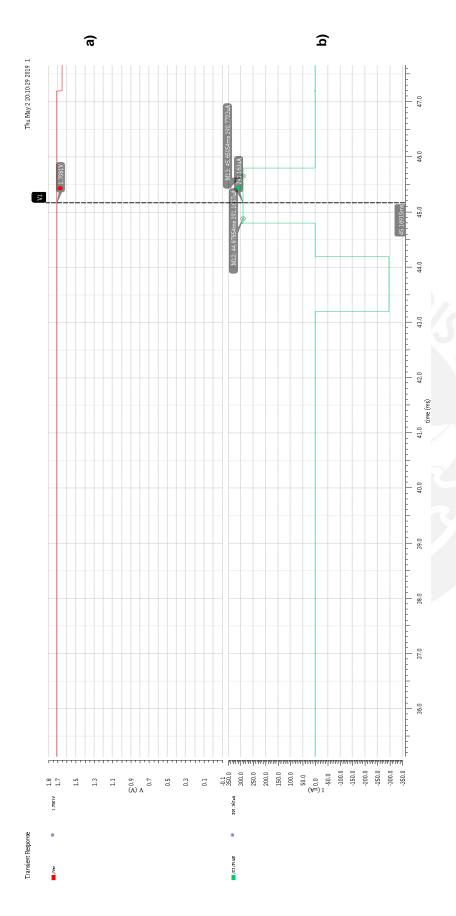

| Figura 4.16 a) Voltaje del electrodo. b) Señal de decremento. c) Señal de incremento. d) Pulsos de estimulación .  | 70         |

| Figura 4.17 a) Voltaje del electrodo. b) Pulso de estimulación con amplitud del pulso anódico corregido            | 77         |

| Figura 4.18 Pulso de compensación para disminuir la amplitud del pulso anódico                                     | 78         |

# ÍNDICE DE TABLAS

| Tabla 4.1 Dimensiones de transistores del comparador dinámico | .61 |

|---------------------------------------------------------------|-----|

| Tabla 4.2 Dimensiones de transistores del Latch SR            |     |

| Tabla 4 3 Comparación de disipación de potencia               |     |

# **CAPÍTULO 1**

# ASPECTOS GENERALES DE LA PRÓTESIS DE RETINA

#### 1.1 Enfermedades degenerativas de la retina

#### 1.1.1 La retina

La retina es el tejido transparente y sensible a la luz que se encuentra en la parte posterior interior de la pared del ojo. Es la encargada de convertir la información recibida a través de los ojos (imágenes) en señales eléctricas para su posterior envío al cerebro. Como se observa en la figura 1.1, la retina consta de una estructura neuronal multicapa de aproximadamente 200µm de espesor [1]. Primero, se encuentra el epitelio pigmentario retiniano que se encarga de absorber la luz. Segundo, están los fotorreceptores (bastones y conos) que transforman la luz incidente en impulsos eléctricos, proceso llamado foto-transducción. A partir de aquí, son las células inter neuronales que conectarán a los fotorreceptores con las células ganglionares [2]. Estas últimas son quienes envían las señales eléctricas al cerebro a través del nervio óptico.

Figura 1.1 El ojo humano y estructura de la retina [3].

#### 1.1.2 Retinitis pigmentaria y degeneración macular asociada a la edad

La ceguera puede ser causada por el daño de partes del ojo que reflejan la luz en la retina; por ejemplo, la córnea y el cristalino, o la atrofia del nervio óptico que es el medio por el cual se transmite el impulso eléctrico al cerebro. Estos efectos se presentan en enfermedades como las cataratas y el glaucoma. Por otro lado, si las células de la retina, encargadas de transformar la luz en señales eléctricas y de transmitirlas, son dañadas; entonces también puede existir una pérdida de visión. Las enfermedades degenerativas de la retina son las causantes del daño a las células antes mencionadas.

Las enfermedades degenerativas de la retina más comunes y significativas son la retinitis pigmentaria (RP) y la degeneración macular asociada a la edad (DMAE). La retinitis pigmentaria es un grupo de enfermedades de origen genético que se caracterizan por la pérdida de las células fotorreceptores y el depósito del pigmento de retina como en la figura 1.2. Inicialmente existe una pérdida de la visión nocturna y periférica debido a que las primeras células en degenerarse son los bastones, responsables de esa visión. Con el paso del tiempo, se pierde la visión diurna y central como resultado de la muerte de las células conos. Este proceso puede tener una evolución rápida o un avance lento que no conduce a la ceguera, mas la visión ya está comprometida. Asimismo, se puede producir o no la aparición de depósitos de pigmento (manchas oscuras) en el fondo del ojo; no obstante la cantidad de manchas no tiene relación con la gravedad de la enfermedad. Actualmente, no existe cura o tratamiento que pueda detener el desarrollo de esta enfermedad; sin embargo existen tratamientos para poder ralentizar el proceso degenerativo [5].

La degeneración macular asociada a la edad (DMAE) es una enfermedad lenta y progresiva que afecta a la mácula. La mácula es un área pequeña de la retina ubicada en la parte central que consiste de una estructura celular (fotorreceptores, células gliales, vasculatura retiniana) y el

epitelio pigmentario retiniano. Asimismo, en la parte central de la mácula se encuentra una gran cantidad de conos fotorreceptores (fóvea). Esta enfermedad puede ser distinguida por tres etapas: DMAE temprana, intermedia y tardía. Las dos primeras etapas se caracterizan por la presencia de drusas blandas entre el epitelio pigmentario retiniano y la membrana de Bruch, una fina capa de matriz extracelular [6]. Las drusas son unos depósitos amarillos compuestos de lípidos clasificadas en dos tipos: blandas y duras. Las drusas duras pueden o no causar problemas en la visión mientras las blandas son las que aumentan el riesgo de desarrollar DMAE [4]. La etapa más severa es la tardía la cual se divide a su vez en dos tipos de DMAE: seca o atrófica y húmeda o neovascular. La DMAE seca es causada por el envejecimiento y adelgazamiento de los tejidos de la mácula. La formación de drusas se da por debajo de la retina. En cambio, la DMAE húmeda comienza con la formación de vasos sanguíneos a partir de la coroides que luego llegan a la retina [7]. Con todo esto, esta enfermedad puede causar cambios en la pigmentación del epitelio pigmentario retiniano y la muerte de sus células (ver figura 1.3), si es la etapa temprana o intermedia. Del mismo modo, en la DMAE seca o atrófica existe una pérdida de la coroides, del epitelio pigmentario retiniano y la retina neurosensorial la cual contiene a los fotorreceptores. La DMAE húmeda genera una acumulación de fluido ya que los vasos sanguíneos formados son débiles y eventualmente producen un sangrado interno [6].

Figura 1.2 Fondo de ojo humano con retinitis pigmentaria [5].

Figura 1.3 Fondo de ojo sano y con DMAE. Círculo negro indica la mácula. (a) ojo sano, (b) DMAE seca con despigmentación, (c) DMAE húmeda con los vasos sanguíneos en la retina [7].

#### 1.2 Prótesis de retina

## 1.2.1 Concepto de prótesis de retina

La prótesis de retina se encarga de reemplazar la función que realizaban las células fotorreceptoras, ahora dañadas por las enfermedades antes vistas, y así poder crear la sensación de visión al estimular las células neuronales sanas restantes en la retina. Existen estudios de otras prótesis visuales como las implantadas en la corteza visual y nervio óptico con la misma funcionalidad como se muestra en la figura 1.4 [8] [9]; sin embargo, estas no son objeto del presente estudio. La prótesis de retina es capaz de estimular eléctricamente la retina mediante el envío de pulsos eléctricos a través de un arreglo de electrodos. Por ello, enviando los patrones correctos de impulsos se pueden crear manchas luminosas conocidas como el fenómeno del fosfeno. Así el paciente es capaz de identificar las formas de objetos y dependiendo de la prótesis, restaurar parcialmente su visión. Parámetros como la disipación de potencia, dimensiones y resolución son importantes a considerar al momento de diseñar la prótesis.

Figura 1.4 Prótesis visuales. (a) Prótesis cortical, la corteza visual [10]. (b) Prótesis de nervio óptico [8]. (c) Prótesis de retina [12].

# 1.2.2 Tipos de prótesis de retina

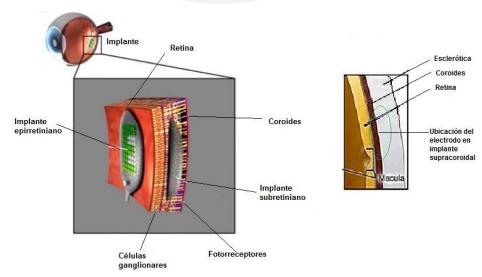

Existen tres diferentes enfoques de prótesis de retina vinculadas con la posición del arreglo de electrodos: epirretinal, subretiniana y supracoroidal. La posición del arreglo es mostrada en la figura 1.5.

Primero, la prótesis epirretinal es aquella en donde el arreglo de electrodos es colocado en la superficie interior de la retina. Este será el tipo en el cual estará enfocada la presente tesis. Una característica de acuerdo a la posición del arreglo de electrodos es que asegura un contacto

directo y la estimulación de las células ganglionares. Mayor información respecto a este tipo de prótesis puede ser encontrada en [11]. Algunos grupos de investigación han desarrollado esta prótesis de retina como lo son *Intelligent Medical Implants* (IMI), *Epi-Ret Consortium* (Epi-Ret) y *Second Sight* con el Argus I y el Argus II [12] [13].

Segundo, la prótesis subretiniana se encuentra localizada entre la retina y la coroides. Específicamente, la prótesis se coloca en el lugar en donde están los fotorreceptores degenerados. Esto produce una serie de ventajas y desventajas; por ejemplo, el hecho que se encuentre entre la retina y la coroides hace que aproveche todo el proceso neuronal normal que sucede en las multicapas intermedias. Si se desea saber más sobre las ventajas y desventajas, puede ser consultado en [11]. Existen dispositivos que aplican el enfoque subretiniano como el presentado en [14].

Por último, el tipo supracoroidal consiste en ubicar el arreglo de electrodos en un corte que se realiza al esclerótico, capa exterior del ojo, y dirigir los contactos de los electrodos a la coroides. En este caso, la distancia entre el arreglo de electrodos y la retina es mayor y por ello el umbral de estimulación aumenta; sin embargo, ha habido estudios en los que se ha logrado una correcta estimulación [12].

Figura 1.5 Ubicación de los implantes en los diferentes tipos de prótesis [12].

#### 1.2.3 Funcionamiento de la prótesis

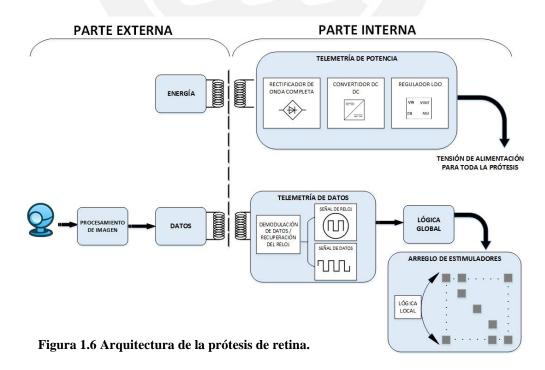

De acuerdo a lo mencionado anteriormente, la presente tesis se basará en el tipo de prótesis epirretinal completamente intraocular. El funcionamiento de la prótesis está basado en los estudios previos realizados en [15]. El sistema cuenta con dos partes: parte externa y parte interna, cada una con diferentes etapas como se puede observar en la figura 1.6. La parte extraocular consiste en una videocámara para la recepción de imágenes y procesamiento de las mismas. Esta información al igual que la energía necesaria para el chip es enviada inalámbricamente a la parte intraocular por medio de radiofrecuencia a través de una bobina de transmisión para potencia y otra para datos. Del mismo modo, la parte intraocular tiene unas bobinas de recepción para potencia y datos. Luego ambas señales deben ser recuperadas de forma independiente dentro del chip, por eso cuenta con un bloque de telemetría de potencia y uno de datos. El primero, recibirá la señal de potencia de entrada y la rectificará a través de un rectificador de onda completa, para luego por medio de convertidores DC-DC y de reguladores de baja caída de tensión (LDO) obtener salidas de tensión regulada. Con esto se generarán las señales de alimentación necesarias para el circuito de estimulación. Por otra parte, el bloque de telemetría de datos recibe la información inalámbricamente para luego ser demodulada; por ejemplo, mediante modulación PSK. Asimismo, en este bloque se recupera la señal de reloj con la cual los circuitos trabajarán. La información demodulada es recibida por el bloque de lógica de control global. Por último, está el arreglo de estimuladores que contiene un bloque de lógica local que se encarga de recibir la información proveniente del bloque de lógica global. Con esto se controla la estimulación de los electrodos ubicados sobre la retina.

### 1.3 Desafíos de seguridad actuales existentes

La estimulación neuronal es lograda gracias a la transferencia de carga a través de un electrodo como se explicó anteriormente. Sin embargo, una de las grandes preocupaciones en cuanto a la estimulación de la prótesis de retina, es que cualquier exceso de acumulación de carga que supere los límites de seguridad tolerables puede causar daño a la retina, entendiéndose como la descomposición de una sustancia inmersa en una disolución por acción de la corriente eléctrica continua. Esto deterioraría el arreglo de electrodo corroyéndolo y a su vez podría causar algún daño al tejido sano de la retina. Sumado a esto, es necesario tener en consideración que el área existente es limitada y se debe disponer de la mayor cantidad de energía necesaria, así como asegurar una operación segura para evitar estimulación sin control. En aras de la salud del paciente y conservación en buen estado de la prótesis, existen métodos que buscan corregir esto con el propósito de ofrecer una mejor experiencia con la prótesis de retina. La existencia de la carga residual y efectos, así como los diferentes métodos y comparaciones entre ellos serán presentados en el siguiente capítulo.

## Capítulo 2

# MÉTODOS DE CALIBRACIÓN PARA EL EQUILIBRIO DE CARGA

#### 2.1 Modelo del electrodo-tejido de la retina

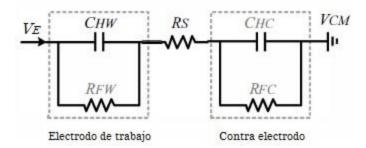

Cuando se coloca un electrodo de metal en un medio fisiológico como un fluido extracelular (electrolito) se genera un interfaz entre estos dos componentes. Anteriormente se mencionó que la estimulación de la retina se da a través de impulsos eléctricos, se entrega carga. El proceso que ocurre en la interfaz es la transducción del transporte de carga de los electrones en el electrodo a los iones en el electrolito. Al pasar corriente del electrodo al electrolito, ocurre un cambio en el potencial eléctrico y se genera un campo eléctrico en el interfaz. Hay dos maneras de transferir carga en el interfaz electrodo-electrolito, por medio de una reacción no farádica o bien una reacción farádica. Primero, la transferencia de carga no farádica se representa con una capacitancia llamada capacitancia de doble capa (CHW y CHC), esta modela la habilidad del electrodo para generar un flujo de carga en el electrolito sin la necesidad de transferir electrones. Segundo, la transferencia de carga farádica se representa por medio de una resistencia en paralelo a la capacitancia de doble capa, resistencia farádica (RFW y RFC). La resistencia farádica representa los procesos de reducción y oxidación donde ocurre transferencia de electrones entre electrodo y electrolito. Tercero, se utiliza una impedancia resistiva (RS) para representar al electrolito, el tejido en este caso [16].

En la figura 2.1 se observan dos electrodos, electrodo de trabajo y contra electrodo, los cuales cumplen la función de recibir e inyectar la carga respectivamente. Para aplicaciones con estimulación monopolar, el contra electrodo es un electrodo de referencia muy grande. Por otro lado, las aplicaciones en las que se utiliza estimulación bipolar como es el caso de la prótesis de

Figura 2.1 Modelo de interfaz electrodo-electrolito [17].

retina, el contra electrodo se representa como un segundo electrodo de estimulación. Por último, debido a la limitación de área en la prótesis de retina; la resistencia farádica no es modelada ya que su valor es mucho mayor comparado a la impedancia resistiva del tejido. Así la resistencia farádica no es considerada y solo la capacitancia de doble capa y la impedancia del tejido son tomadas en cuenta para una operación segura.

## 2.2 Concepto de carga residual

### 2.2.1 Existencia de la carga residual

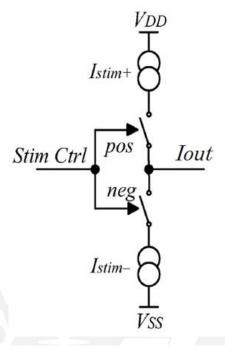

Para poder entender el porqué de la carga residual, se debe conocer en primer lugar como es que se da la estimulación de los electrodos. En la figura 2.2 se representa al estimulador, el cual consta de dos fuentes de corriente y dos interruptores. Así, de acuerdo a la información que reciba del bloque de lógica local, la señal "Stim Ctrl", cerrará el interruptor adecuado y dará paso a la corriente de estimulación anódica o catódica. Como se mencionó anteriormente, al solo trabajar con la capacitancia de doble capa, se está modelando un comportamiento no farádico en donde la carga inyectada del electrodo al electrolito y almacenada en la capacitancia es contrarrestada al invertir la corriente.

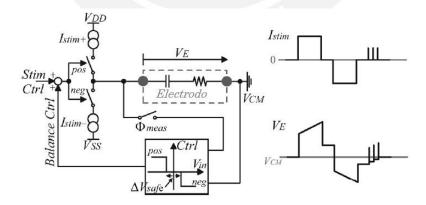

Figura 2.2 Estimulador [18].

Con todo esto, se define como carga residual a la carga existente en el tejido luego de la estimulación. Dicha carga es producida debido al *mismatch* de corrientes; es decir, la no coincidencia en las intensidades de los pulsos de estimulación. En la figura 2.3 se presenta la forma de onda de la corriente de estimulación y cómo se comporta el potencial en el electrodo. Inicialmente, el voltaje en el electrodo es cero hasta que se reciba el primer pulso de la corriente de estimulación; en este ejemplo un pulso catódico. Con esto, la caída de tensión en la impedancia del tejido (RS) hace que el voltaje adquiera un valor V1. La corriente hará que el condensador comience a cargarse tendiendo a un valor V2 como se observa en la figura. Al finalizar el pulso, la caída de voltaje en la impedancia del tejido vuelve a ser cero y por ello el voltaje del electrodo cambia a un valor V3. Durante el tiempo intermedio entre los pulsos, debido a la fuga de carga, la carga del condensador comenzará a disminuir a V4. Cuando el pulso anódico llegue desde el estimulador, el proceso se repite de forma inversa. Finalmente, existirá

una carga residual luego del pulso anódico debido al *mismatch*; esta carga se reducirá nuevamente debido a las fugas. Sin embargo; esta no llegará a cero y pese a que en la primera estimulación pueda ser muy pequeña existe un riesgo creciente conforme va aumentando esta carga residual.

Figura 2.3 Forma de onda de la corriente de estimulación y del voltaje en el electrodo [19].

## 2.2.2 Consecuencias de la carga residual

Así como una mala estimulación puede causar efectos nocivos, la acumulación de la carga residual también. De acuerdo a la figura 2.3, existe una pequeña carga residual luego de cada estimulación; sin embargo, esta pequeña cantidad de carga puede ir aumentando con el paso del tiempo si no es controlada. Uno de los objetivos de la prótesis de retina es que pueda ser usado por los pacientes por grandes períodos, de lo contrario sería ineficiente. Así uno de los problemas que devienen con la acumulación de la carga residual es el daño al tejido. La carga existente en el electrodo al irse acumulando puede llegar a niveles no seguros y sobre estimular el tejido debido al proceso biológico intrínseco que se produce así como afectar el entorno de la retina

constantemente. Del mismo modo, se puede producir una reacción electroquímica en la superficie del electrodo a un grado mayor del que se pueda tolerar en un sistema fisiológico [16]. Asimismo, el electrodo puede sufrir daños debido a la acumulación de carga; estos daños pueden presentarse en forma de corrosión. Existen valores definidos con los que se ha trabajado que consideran que para operar de manera segura la carga residual debe de estar dentro de un rango de  $\pm$  50 mV o  $\pm$ 100 mV [18] [23].

#### 2.3 Métodos de monitoreo de carga residual existentes

Las técnicas de monitoreo que se han presentado como solución a la carga residual existente en el electrodo se clasifican en dos categorías: técnicas pasivas y técnicas activas.

#### 2.3.1 Técnicas pasivas

Las técnicas pasivas hacen referencia a todos aquellos métodos en los que no existe un control sobre el método mismo.

### 2.3.1.1 Resistencia de descarga

La técnica pasiva más simple es colocar una resistencia de descarga (RD) en paralelo a la resistencia del tejido y la capacitancia de doble capa, las cuales están conectadas en serie. De acuerdo con los presentado en [20], esta técnica posee variantes que solo se centran en la diferencia de conectar dicha resistencia de forma permanente o por medio de una conmutación como se observa en la figura 2.4. El valor de la resistencia de descarga no es muy alto en este tipo de aplicaciones; por ello, una de las consideraciones que se debe tener en cuenta es que si la corriente de estimulación que fluye a través del electrodo no produce un potencial fuera del rango de seguridad, una gran parte de la corriente se irá a través de la resistencia; reduciendo así la eficiencia del estimulador si estuviese conectado permanentemente. Parte de esto se soluciona

cuando la resistencia es conectada por medio de conmutación ya que solo sucederá luego de la estimulación. Sin embargo, la corriente a compensar en algunos casos será mayor y el tiempo de descarga menor al que se tenía antes. Con esto, el tiempo de estimulación debería reducirse o bien que el valor de la resistencia de descarga menor al que se tendría si estuviese permanentemente conectada. Del mismo modo, otra desventaja sería la conmutación misma. Este tipo de aplicaciones requeriría voltajes muy altos como de  $\pm 10$ V, lo cual no es realizable en tecnología CMOS. Si bien se puede soportar altos valores para el drenador-surtidor, no es posible tener voltajes altos de puerta-surtidor.

Figura 2.4 Gráfico de ciclos de descarga y circuito con resistencia de descarga por conmutación [20].

#### 2.3.1.2 Capacitor de bloqueo

Una de las técnicas más populares en el pasado era las capacitancias de bloqueo, estos se conectaban en serie entre el estimulador y la capacitancia de doble capa. Su concepto es simple y provee de características muy beneficiosas para el circuito. La carga residual producida debido al

mismatch de corrientes es acumulada en el capacitor de bloqueo. Un interruptor adicional (S3 en la figura 2.5) se cerrará luego de las fases catódica y anódica para la respectiva descarga del capacitor. La constante de tiempo de descarga para el capacitor dependerá del modelo del electrodo-tejido ( $\tau = RC$ ). Asimismo, gracias a la característica del capacitor de bloquear la señal DC; no permitirá que corrientes directas prolongadas fluyan a través del electrodo y tejido. De lo contrario, podrían suceder fallas en el semiconductor o conexiones. Otra característica es que limita la carga neta por fase [21].

Figura 2.5 Estimulador bifásico con capacitor de bloqueo conectado al electrodo-tejido [21].

No obstante, para aplicaciones multicanales como lo es la prótesis de retina, esta técnica no es la más adecuada ya que el tamaño de los capacitores de bloqueo es más grande que el de los capacitores de doble capa. A causa de la limitación de área que existe, deberían ser componentes fuera del chip lo cual es algo que se busca reducir [18] [20].

#### 2.3.1.3 Cortocircuito del electrodo

Para poder solucionar algunos de los problemas que se presentaban en la técnica que involucraba una resistencia de descarga como las grandes corrientes a través del tejido o los picos de corriente debido a la conmutación, se utiliza un circuito de descarga como el presentado en [22]. Este circuito a su vez servirá para la reducción de la carga residual existente. De acuerdo a la figura 2.6, los transistores NMOS (M1) y PMOS (M2) conectados en serie forman un camino a tierra (gnd). La ventaja de esta conexión es que a altos voltajes, uno de los transistores funcionará como una fuente de corriente para limitar la corriente independiente de la polaridad de carga. El circuito propuesto puede ser global, uno para todas las salidas de los electrodos, o local, uno para cada estimulador. Para poder cambiar los voltajes de puerta necesarios, se hace uso de un circuito de cambio de nivel el cual también está incluido en la figura. De acuerdo a las pruebas realizadas, las corrientes de descarga máximas son de 1.5mA para un voltaje positivo y 1mA para un voltaje negativo.

Figura 2.6 Circuito de descarga [22].

Las técnicas pasivas en general, ofrecen ciertos beneficios como los presentados anteriormente; sin embargo, el mayor problema que presentan y por el cual no pueden ser aplicados a la prótesis de retina es la no existencia de un control. El tiempo de descarga necesario luego de cada estimulación varía de acuerdo a la variación del *mismatch* de corriente y de la impedancia del electrodo que sucede con el tiempo. Así este tiempo no es conocido con exactitud, lo que conlleva a no saber cuál es el potencial del electrodo antes ni después de la estimulación. Todo esto no garantiza una operación segura del electrodo.

#### 2.3.2 Técnicas activas

En el pasado, las técnicas activas para el balanceo de carga residual se basaban en hacer coincidir las fases anódicas y catódicas de la corriente de estimulación; es decir, un *mismatch* igual a cero. No obstante, esto es complicado de conseguir ya que por diferentes motivos como los procesos de fabricación y el paso del tiempo hacen que el *mismatch* no sea exactamente cero y varíe. Así las nuevas técnicas activas buscan entonces definir al potencial del electrodo dentro de un rango de seguridad de operación de manera controlada.

#### 2.3.2.1 Inserción de corriente

La primera forma de insertar corriente de compensación es en forma de pulsos. La idea simplificada de la técnica de inserción de pulsos está ilustrada en la figura 2.7. Para poder mantener el potencial del electrodo dentro de un rango, este debe ser monitoreado y comparado con los valores del rango de seguridad definidos. Mencionados anteriormente, estos rangos de seguridad pueden ser ±50mV o ±100mV. Este proceso se ejecuta durante la fase de no estimulación o descarga para evitar caída de voltaje adicional en la impedancia resistiva del electrodo. Luego de la estimulación, el interruptor se cerrará para monitorear el potencial del electrodo. Si este último estuviera fuera del rango de seguridad, se aplicarán cargas de

compensación a través del estimulador; en forma de pulsos; hasta que el valor del potencial vuelva a estar dentro de dicho rango seguro.

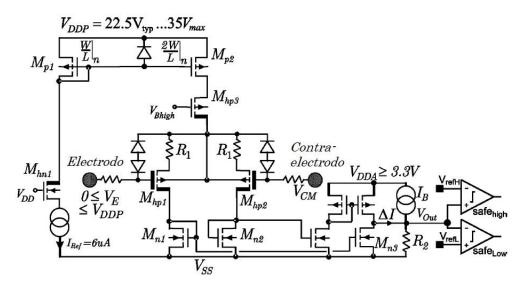

En [23] se presenta un circuito comparador de alto voltaje para el balance de carga residual por medio de inserción de pulsos cuyo circuito es presentado en la figura 2.8. En él, se controla el voltaje entre el electrodo y contra electrodo, cuya diferencia de potencial reside alrededor del potencial medio de VCM igual a 10V. El circuito cuenta con un amplificador diferencial usado para convertir la diferencia de potencial (alto voltaje) entre el electrodo y contra electrodo (ΔV = VE – VCM) en una diferencia de corriente (ΔI). Esta diferencia debe ser reflejada en el dominio de bajo voltaje, por ello es transformada en una diferencia de voltaje (Vout) a través de la resistencia R2 y un offset DC de bajo voltaje ajustable con la fuente de corriente IB. Asimismo, cuenta con dos comparadores de bajo voltaje que determinarán si el potencial del electrodo está dentro del rango de seguridad. Finalmente, se envía la señal de control que de ser necesario cerrará el interruptor adecuado del estimulador de acuerdo a la polaridad para insertar el pulso de compensación.

Figura 2.7 Balance de carga por medio de inserción de pulsos [18].

Sin embargo, el número de pulsos requeridos y la cantidad de *mismatch* que puede ser compensado depende del número de pulsos permitidos en el tiempo disponible luego de la

Figura 2.8 Circuito de balance de carga para inserción de pulso [23].

estimulación así como de la cantidad de carga a balancear. Una variante del balance de carga de [23] es presentado en [18] con el objetivo de solucionar estos problemas y evitar picos de corriente en el balance. El concepto de inserción de corriente es la misma, pero en este caso el proceso de balance de carga no se da exclusivamente luego de la estimulación sino; como un proceso de fondo; es decir, se aplicará una corriente de manera continua aumentado o disminuyendo su valor si el voltaje del electrodo esta fuera del rango de seguridad. En este caso, el voltaje del electrodo es monitoreado por un momento cuando el interruptor se cierra. La diferencia de voltaje (ΔV = VCM - VE) producirá a la salida del comparador una tensión que será la entrada de la etapa de control. Esta última es la encargada de generar la corriente de offset de balance y luego será convertida a un voltaje de offset. Así añadir la corriente de offset adecuada junto a la corriente de estimulación de manera continua, balanceará la carga residual

sin importar el tiempo de descarga disponible, así como no se presentarán picos de corriente como el caso de inserción de pulsos. La figura 2.9 muestra por bloques como está comprendido este método de balance de carga.

Figura 2.9 Circuito de balance de carga con corriente de offset [18].

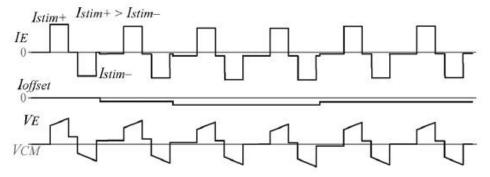

En la figura 2.10 se puede observar que la corriente de offset se añade luego de la primera estimulación. La corriente aumenta o disminuye su valor dependiendo del potencial del electrodo a corregir. Con esto se puede eliminar los picos de corriente que se producían en el método anterior y también la dependencia del balanceo de carga con el tiempo de descarga. Por otro lado, la disipación de potencia del sistema aumenta ya que tenemos otra fuente de corriente a considerar.

Figura 2.10 Formas de onda de un balance de carga permanente [18].

#### 2.3.2.2 Variación del pulso de estimulación

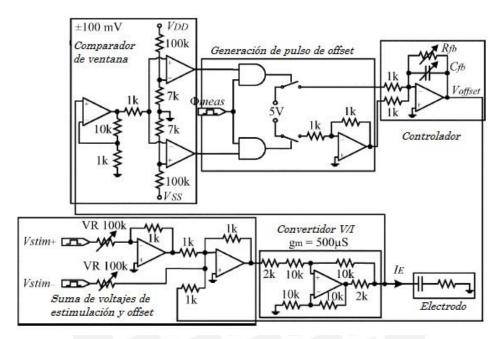

Anteriormente, se presentó a la corriente de estimulación como una serie de pulsos bifásicos. La idea de este tipo de estimulación es que el efecto del primer pulso (anódico o catódico) sea contrarrestado por el segundo pulso. Con esto, surge el concepto de esta técnica de balanceo de carga. Si el potencial del electrodo esta fuera del rango seguro de operación, los parámetros de los pulsos (amplitud y duración) pueden ser modificados para hacer volver al potencial al rango de seguridad. La primera variante de este método es presentado en [17], el concepto del método mostrado en la figura 2.11 busca balancear la carga residual al variar la amplitud de los pulsos anódicos de estimulación. Después de recibir el pulso anódico de estimulación, el interruptor se cierra para verificar si el voltaje del electrodo está dentro de los límites seguros por medio del comparador de ventana. Las salidas del comparador se convierten en las entradas de la unidad de control digital (UCD), la cual se encargará de generar la señal de aumento o decremento de amplitud de la señal anódica si es necesario. Por ejemplo, si el potencial del electrodo resulta ser mayor al límite superior seguro, entonces la señal de decremento (DEC) adquiere un valor lógico de '1'. Así el siguiente pulso anódico será más pequeño mientras que el pulso catódico más grande y por ende el voltaje del electrodo debe disminuir. Lo mismo sucederá si el caso fuese inverso.

Figura 2.11 Diagrama del sistema de balanceo de carga por medio del control de amplitud de pulso [17].

Figura 2.12 Circuito comparador dinámico [17].

Existen dos consideraciones que se deben tener en cuenta respecto a la constante de amplitud de variación del pulso anódico. Primero, la variación debe ser lo suficiente para poder compensar la carga, de lo contrario nunca lo lograría. Segundo, la variación tampoco debe ser muy grande porque podría suceder el caso que eleve el potencial del electrodo fuera del rango seguro. Asimismo, debido a que la compensación de carga residual de un período es realizada en el período siguiente, se debe definir un rango de seguridad menor al que se propone inicialmente. El voltaje del electrodo será comparado con estos nuevos límites para poder garantizar una mayor seguridad. Por último, para minimizar la disipación de potencia, se utiliza un comparador de ventana dinámico (figura 2.12) que solo funcionará por un período corto luego de la estimulación.

De la misma manera que se buscó lograr un balanceo de carga al modificar la amplitud de los pulsos de estimulación, existe otra variante. El otro parámetro que puede ser modificado es el

ancho de pulso; es decir, la duración del pulso de estimulación catódico o anódico. De acuerdo a lo presentado en [19], gracias a un preciso control del ancho de pulso se puede remover la carga residual de forma efectiva sin la necesidad de pulsos de compensación. En esta técnica (ver figura 2.13) nuevamente el voltaje del electrodo es lo primero a ser medido. La medición es realizada por un sensor de realimentación que puede ser un comparador o un conversor analógico-digital (ADC). La salida es enviada a un controlador PID. Con este último se buscará mantener que el error estacionario se aproxime a cero o en todo caso se reduzca lo suficiente, que sea mínimo. Algunos datos importantes que se consideraron en [19] son que se utilizó como sensor de realimentación un ADC de 4 bits y un electrodo de platino el cual tiene una ventana electroquímica o de agua entre -0.6V y 0.8V para una operación segura. La ventana de agua es el rango de voltaje en el cual no ocurren procesos de oxidación ni reducción en una sustancia. En el caso que el voltaje residual medido sea positivo, entonces el ancho del pulso catódico incrementa o bien el ancho del pulso anódico disminuye. La misma lógica se aplica si el voltaje es negativo. Sin embargo, como en la mayoría de aplicaciones, el pulso catódico es el más importante porque representa el pulso de estimulación mientras el anódico representa el pulso de compensación; se modifica el ancho del pulso anódico.

Figura 2.13 Diagrama del sistema de balanceo de carga por medio del control del ancho de pulso [19].

### 2.3.2.3 Inserción de pulsos de corriente con control de ancho de pulso de estimulación

El método presentado en [24] combina dos técnicas mencionadas anteriormente en busca de un mejor desempeño. Su balanceo de carga incluye a un circuito de ajuste de ancho de pulso con inserción de pulsos de corriente basados en la compensación y cuantización de carga residual. Podrá reducir el número de pulsos auxiliares, aquellos que deben insertarse, al mínimo y además controlar la acumulación de carga residual en la etapa inicial.

El sistema cuanta con el generador de pulsos auxiliares (GPA), el bloque de monitoreo de voltaje residual y cuantización de carga residual y por último un controlador digital. Se pueden observar estos tres bloques así como la forma de onda que tendría el comportamiento del potencial del electrodo en la figura 2.14.

Figura 2.14 Arquitectura del sistema de balanceo de carga y formas de onda del voltaje residual [24].

La función del GPA es generar los pulsos de corriente que serán utilizados en la técnica de inserción de pulsos. El circuito de este último tiene la misma arquitectura que el estimulador "front-end" utilizado en [25]. Para las pruebas del circuito también se utilizará al GPA como un

generador de pulsos bifásicos (GPB). En la figura 2.15 se presenta al circuito del bloque de compensación del voltaje residual y cuantización de carga residual. La función de los condensadores C1 y C2 es monitorear el voltaje residual Vres luego de cada pulso de estimulación. Inicialmente se tendrá un offset del opamp (OPA en la figura) y el voltaje VA será igual a Vref + Voffset. Luego de que el transistor Sini esté abierto, el voltaje en el nodo A seguirá al voltaje residual (Vres) del electrodo dando  $VA = Vref + Voffset + \alpha*Vres$ , donde  $\alpha$ será determinado por los condensadores. El opamp funcionará como un comparador entre VA y Vref para determina1r la polaridad del voltaje residual. Al inicializar VA nuevamente en Vref + Voffset, podrá eliminarse Voffset. Una vez que la polaridad del voltaje residual es detectada, se enviarán los pulsos auxiliares hasta que el voltaje residual sea compensando, que exista un cambio en su polaridad. El número de pulsos enviados es registrado para obtener el valor de carga residual compensada. Por último, el controlador digital es el encargado de registrar los parámetros de los pulsos así como la carga residual compensada anteriormente. Con esto, se adaptará el pulso de compensación de la próxima estimulación basándose en el valor de carga residual cuantizado.

Figura 2.15 Diagrama del circuito del bloque de compensación y cuantización [24].

#### 2.4 Elección de topología

Dado lo antes presentado, todas las técnicas de balanceo de carga residual pasivas no son consideradas como las opciones óptimas debido a las desventajas que presentan al ser aplicadas a la prótesis de retina, entre las más importantes está la no existencia de control en el proceso de balanceo de carga lo cual no garantiza una operación segura del electrodo. Por ello, el circuito de seguridad debe ser capaz de definir el potencial del electrodo dentro de un rango de seguridad de operación de manera controlada; es decir, ser una técnica activa. Dentro de las técnicas activas vistas, algunas no son consideradas como las más adecuadas para un futuro diseño. Las técnicas de inserción de corriente mediante pulsos y corriente de offset presentan ciertas desventajas. El primer método tiene la limitante que el número de pulsos requeridos y la cantidad de mismatch que puede ser compensado depende del número de pulsos permitidos en el tiempo disponible luego de la estimulación así como de la cantidad de carga a balancear. El segundo, si bien evita los picos de corriente al no presentar pulsos y elimina la dependencia del balance de carga con el tiempo de descarga, su disipación de potencia es mayor al presentar una fuente de corriente adicional que estará funcionando de manera continua durante todo el proceso de estimulación de la prótesis. La propuesta que busca modificar el ancho del pulso de estimulación presenta ciertas ventajas; sin embargo, su diseño es más complejo al agregar un controlador PID para que el error estacionario sea cero. Asimismo, utilizan un ADC de 4 bits como sensor de realimentación lo cual ya es considerado como algo que ocupará mucha área. Para el caso de la prótesis de retina, un ADC de más de 1 bit es considerado como algo grande en términos de área. La técnica de inserción del pulsos mediante el control de ancho de pulso, vuelve a introducir el concepto de inserción de pulsos lo que podría producir picos de corriente y agregan capacitores para monitorear el voltaje residual. Esto último no es lo mejor si se quiere ahorrar área. Por último, la

técnica activa que modifica la amplitud de pulso de estimulación, es la propuesta más atractiva. Presenta una baja disipación de potencia al utilizar un comparador dinámico el cual solo funcionará cada cierto tiempo para monitorear la carga residual y una lógica sencilla para discernir si se debe aumentar o disminuir la amplitud del pulso de estimulación. El circuito de seguridad a diseñar estará basado en el comparador dinámico conocido como StrongARM Latch, un Latch SR y un bloque de lógica a partir de simples compuertas lógicas.

## Capítulo 3

# ANÁLISIS DEL CIRCUITO DE MONITOREO DE CARGA RESIDUAL

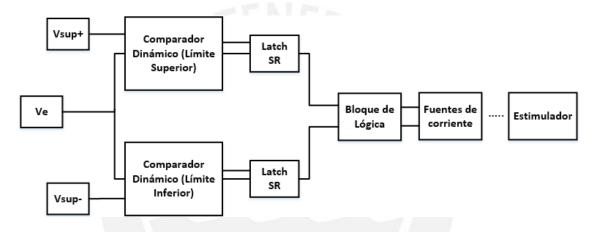

En el presente capítulo, se procede a analizar el funcionamiento del circuito de monitoreo de carga residual, este último está definido de acuerdo al diagrama de bloques de la figura 3.1. Asimismo, se procederá a mencionar sus características y consideraciones que se tendrán en cuenta para un mejor entendimiento y correcto análisis.

Figura 3.1 Diagrama de bloques del circuito de seguridad

De acuerdo a lo concluido en el capítulo 2, se escogió el método activo de modificar la amplitud de uno de los pulsos de estimulación. Dado que en la mayoría de aplicaciones, el pulso catódico es el más importante al representar el pulso de estimulación mientras el anódico representa el pulso de compensación; se modifica la amplitud del pulso anódico. El circuito de seguridad consta de dos comparadores dinámicos, dos latch SR, un bloque de lógica y fuentes de corriente.

Inicialmente, el circuito compara el voltaje del electrodo luego del ciclo de estimulación con dos voltajes de referencia conocidos como ventana de seguridad. Como se mencionó anteriormente, en estudios previos se definió que la ventana de seguridad puede ser ±50mV o ±100mV. Las salidas del comparador serán las entradas del latch SR, este se encargará de definir si las salidas

del comparador son válidas. A su vez, las salidas de los latch SR son interpretadas por el bloque de lógica como sus entradas. Este bloque es el encargado de discernir si la amplitud del pulso anódico de estimulación debe aumentar o disminuir. Finalmente, de acuerdo al resultado del bloque de lógica; se utilizarán fuentes de corriente para modificar la amplitud del pulso de estimulación.

## 3.1 Funcionamiento general del circuito de seguridad

## 3.1.1 Voltaje del electrodo

El análisis del voltaje del electrodo se dará de acuerdo la figura 3.2 que representa un ciclo de estimulación. A partir del modelo del electrodo – tejido de la figura 2.1, se tiene en consideración que la capacitancia de doble capa del contra electrodo ( $C_{HC}$ ) es mucho más grande que la capacitancia de doble capa del electrodo de trabajo ( $C_{HW}$ ). Asimismo, la resistencia farádica ( $R_{FW}$ ) están en el orden de los  $M\Omega$  por lo que no será tomada en cuenta en el análisis. Así para una operación segura, solo bastará con tener en cuenta a la resistencia del tejido ( $R_{FW}$ ) y la capacitancia de doble capa del electrodo de trabajo ( $R_{FW}$ ).

Figura 3.2 Voltaje del electrodo vs tiempo

El análisis comienza cuando la corriente de estimulación catódica (Icat) fluye a través de la resistencia del tejido Rs y el electrodo de trabajo.

Inicialmente, el voltaje del electrodo consta solo de la caída de voltaje V1 en la resistencia Rs.

$$V1 = Icat * Rs \tag{3.1}$$

Debido a que la corriente Icat fluye durante un tiempo de estimulación (tcat), entonces la capacitancia CHW comienza a cargarse a tal punto que existirá un voltaje final en el electrodo V2.

Teniendo en cuenta que en un condensador la corriente es igual a lo siguiente:

$$Ic = C * \frac{dVc}{dt} \to Ic * dt = C * dVc$$

(3.2)

Integrando la expresión (3.2) y despejando Vc.

$$\int Ic * dt = \int C * dVc \rightarrow Vc = \frac{Ic*T}{C}$$

(3.3)

Donde Vc es el voltaje del capacitor luego del tiempo T, Ic es la corriente que fluye a través del capacitor y carga a este mismo y C es el valor de la capacitancia.

De (3.3) se obtendrá

$$V2 = Icat * Rs + \frac{Icat*tcat}{C_{HW}}$$

(3.4)

Luego del tiempo tcat, tiempo que dura el pulso catódico, la caída de voltaje en la resistencia del tejido Rs es 0V. El voltaje V3 simplemente es igual a la carga almacenada en el condensador. Durante el tiempo de retardo entre los pulsos, existirá una pequeña fuga de corriente en el condensador lo que causa que el voltaje V3 comience a disminuir. Sin embargo, al ser una

pequeña fuga durante el retardo entre pulsos el cual es menor a la duración de los pulsos mismos, se asumirá que el voltaje V4 luego del retardo es igual al voltaje inicial V3.

$$V3 = V4 = \frac{Icat*tcat}{C_{HW}} \tag{3.5}$$

Al fluir la corriente anódica a través del electrodo-tejido, vuelve a existir una caída de voltaje en la resistencia Rs.

$$V5 = Ianod * Rs + \frac{Icat*tcat}{C_{HW}}$$

(3.6)

Al igual que en el caso anterior, la corriente anódica cargaría el condensador si este estuviese descargado; pero en este caso descargará el condensador durante el tiempo que la corriente anódica fluya a través de él al ser una corriente opuesta a la corriente catódica.

$$V6 = Ianod * Rs + \frac{Icat*tcat}{C_{HW}} + \frac{Ianod*tanod}{C_{HW}}$$

(3.7)

Finalmente, una vez que no exista flujo de corriente en el electrodo – tejido, el voltaje del electrodo sería igual a V7.

$$V7 = \frac{Icat*tcat}{C_{HW}} + \frac{Ianod*tanod}{C_{HW}}$$

(3.8)

Consideraciones para la ecuación (3.8)

- Idealmente, la magnitud de la corriente anódica debe ser igual a la magnitud de la corriente catódica |Icat| = |Ianod|; sin embargo, esto no es 100% probable.

- Asimismo, las corrientes de estimulación son generadas positiva y negativamente. Así se tendrá una corriente catódica (*-Icat*) y una corriente anódica (Ianod).

- Se puede definir una duración de pulso de estimulación igual a tstim dado que la duración de estos pulsos es de la misma magnitud; es decir, |tcat| = |tanod| = |tstim|.

Así la ecuación (3.8) quedaría de la siguiente forma:

$$V7 = VE = \frac{(Ianod - Icat) * tstim}{c_{HW}}$$

(3.9)

Donde VE es el voltaje en el electrodo luego de un ciclo de estimulación. Este voltaje es el que será comparado con la ventana de seguridad para comprobar si está fuera del rango seguro definido para su posterior compensación o si está dentro de los límites seguros.

## 3.1.2 Comparador

Un comparador es un dispositivo que analiza dos tensiones analógicas o corrientes y modifica su salida para indicar que entrada es mayor. Tal como se observa en la figura 3.1, se tienen dos comparadores dinámicos, utilizar un comparador dinámico es ideal dado que se puede tener el resultado de la comparación rápidamente al igual que una fuerte retroalimentación. Asimismo, su disipación de potencia está dado básicamente por los momentos en donde exista la transición del CLK (señal de reloj) y éste se encuentre comparando; es decir, en funcionamiento. Para un mejor entendimiento se procederá a mencionar las características de uno de ellos ya que ambos comparadores serán iguales.

La figura 3.3 muestra al comparador que define si el voltaje del electrodo está fuera del límite de seguridad superior.

Figura 3.3 Símbolo del comparador

Siendo Vin+ el voltaje límite superior de la ventana de seguridad y Vin- el voltaje del electrodo, se define lo siguiente:

Figura 3.4 Modelo de primer orden de un comparador

La ganancia del comparador:

$$Av = \frac{VOH - VOL}{VIH - VIL} \tag{3.10}$$

Dadas las características de la prótesis epiretinal, el comparador dinámico trabajará a una frecuencia entre 10 kHz a 100 kHz por lo que una característica importante aquí será la resolución del comparador. La resolución del comparador es la mínima diferencia de voltaje a la entrada del comparador para poder obtener un cambio en la salida.

$$V_{in+} - V_{in-} = \Delta V = VIH - VIL \tag{3.11}$$

Siendo

$$V_{in+} = Vumbral + (3.12)$$

$$V_{in-} = VE (3.13)$$

Reemplazando (3.12) y (3.13) en (3.11)

$$Vumbral + -VE = \Delta V = VIH - VIL$$

(3.14)

Así se presentarán dos situaciones en el comparador

$$\label{eq:comparador} Si \ |Vumbral + - VE| \ge \Delta \ V, \ el \ circuito \ responde.$$

Comparador

$$\ \ Si \ |Vumbral + - VE| < \Delta \ V, \ el \ circuito \ no \ responde.$$

Luego de un ciclo de estimulación, y cumpliéndose que Vumbral  $+ - VE \ge \Delta V$ , el comparador procederá a indicar si el voltaje del electrodo es mayor o menor que el voltaje límite de la ventana.

Las salidas del comparador dinámico (Vx y Vy) constan de dos señales que están gobernadas por la frecuencia de reloj ( $f_{CLK}$ ) con la que trabaja el circuito.

$$\label{eq:cuando} \text{Cuando } f_{\text{CLK}} \text{ es } 0, \text{ Vx} = \text{Vdd}, \text{ Vy} = \text{Vdd}.$$

$$\text{Si Vumbral} + > \text{ VE, Vx} = 0, \text{Vy} = \text{Vdd}$$

$$\text{Cuando } f_{\text{CLK}} \text{ es Vdd}$$

$$\text{Si Vumbral} + < \text{VE, Vx} = \text{Vdd, Vy} = 0$$

### **3.1.3 Latch SR**

Las salidas Vx y Vy del comparador son las entradas del latch SR. El motivo de la utilización del latch es sencillo, dado que Vx y Vy dependen de la frecuencia de reloj del comparador; entonces se tendrán señales cuadráticas entre 3.3V y 0V. Sin embargo, luego del latch se tendrán señales constantes ya sea para indicar que la tensión está fuera o dentro del rango de seguridad; es decir,

sirve como memoria. Como se sabe, el latch SR está compuesto por dos compuertas lógicas NAND y obedece la siguiente tabla de verdad:

Figura 3.5 (a) Latch SR de compuertas NAND. (b) Tabla de verdad del latch SR.

La única salida del latch con la cual se trabajará será la salida Q. La tabla de verdad nos indica que si el voltaje del electrodo es menor al voltaje límite superior de seguridad (Vy = 1, Vx = 0), entonces la salida Q es igual a 0. Por otro lado, si el voltaje del electrodo es mayor al voltaje límite superior (Vy = 0, Vx = 1), entonces la salida Q es igual a 1. Asimismo, cuando ambas salidas (Vy, Vx) sean igual a 1, entonces el latch entra en memoria dando a la salida el estado previo. Para poder cerciorase sobre el estado del voltaje del electrodo, se debe saber cuáles son las salidas de ambos latch, tanto para el límite inferior como superior. De esta forma, se tendrán dos salidas Q1 y Q2 que serán las entradas del siguiente bloque, el bloque de lógica.

## 3.1.4 Bloque de lógica

Las entradas del bloque de lógica son Q1 y Q2, obtenidas previamente por los latch SR. En la figura 3.6, se puede observar en que consiste el bloque de lógica. Una compuerta XOR y dos compuertas AND son suficientes para que el circuito sea capaz de discernir la acción que debe

tomarse. El circuito cumple con la tabla de verdad de la figura 3.6. Siendo Q1 la salida del latch SR superior y Q2 la salida del inferior, el circuito de lógica nos indica si el voltaje del electrodo es menor al voltaje límite superior de seguridad (Q1 = 0) y el voltaje del electrodo es mayor al voltaje límite inferior de seguridad (Q2 = 1), entonces la salida INC (incremento) es igual a 1. Por otro lado, si el voltaje del electrodo es mayor al voltaje límite superior de seguridad (Q1 = 1) y el voltaje del electrodo es menor al voltaje límite inferior de seguridad (Q2 = 0), entonces la salida DEC (decremento) es igual a 1. Estas salidas indicarán si es necesario aumentar o disminuir la amplitud del pulso anódico en el siguiente ciclo de estimulación.

Figura 3.6 (a) Circuito de lógica. (b) Tabla de verdad del circuito de lógica.

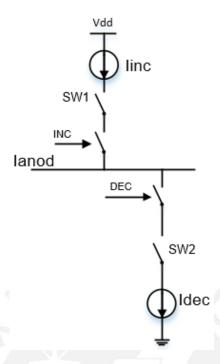

#### 3.1.5 Fuentes de corriente

El último paso para el balance de carga residual, es la compensación de la amplitud del pulso anódico. Del bloque de lógica, se sabrá qué tipo de compensación debe realizarse y con ello que fuente de corriente trabajará como se observa en la figura 3.7. Dada la lógica, el *switch* correspondiente conmutará y dejará fluir la corriente respectiva una vez que el segundo *switch* (SW1 o SW2) se cierre durante el tiempo que se genere el pulso anódico. Uno de los parámetros más importantes del circuito es la corriente a compensar (Iin e Idec), en el circuito se asumen

fuentes de corrientes ideales de magnitud constante al igual que los *switches* también considerados ideales. Debido a que es un valor fijo, ambas corrientes deben tener un valor adecuado lo suficientemente grande para que asegure el balance de carga.

Figura 3.7 Fuentes de corriente de compensación

Asimismo, este valor tiene un límite ya que de ser muy grande podría llevar al electrodo fuera del rango de seguridad. Considerando esto, para poder asegurar que el electrodo se mantenga dentro de la ventana de seguridad, se define una nueva ventana de seguridad. Como la compensación de amplitud del pulso anódico se realiza en el siguiente ciclo de estimulación, definir la nueva ventana de seguridad aseguraría una operación segura.

$$Vu_{nuevo} = Vu_{anterior} - \frac{(lanod-lcat)*tstim}{c_{HW}}$$

(3.15)

Donde Vu<sub>nuevo</sub> es el nuevo voltaje umbral, Vu<sub>anterior</sub> es el voltaje umbral anterior al cual se le resta teóricamente el valor del voltaje del electrodo. Con el nuevo valor de voltaje umbral, el circuito siempre trabajará de forma segura.

Considerando "\varepsilon" como el voltaje del electrodo antes de la estimulación n y a partir de la ecuación (3.9), el voltaje del electrodo luego de la estimulación n es el siguiente:

$$VE_n = \varepsilon + \frac{(Ianod_n - Icat_n) * tstim}{c_{HW}}$$

(3.16)

Asumiendo que el voltaje del electrodo luego de la estimulación n sale del rango de seguridad, entonces la compensación y cambio de la amplitud del pulso anódico debe realizarse en el ciclo de estimulación n+1, el voltaje del electrodo sería igual a:

$$VE_{n+1} = \varepsilon + \frac{(Ianod_n - Icat_n) * tstim}{C_{HW}} + \frac{(I'anod_{n+1} - Icat_{n+1}) * tstim}{C_{HW}}$$

(3.17)

En donde:

$$I'anod_{n+1} = Ianod_{n+1} + I_{comp}$$

(3.18)

$|I_{comp}| = |I_{inc}| = |I_{dec}|$  (3.19)

$$|I_{comp}| = |I_{inc}| = |I_{dec}|$$

(3.19)

Reemplazando (3.18) en (3.17)

$$VE_{n+1} = \varepsilon + \frac{(Ianod_n - Icat_n) * tstim}{C_{HW}} + \frac{(Ianod_{n+1} + I_{comp} - Icat_{n+1}) * tstim}{C_{HW}}$$

$$VE_{n+1} = \varepsilon + \frac{(Ianod_n - Icat_n) * tstim}{C_{HW}} + \frac{(Ianod_{n+1} - Icat_{n+1}) * tstim}{C_{HW}} + \frac{(I_{comp}) * tstim}{C_{HW}}$$

(3.20)

Para asegurar una operación segura del electrodo se debe fijar que el voltaje del electrodo luego de la compensación este dentro del nuevo umbral de seguridad.

$$-|Vu_{nuevo}| < VE_{n+1} < |Vu_{nuevo}| \tag{3.21}$$

El voltaje del electrodo se mantendrá dentro de la ventana de seguridad gracias al circuito analizado.

## 3.2 Análisis de los bloques del circuito

#### 3.2.1 Comparador dinámico

El comparador dinámico a utilizar en el circuito de seguridad será el presentado en [26], figura 3.8. Este circuito es conocido como *StrongARM Latch* y presenta tres importantes ventajas: su disipación de potencia estática es cero, produce salidas que pueden llegar a ser muy próximas a la tensión de alimentación (*rail-to-rail*), su *offset* de entrada proviene principalmente de un par diferencial.

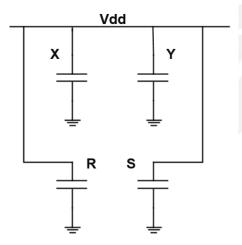

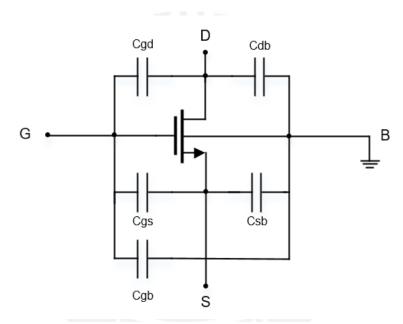

El comparador tiene una frecuencia de reloj (CLK en la figura 3.8) que permite hacer trabajar al circuito por etapas. La frecuencia de trabajo está entre 10kHz y 100 kHz y se considera como V<sub>alta</sub> = Vdd y V<sub>baja</sub> = 0V. Inicialmente cuando CLK esté en baja, los transistores S1 y S4 funcionarán como *switches* lo que permitirá que los nodos R y S estén a una tensión inicial de Vdd. De igual forma, los transistores S2 y S3 precargan los nodos de salida X y Y a Vdd. Los transistores M1 a M7 no estarán activados debido a que están en la zona de corte. Algo importante que mencionar es la existencia de las capacitancias parásitas del transistor. Si bien el circuito del comparador dinámico no trabaja a altas frecuencias en este caso, es importante considerar ciertas capacitancias parásitas para poder realizar el análisis del circuito. Para entender mejor esto, se asumirá que el substrato de los transistores están conectado a GND y que se obtendrá una capacitancia parásita equivalente por nodo, la cual está compuesta por todas las capacitancias que se encuentren conectadas de ese nodo a GND. Dada esta premisa, cuando la señal de reloj esté en baja, inicialmente el circuito quedará como en la figura 3.9.

Figura 3.8 Comparador dinámico StrongARM Latch [26]

Figura 3.9 Comparador dinámico cuando el CLK está en baja

Las capacitancias equivalentes en los nodos indicados en la figura 3.9 son  $C_R$ ,  $C_S$ ,  $C_X$  y  $C_Y$ , dichas capacitancias se cargarán y se mantendrán a un valor de Vdd durante el tiempo en el que la señal CLK se encuentre en baja. En el momento que CLK conmute a alta, los transistores M1

y M2 entrarán en zona de saturación dado que VDS será igual a Vdd y permitirá que las capacitancias  $C_R$  y  $C_S$  se descarguen a través de ellos. La diferencia de tensión de puerta en los transistores M1 y M2 significará una diferencia de corriente de drenador. Debido a esto, uno de los capacitores ( $C_R$  o  $C_S$ ) se descargará más rápido que el otro. Cuando la tensión de los nodos R y S esté por debajo de Vdd – Vthn, donde Vthn es el voltaje umbral del transistor nmos, los transistores M3 y M4 entrarán a zona de saturación y comenzarán a descargar las capacitancias de salida  $C_X$  y  $C_Y$  dependiendo de la diferencia de tensión en los nodos R y S. Sin embargo, la etapa conocida como regeneración se producirá cuando la tensión en las salidas sean menor a Vdd – Vthp, donde Vthp es el voltaje umbral del transistor pmos. Esto dará lugar a que los transistores M5 y M6 entren en zona de saturación permitiendo así la realimentación positiva. Con ello, una de las salidas será muy próxima a Vdd mientras que la otra será muy próxima a GND.

# 3.2.1.1 Análisis en pequeña señal del comparador

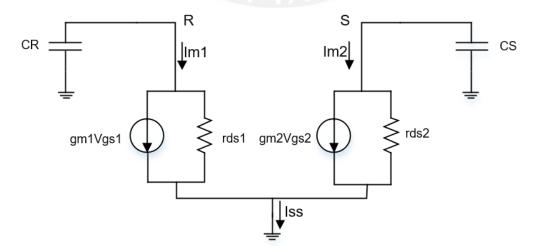

Primero, se procederá a realizar un análisis en el instante en el que la señal CLK conmuta a alta. En este punto, los transistores M1 y M2 se encuentran en zona de saturación y los capacitores  $C_R$  y  $C_S$  se descargarán a través de ellos gracias a que el transistor M7 se encuentra activado.

Figura 3.10 Circuito en pequeña señal del comparador dinámico en el momento de la conmutación de CLK a alta.

Para el análisis de los transistores MOS, se utilizará el modelo cuadrático, el cual utiliza un modelo simplificado de la corriente de drenador para un transistor que opera en la región de saturación. Asimismo, se buscará reducir el efecto cuerpo del transistor al conectar el substrato a GND y se despreciarán las corrientes que circulan por las resistencias rds, las cuales dependen del efecto de la longitud de la modulación de canal. Se procederá a analizar uno de los lados; por ejemplo, el lado del transistor M1.

$$Vgs1 = Vin1 \tag{3.22}$$

$$Im1 = gm1Vgs1 (3.23)$$

Reemplazando (3.22) en (3.23)

$$Im1 = gm1 \times Vin1 \tag{3.24}$$

Para hallar el voltaje del condensador se utilizará la ecuación (3.3), y se reemplazará (3.24) en ella.

$$VR = \frac{-gm1 \times Vin1 \times T1}{CR} \tag{3.25}$$

En donde T1 es el tiempo en el cual el capacitor CR irá descargándose debido al transistor M1.

De manera análoga para el transistor M2 se obtendrá lo siguiente

$$VS = \frac{-gm2 \times Vin2 \times T1}{cs} \tag{3.26}$$

Dado que se asume que los transistores M1 y M2 son idealmente idénticos, entonces se puede tener la siguiente consideración

$$CR = CS (3.27)$$

La duración de esta etapa depende del Vthn de los transistores M3 y M4 ya que una vez que la carga de las capacitancias CR y CS sean menores a Vdd – Vthn; dichos transistores entrarán a zona de saturación. Asimismo, la corriente en modo común (I<sub>CM</sub>) del circuito definirá la duración de esta etapa así como una pequeña ganancia. De la ecuación (3.2)

$$Ts = \frac{C_{R,S}*Vthn}{I_{CM}} \tag{3.28}$$

Para hallar la ganancia, se puede obtener la siguiente ecuación a partir de las ecuaciones (3.25) y (3.26).

$$|VR - VS| = \frac{gm_{1,2} * |Vin1 - Vin2| * T1}{C_{R,S}}$$

(3.29)

Reemplazando (3.28) en (3.29)

$$|VR - VS| = \frac{gm_{1,2} * |Vin1 - Vin2|}{C_{R,S}} * \frac{C_{R,S} * Vthn}{I_{CM}}$$

(3.30)

Se obtiene que la ganancia de esta etapa es igual a la siguiente expresión

$$|Av| = \frac{gm_{1,2} * Vthn}{I_{CM}} \tag{3.31}$$

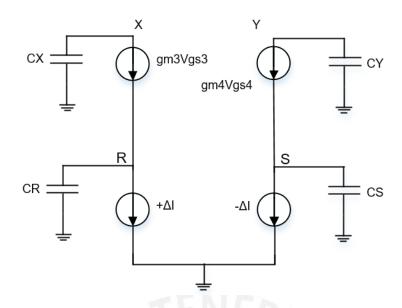

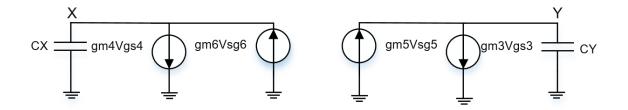

En el momento en el que la tensión en los nodos R y S esté por debajo de Vdd – Vthn, los transistores M3 y M4 entrarán a zona de saturación y los capacitores  $C_X$  y  $C_Y$  comenzarán a descargarse a través de dichos transistores. En la figura 3.11 se presenta el circuito en pequeña señal. Al igual que en la etapa anterior, las corrientes que fluyen a través de las resistencias rds no serán tomadas en cuenta por lo que estas resistencias no serán consideradas. En la figura 3.11,  $+\Delta I$  y  $-\Delta I$  representan la corriente diferencial producida por el par.

Figura 3.11 Circuito en pequeña señal al con los transistores M3 y M4 en saturación

Del circuito se obtiene que

$$Vgs3 = VY - VR$$

$$Vgs4 = VX - VS$$

(3.32)

$$Vgs4 = VX - VS \tag{3.33}$$

La corriente de un capacitor puede obtenerse de la ecuación (3.2)

$$Ic = C x \frac{dV}{dt}$$

Reemplazando (3.32) en (3.2) se puede definir la corriente que fluye en los capacitores CX y CY

$$-CX \frac{dVX}{dt} = gm3 (VY - VR)$$

(3.34)

$$-CY\frac{dVY}{dt} = gm4 (VX - VS)$$

(3.35)

$$-CR\frac{dVR}{dt} = CX\frac{dVX}{dt} + \Delta I \tag{3.36}$$

$$-CS\frac{dVS}{dt} = CY\frac{dVY}{dt} - \Delta I \tag{3.37}$$

Asumiendo que los transistores M3 y M4 son idénticos entre sí al igual que los transistores M5 y M6, se considera que las capacitancias CX y CY son iguales.

Restando (3.34) y (3.35)

$$-CX\frac{dVX}{dt} + CY\frac{dVY}{dt} = gm3(VY - VR) - gm4(VX - VS)$$

(3.38)

$$-C_{X,Y} * \frac{d(V_X - V_Y)}{dt} = gm_{3,4} * (-VX + VY - VR + VS)$$

(3.39)

Integrando (3.36) y (3.37)

$$\int -CR * dVR = \int (CX * dVX) + (\Delta I * dt)$$

(3.40)

$$-CR * VR = CX * VX + \Delta I * t \tag{3.41}$$

$$\int -CS * dVS = \int (CY * dVY) - (\Delta I * dt)$$

(3.42)

$$-CS * VS = CY * VY - \Delta I * t \tag{3.43}$$

Restando (3.41) y (3.43)

$$C_{R,S} * (VS - VR) = C_{X,Y} * (VX - VY) + 2 * \Delta I * t$$

(3.44)

Despejando (VS – VR) y reemplazando la expresión en (3.39)

$$C_{X,Y} * \frac{d(V_X - V_Y)}{dt} - gm_{3,4} * \left(1 - \frac{C_{X,Y}}{C_{R,S}}\right) * (VX - VY) = -2 * gm_{3,4} * \frac{\Delta I * t}{C_{R,S}}$$

(3.45)

Dado que se asume que la transconductancia de M3 y M4 no varía en el tiempo podemos obtener que la diferencia de voltaje de las capacitancias CX y CY al desarrollar la ecuación (3.45).

$$|Vx - VY| = \left| \frac{gm_{3,4} * \Delta I * t^2}{c_{R,S} * [gm_{3,4} * \left(1 - \frac{c_{X,Y}}{c_{R,S}}\right) * t - c_{X,Y}]} \right|$$

(3.46)

Esta segunda etapa transcurre hasta el momento en el que la carga de las capacitancias este por debajo de Vdd – Vthp, lo que hará que los transistores M5 y M6 entren en zona de saturación. El tiempo de la segunda etapa es igual al tiempo que toma descargar los nodos X y Y hasta Vthp. Se puede definir a partir de la ecuación (3.2)

$$Tp = \frac{CX*Vthp}{|\Delta I|} \tag{3.47}$$

Cuando los transistores M5 y M6 entren en zona de saturación, se puede asumir que los transistores M1 y M2 se encuentran en la zona lineal o triodo con una conductancia de valor muy alto por lo que el circuito quedaría como el presentado en la figura 3.12.

Figura 3.12 Circuito del comparador en la etapa de realimentación positiva

La figura 3.13 muestra el circuito de la figura 3.12 en pequeña señal. Se analizará uno de los lados ya que ambos circuitos son iguales. Para el caso de los transistores M3 y M5, se tiene el circuito en pequeña señal simplificado en la figura 3.14.

Figura 3.13 Circuito en pequeña señal del comparador en la etapa de realimentación positiva.

Figura 3.14 Circuito en pequeña señal de los transistores M3 y M5.

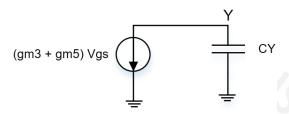

La duración de la etapa de realimentación positiva es igual al tiempo que toma cargar uno de los condensadores (CX o CY) a Vdd mientras descarga el otro a 0. De la ecuación (3.2).

$$-C_Y * \frac{dV_Y}{dt} = (gm3 + gm5) * Vgs \tag{3.48}$$

$$Vgs = V_Y \tag{3.49}$$

Reemplazando (3.49) en (3.48)

$$-C_Y * \frac{dV_Y}{dt} = (gm3 + gm5) * V_Y$$

(3.50)

Integrando ambas partes de (3.50) y despejando el tiempo se obtiene lo siguiente:

$$Tr = \frac{c_Y}{(gm3 + gm5)} \tag{3.51}$$

Donde Tr es igual al tiempo que dura la realimentación positiva.

En esta etapa, existe una ganancia la cual se calcula de la siguiente forma partiendo de la figura 3.13.

$$\frac{dV_X}{dt} + \frac{Gm}{C} * V_Y = 0 ag{3.52}$$

$$\frac{dV_Y}{dt} + \frac{Gm}{C} * V_X = 0 ag{3.53}$$

$$G_m = gm_n + gm_p \tag{3.54}$$

$$gm_n = gm_3 + gm_4 (3.55)$$

$$gm_p = gm_5 + gm_6 (3.56)$$

$$C = C_X = C_Y \tag{3.57}$$

Restando (3.52) y (3.53)

$$\frac{d(V_X - V_Y)}{dt} - \frac{Gm}{C} * (V_X - V_Y) = 0$$

(3.58)

Integrando ambas partes de la ecuación (3.58)

$$\int_0^t \frac{d(V_X - V_Y)}{(V_X - V_Y)} = \int_0^t \frac{Gm}{C} * dt$$

(3.59)