## PONTIFICIA UNIVERSIDAD CATÓLICA DEL PERÚ FACULTAD DE CIENCIAS E INGENIERÍA

# DISEÑO DE UN CONTROLADOR DE CORRIENTE PARA UN NEUROESTIMULADOR EN UNA PROTESIS EPIRETINAL

Tesis para optar el Título de Ingeniero Electrónico, que presenta el bachiller:

Juan Andrés Rojas Raymundo

ASESOR: Ph.D. Manuel Alejandro Monge Osorio CO-ASESOR: Ing. Erick Leonardo Raygada Vargas

Lima, Septiembre del 2018

A mis padres, por su apoyo incondicional en el logro de mis metas.

A mi hermana, por la motivación a siempre querer ser mejor.

A mis asesores, por compartir conocimientos muy valiosos e incentivar el desarrollo de este trabajo.

Al Grupo de Microelectrónica, por encaminar nuestro interés académico hacia el mundo de los semiconductores.

A mi abuelo, por su inefable perseverancia en el éxito académico y laboral de sus hijos y nietos, su legado.

### Resumen

Las enfermedades de degeneración macular y retinosis pigmentaria afectan directamente a la retina, provocando la pérdida de células fotoreceptoras, denominadas bastones y conos, encargadas de la transformación de señales luminosas provenientes del entorno en señales eléctricas que son interpretadas en el cerebro como imágenes. Estas enfermedades son de interés porque provocan la pérdida de células cuyo funcionamiento se puede reemplazar por dispositivos electrónicos, ya que utilizan cargas eléctricas como portadoras de información.

El presente trabajo de tesis se centra en el diseño de un controlador de corriente como circuito integrado en un neuroestimulador que forma parte de un sistema de mayor complejidad, denominado prótesis epiretinal. Las entradas del circuito a diseñar son señales digitales, que determinarán la forma de onda de corriente a generar, y corrientes de referencia para establecer la resolución del controlador de corriente.

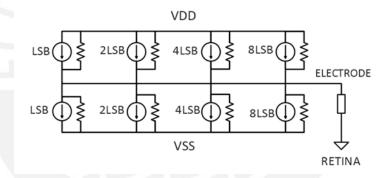

El diseño se basa en una topología de espejos de corriente SCCT (Self Cascode Composite Transistor) como estructura base de Conversores Digital-Analógico colocados directamente a la salida del controlador de corriente, distribuidos en ramas LSB, 2LSB, 4LSB y 8 LSB, con la posibilidad de compartir un circuito de polarización entre los canales locales.

Se ha utilizado transistores de 5 V de la tecnología AMS (Austria Micro Systems)  $0.35~\mu m$ . La carga utilizada para simular el circuito es un modelo de electrodo de impedancia de 30 k $\Omega$  en serie con 100 nF. El circuito fue probado utilizando el simulador SPECTRE en el software de diseño de circuitos integrados CADENCE.

El presente trabajo permitió generar una forma de onda bifásica de corriente máxima de 55  $\mu$ A, con un rango de voltaje a la salida de  $\pm$  2.2 V. La disipación de potencia del circuito se encuentra entre 10.2  $\mu$ W y 72.2  $\mu$ W, dependiendo de la etapa de forma de onda en que se encuentre. El área ocupada por la disposición física del circuito es de 0.006408  $mm^2$ .

#### TEMA DE TESIS PARA OPTAR EL TÍTULO DE INGENIERO ELECTRÓNICO

tarona A UNIVERSIDAD CATÓLICA DEL PE Faculto del Ciliacies e Ingenieria

MEJIA PUENTE

Título : Diseño de un controlador de corriente para un neuroestimulador en una prótesis epiretinal

Área

: Microelectrónica # 4383

Asesor

: Manuel Monge/ Erick Raygada (Co-asesor)

Alumno

: Juan Andrés Rojas Raymundo

Código

: 20110863

Fecha

: 30/06/2017

Descripción y Objetivos

La visión ha sido considerada por muchos años como uno de los sentidos más importantes para el ser humano, y es que, a través de la historia, nos ha servido como el principal medio para obtener información del entorno y poder interactuar con este de manera óptima. Lamentablemente, existen enfermedades degenerativas, que limitan o eliminan esta capacidad al provocar la pérdida de las células fotoreceptoras en la retina. Casualmente, la ingeniería y la medicina han hallado soluciones integrales para solventar dicho problema: las prótesis de retina. El desarrollo de estas se ha podido dar gracias a los avances en microelectrónica, biomateriales, procesos de fabricación y de cirugía. Uno de los elementos esenciales de la prótesis de retina es el estimulador de células retinales o neuroestimulador, el cual se encarga de la generación y control de las ondas de corriente eléctrica que serán inyectadas en la retina a través de electrodos, para provocar la percepción de imágenes en el cerebro. Dentro de los requerimientos principales a ser alcanzados por la ingeniería para este controlador de corriente están: el bajo consumo de energía, soportar altos valores de voltaje a la salida y la reducción del área del circuito integrado a implementar. Con ello se podría incrementar el número de electrodos y, gracias a ello, mejorar la resolución de las imágenes que llegan al cerebro para que los pacientes puedan lograr tareas más complejas, como el reconocimiento de rostros y la lectura. El objetivo de la presente tesis es diseñar un controlador de corriente que optimice los procesos de generación y control de corrientes eléctricas e induzca un impulso eléctrico deseado en la retina con el fin de transmitir al cerebro las imágenes capturadas por una cámara, y así devolver la capacidad de ver a pacientes con enfermedades de degeneración macular. El diseño se basa en una topología de espejos de corriente Cascodo como estructura base de Conversores Digital-Analógico colocados directamente a la salida del controlador de corriente, con un rango de voltajes de salida para corrientes de estimulación de 50 µA, que permitan un control del punto de operación en base a la polarización de los transistores, compartiendo un circuito de polarización entre los canales locales. El circuito se implementó utilizando transistores de 5 V de la tecnología AMS 0.35 µm en el software

B

Cadence de diseño de circuitos integrados.

MÁXIMO SO.

PÁGINAS

PONTIFICIA UNIVERSIDAD CATÓLICA DEL PERÚ FACULTAD DE CIENCIAS E INGENIERÍA

M. Sc. Ing. MIGUEL ANGEL CATAÑO SÁNCHEZ Coordinador de la Especialidad de Ingenieria Electrónica

#### TEMA DE TESIS PARA OPTAR EL TÍTULO DE INGENIERO ELECTRÓNICO

Título : Diseño de un controlador de corriente para un neuroestimulador en una prótesis epiretinal

#### Índice

#### Resumen

#### Introducción

- 1. El neuroestimulador para prótesis epiretinal

- 2. El controlador de corriente

- 3. Diseño del controlador de corriente

- 4. Resultados y simulaciones

Conclusiones

Recomendaciones

Bibliografía

PONTIFICIA UNIVERSIDAD CATÓLICA DEL PERÚ FACULTAD DE CIENCIAS E INGENIERÍA

M. Sc. Ing. MIGUEL ANGEL CATANO SÁNCHEZ Coordinador de la Especialidad de Ingeniería Electrónica

# Índice general

| Ín | Índice de Tablas |        |                                                                                                      |      |

|----|------------------|--------|------------------------------------------------------------------------------------------------------|------|

| Ín | dice             | de Fig | guras                                                                                                | VIII |

| In | $\mathbf{trod}$  | ucción |                                                                                                      | 1    |

| 1. | El I             | Neuroe | estimulador para Prótesis Epiretinal                                                                 | 2    |

|    | 1.1.             |        | la de células fotoreceptoras por nedades de degeneración de retina                                   | 4    |

|    | 1.2.             |        | ulación de la retina mediante pulsos<br>cos                                                          | 5    |

|    | 1.3.             |        | os en ingeniería para los estimuladores de prótesis epiretinales                                     | 7    |

| 2. | El C             | Contro | lador de Corriente                                                                                   | 10   |

|    | 2.1.             | Estado | o del Arte                                                                                           | 10   |

|    |                  | 2.1.1. | El proyecto Argus II de Second Sight                                                                 | 10   |

|    |                  | 2.1.2. | El proyecto EPI-RET-3 del consorcio EPI-RET y el Ministerio de Educación e Investigación de Alemania | 11   |

|    |                  | 2.1.3. | Controlador de Corriente con alto voltaje a la salida para una prótesis epiretinal                   | 13   |

|    |                  | 2.1.4. | Controlador de Corriente con monitoreo y demultiplexación de salidas                                 | 14   |

|    |                  | 2.1.5. | Espejos de Corriente de bajo voltaje headroom para un Controlador de Corriente                       | 16   |

|    | 2.2.  | Cuadro comparativo de parámetros utilizados en trabajos previos        | 17             |  |

|----|-------|------------------------------------------------------------------------|----------------|--|

| 3. | Dise  | eño del Controlador de Corriente                                       | 18             |  |

|    | 3.1.  | Funcionamiento del Controlador de Corriente                            | 19             |  |

|    | 3.2.  | Especificaciones                                                       | 20             |  |

|    | 3.3.  | Topología propuesta                                                    | 22             |  |

|    |       | 3.3.1. Diagrama de bloques y diagrama esquemático                      | 22             |  |

|    |       | 3.3.2. Transistor compuesto o Self Cascode Composite Transistor (SCCT) | 24             |  |

|    |       | 3.3.3. Conversor Digital-Análogo en modo corriente                     | 25             |  |

|    |       | 3.3.4. Circuitos de control digital                                    | 26             |  |

|    | 3.4.  | Análisis en larga señal                                                | 27             |  |

|    |       | 3.4.1. Rango de voltaje y corriente a la salida                        | 28             |  |

|    |       | 3.4.2. Compromisos entre parámetros involucrados en la onda de salida  | 30             |  |

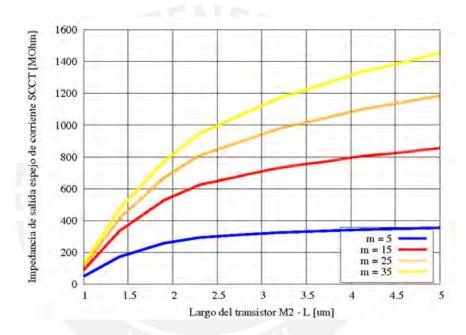

|    |       | 3.4.3. Impedancia de salida                                            | 33             |  |

|    | 3.5.  | Dimensionamiento                                                       | 37             |  |

|    |       |                                                                        |                |  |

| 4. | Res   | ultados y simulaciones                                                 | 38             |  |

|    | 4.1.  | Simulación DC                                                          | 38             |  |

|    |       | 4.1.1. Punto de operación                                              | 38             |  |

|    |       | 4.1.2. Curva característica                                            | 39             |  |

|    | 4.2.  | Simulación transitoria                                                 | 38<br>39<br>41 |  |

|    | 4.3.  | Disipación de potencia                                                 | 42             |  |

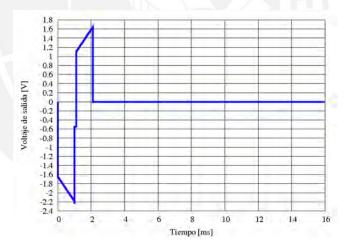

|    | 4.4.  | Slew rate                                                              | 45             |  |

|    | 4.5.  | Disposición física del Controlador de<br>Corriente                     | 46             |  |

| Co | onclu | ısiones                                                                | 48             |  |

| Recomendaciones | 49 |

|-----------------|----|

|                 |    |

| Bibliografía    | 50 |

# Índice de tablas

| 2.1. | Cuadro comparativo de especificaciones utilizadas en el estado del arte                         | 17 |

|------|-------------------------------------------------------------------------------------------------|----|

| 3.1. | Especificaciones para el diseño del Controlador de Corriente                                    | 20 |

| 3.2. | Regiones de operación del transistor                                                            | 27 |

| 3.3. | Parámetros eléctricos de la tecnología 0.35 $\mu\mathrm{m}$ 5V [25] $\ \ldots \ \ldots$ .       | 28 |

| 3.4. | Compromiso entre dimensiones y requerimientos de los transistores $$ .                          | 33 |

| 3.5. | Compromiso entre dimensiones e impedancia de salida en rama LSB .                               | 36 |

| 3.6. | Dimensionamiento de transistores de que conforman espejo de corriente SCCT LSB para PDAC y NDAC | 37 |

| 3.7. | Dimensionamiento de interruptores                                                               | 37 |

| 4.1. | Punto de operación de transistores saturados en ramas LSB $$                                    | 39 |

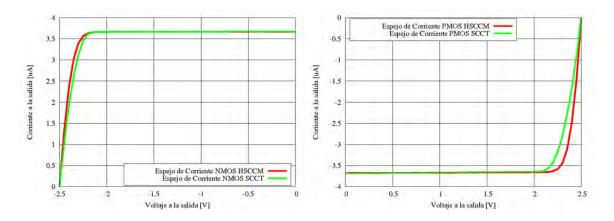

| 4.2. | Curvas de transferencia y rangos de salida de NDAC y PDAC $$                                    | 39 |

| 4.3. | Desempeño de NDAC y PDAC                                                                        | 39 |

| 4.4. | Comparación de ventajas y desventajas entre topologías SCCT y $\operatorname{HSCCM}$            | 41 |

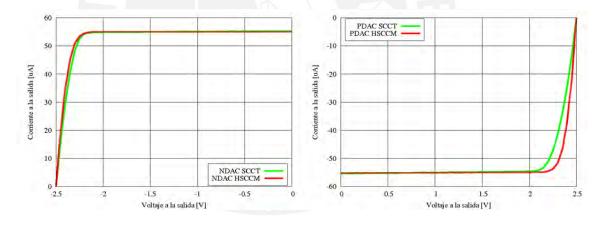

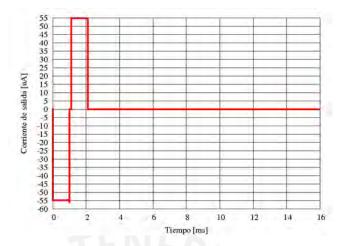

| 4.5. | Parámetros de la forma de onda generada a la salida                                             | 41 |

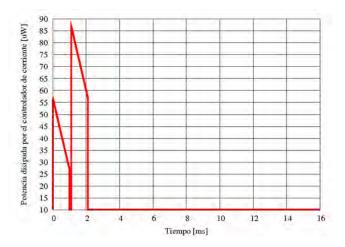

| 4.6  | Disipación de potencia durante fases de la onda de estimulación                                 | 45 |

# Índice de figuras

| 1.1. | Prótesis Epiretinal [3]                                                                                                                         | 3  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2. | Concepto del neuroestimulador basado en la percepción de Fosfenos [5].                                                                          | 3  |

| 1.3. | Efecto en la visión, denominado "túnel", causado en un paciente con RP [9]                                                                      | 4  |

| 1.4. | Efecto en la visión causado en un paciente con DMAE [9]                                                                                         | 5  |

| 1.5. | Onda de corriente bifásica para la estimulación eléctrica de la retina [11]                                                                     | 6  |

| 2.1. | Componente Interno del sistema de prótesis de retina Argus II [16]                                                                              | 11 |

| 2.2. | Componente Externo del Sistema de prótesis de retina Argus II. [16].                                                                            | 11 |

| 2.3. | Implante Intraocular del proyecto EPI-RET-3 [20]                                                                                                | 12 |

| 2.4. | Diagrama de bloques del estimulador [21]                                                                                                        | 12 |

| 2.5. | Arquitectura del Controlador de Corriente propuesto por <i>Chen et al.</i> [15]                                                                 | 13 |

| 2.6. | Forma de onda a la salida del controlador de corriente y <i>layout</i> del mismo [15]                                                           | 14 |

| 2.7. | Controlador de Corriente con monitor de salida y demultiplexor 1:4 [10]                                                                         | 15 |

| 2.8. | Implementación del (a) espejo de corriente de bajo consumo e (b) interruptor de alto voltaje [11]                                               | 16 |

| 3.1. | Funcionamiento del Controlador de Corriente o Current Driver                                                                                    | 19 |

| 3.2. | Diagrama de bloques del Controlador de Corriente                                                                                                | 22 |

| 3.3. | Diagrama Esquemático del Controlador de Corriente                                                                                               | 23 |

| 3.4. | (a) Topologia de transistor compuesto o SCCT-Self Cascode Composite<br>Transistor (b) Espejo de corriente simple utilizando topología SCCT [26] | 24 |

| 5.3.  | duplicar ancho del transistor [27] (b) Técnica aplicada al NDAC del controlador de corriente     | 25 |

|-------|--------------------------------------------------------------------------------------------------|----|

| 3.6.  | Circuito de conmutación de rama PDAC [28]                                                        | 26 |

| 3.7.  | (a) Puerta NOT (b) Interruptor complementario [27]                                               | 26 |

| 3.8.  | Etapa de salida del Controlador de Corriente                                                     | 28 |

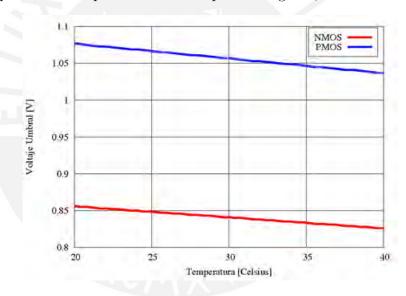

| 3.9.  | Voltaje umbral del transistor NMOS-PMOS vs. Temperatura                                          | 30 |

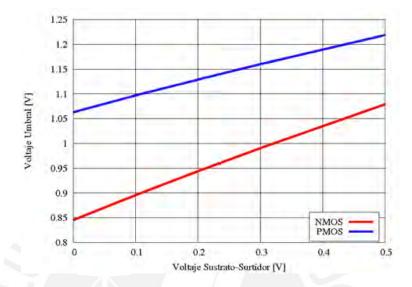

| 3.10. | Voltaje umbral del transistor NMOS-PMOS vs. diferencia de potencial entre sustrato y surtidor    | 31 |

| 3.11. | Topología SCCT y factor de forma de transistores [26]                                            | 33 |

| 3.12. | Compromisos existentes entre dimensiones de transistores y voltaje $V_{GS}$                      | 34 |

| 3.13. | Controlador de Corriente con fuentes de corriente no ideales                                     | 34 |

| 3.14. | Compromisos existentes entre dimensiones de transistores e impedancia de salida                  | 36 |

| 4.1.  | Curva característica de espejos de corriente HSCCM y SCCT                                        | 40 |

| 4.2.  | Curva característica del controlador de corriente $\operatorname{HSCCM}$ y $\operatorname{SCCT}$ | 40 |

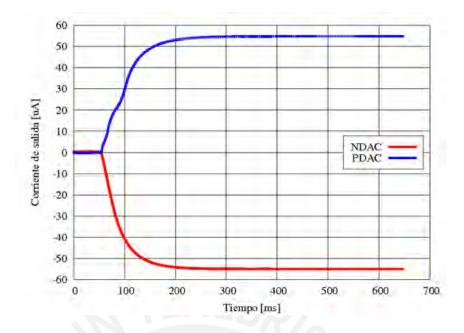

| 4.3.  | Forma de onda bifásica de corriente simulada en el modelo de electrodo                           | 42 |

| 4.4.  | Forma de onda bifásica de voltaje simulada en el modelo de electrodo                             | 42 |

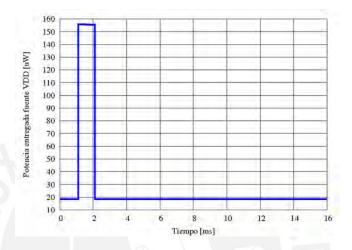

| 4.5.  | Potencia entregada por fuente $V_{DD}$                                                           | 43 |

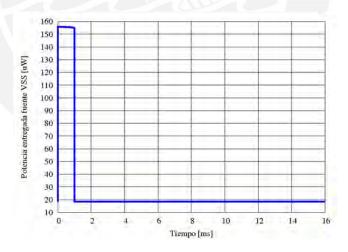

| 4.6.  | Potencia entregada por fuente $V_{SS}$                                                           | 43 |

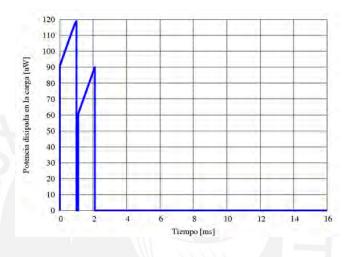

| 4.7.  | Potencia consumida por el electrodo durante el periodo de estimulación                           | 44 |

| 4.8.  | Disipación de potencia en el controlador de corriente                                            | 45 |

| 4.9.  | Velocidad de cambio de la corriente catódica de salida del circuito                              | 46 |

| 4.10. | Disposición física del controlador de corriente                                                  | 47 |

## Introducción

La visión ha sido considerada por muchos años como uno de los sentidos más importantes para el ser humano, y es que a través de la historia, ha servido como el principal medio para obtener información del entorno y poder interactuar con este de manera óptima. Lamentablemente, existen enfermedades degenerativas que limitan o eliminan esta capacidad al provocar la pérdida de las células fotoreceptoras, diferentes de los defectos refractivos como la miopía o la presbicia. Casualmente, la ingeniería y la medicina han hallado soluciones integrales para solventar dicho problema: las prótesis de retina. El desarrollo de estas se ha podido dar gracias a los avances en microelectrónica, materiales, procesos de fabricación y cirugía.

Uno de los elementos esenciales del dispositivo de remplazo de retina es el estimulador del nervio óptico o neuroestimulador, el cual se encarga de la generación y control de las ondas de corriente eléctrica que serán inyectadas en la retina a través de electrodos, para provocar la percepción de imágenes en el cerebro. Dentro de los requerimientos principales a ser alcanzados por la ingeniería para este controlador de corriente están el bajo consumo de energía, altos valores de voltaje a la salida y la reducción del espacio ocupado por el circuito. Con ello se podría incrementar el número de electrodos y, gracias a ello, mejorar la resolución de las imágenes que llegan al cerebro para que los pacientes puedan lograr tareas más complejas, como el reconocimiento de rostros y la lectura.

El objetivo del presente trabajo es diseñar un controlador de corriente que optimice los procesos de generación y control de la forma de onda a ser inducida en un modelo de electrodo, de manera que permita un rango de voltaje a la salida acorde al modelo de electrodo elegido, presente una alta impedancia de salida, en el orden de los  $M\Omega$ , con el fin de acercarse al comportamiendo de una fuente ideal de corriente, y que consuma poca área en el chip, menor a  $0.02~mm^2$ , para incrementar la cantidad de canales.

## Capítulo 1

# El Neuroestimulador para Prótesis Epiretinal

Debido a la imposibilidad de detener o invertir el proceso de destrucción de células fotoreceptoras causado por enfermedades de degeneración de retina, surge la propuesta del neuroestimulador para prótesis epiretinal, cuyo principal aporte consiste en la estimulación eléctrica del tejido neuronal en la superficie de la retina mediante la inyección de ondas de corriente eléctrica bifásicas que generen un impulso eléctrico en las células ganglionares y provoquen la sensación de la vista. Estas ondas de corriente son generadas por un circuito denominado Controlador de Corriente, el cual será explicado con mayor detalle en el siguiente capítulo. El neuroestimulador forma parte de un sistema más complejo llamado prótesis de retina o prótesis visual [1] [2], que tiene como objetivo restaurar parcialmente la visión en personas que sufren de ceguera al convertir una imagen a señales eléctricas mediante un dispositivo de video, procesarla mediante un circuito externo o implantable y generar estímulos eléctricos que serán aplicados a la retina mediante un arreglo de microelectrodos posicionados cerca de la zona macular.

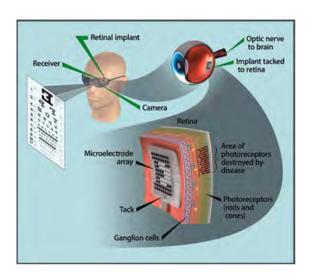

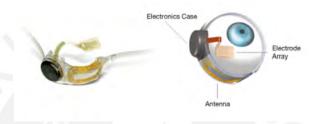

De manera particular, se ha elegido la prótesis epiretinal como el sistema en el cual se integrará el circuito que será diseñado en la presente tesis, ya que los requerimientos en ingeniería para ambos son comunes en muchos puntos, los cuales serán explicados en la sección 1.3. Desafíos en ingeniería para los neuroestimuladores de prótesis epiretinales. La denominación epiretinal alude a la ubicación espacial del arreglo de microelectrodos para la estimulación, que en este caso se posará en la superficie de la retina, a diferencia de las configuraciones subretinal y supracoroidal que implican otra ubicación de los microelectrodos. La Fig. 1.1 sirve de ejemplo para el concepto de prótesis epiretinal, la cual está conformada por tres etapas: una cámara de video, un receptor y el arreglo de microelectrodos. Es necesario mencionar que el receptor representa el conjunto de circuitos electrónicos que se intenta con mayor esfuerzo mejorar y está compuesto de muchas otras etapas, entre ellas, el neuroestimulador.

Figura 1.1: Prótesis Epiretinal [3].

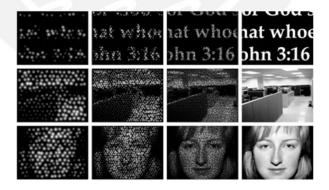

El neuroestimulador tiene como función principal: estimular de manera controlada la zona macular y las células ganglionares por medio de microelectrodos que aplican cargas eléctricas para provocar polarización del tejido e impulsos eléctricos que serán enviados por el nervio óptico y el quiasma hacia el cerebro, a manera de información [4]. La visión prostética simulada y la caracterización del entorno por medio de "spots" de luz que se reconocen en el cerebro debido al número limitado de electrodos utilizados para la estimulación dan lugar al fenómeno de los Fosfenos, los cuales conforman una representación de lo que posiblemente es percibido por los pacientes con implantes de prótesis epiretinal. La agudeza de la visión se puede relacionar proporcionalmente al número de electrodos y la precisión en la generación de ondas de estimulación, como lo ejemplifica la Fig. 1.2 al incrementar dichos parámetros de izquierda a derecha.

Figura 1.2: Concepto del neuroestimulador basado en la percepción de Fosfenos [5].

La mayor problemática que comprenden estos dispositivos, debido a que implican insertar un circuito electrónico en un organismo vivo, está asociada a tres indicadores: disipación de potencia, dado que una mayor potencia implica mayor calor que puede

dañar al tejido del paciente; rango de voltaje a la salida, que debe ser acorde al valor de resistencia de los electrodos; y área, con el fin de reducir el tamaño del chip que será implantado en el paciente. Estos parámetros, además de algunos otros relacionados a la generación de la onda de corriente bifásica como umbrales de corriente de estimulación y ancho de banda, forman la base para la creación de los requerimientos de diseño, los cuales serán acordes a las características electrofisiológicas de la retina para no exacerbar el estado del organismo y servirán para la elección de configuraciones de MOSFETs (Metal Oxide Semiconductor Field Effect Transistors).

### 1.1. Pérdida de células fotoreceptoras por enfermedades de degeneración de retina

Entre las múltiples enfermedades que causan ceguera en las personas a nivel mundial, nos centramos particularmente en aquellas que causan la pérdida de células fotoreceptoras en la retina, conos y bastones, de manera degenerativa en un periodo de tiempo. También denominadas enfermedades de degeneración de retina, consisten básicamente en dos tipos: Degeneración Macular Asociada a la Edad (DMAE) y Retinosis Pigmentaria (RP).

La DMAE se ubica como el primer causante de ceguera en países industrializados y tercera a nivel mundial [6]. En el Perú, se identificaron 2229 casos durante el año 2014 [7], lo que representa una frecuencia diaria de 6 pacientes con DMAE y convierte a dicha enfermedad en el diagnostico con mayor frecuencia en pacientes que acuden al servicio de retina del Ministerio de Salud, principalmente a personas de edad superior a los 50 años. La DMAE implica la pérdida de la visión central debido a lesiones degenerativas en la zona macular de la retina. Ello conlleva a la pérdida de conos y bastones pero no de otras capas de células neuronales presentes en la retina.

Figura 1.3: Efecto en la visión, denominado "túnel", causado en un paciente con RP [9]

La RP es una enfermedad de carácter genético que conlleva a un número de deficiencias oculares que provocan la pérdida de células fotoreceptoras en la retina,

Figura 1.4: Efecto en la visión causado en un paciente con DMAE [9]

con una reincidencia promedio de 1 en cada 3500 individuos [2]. Dicho grupo de enfermedades degenerativas se caracterizan por una pérdida lenta y progresiva de la visión, que afecta, al menos en sus etapas iniciales y a diferencia de la DMAE, a la visión nocturna y periférica, conduciendo en algunos casos a la ceguera. Es frecuente la aparición de acúmulos de pigmento en el fondo del ojo [8]. Sin embargo, al igual que en la DMAE, después de la muertes de las células fotoreceptoras, la RP no destruye las células ganglionares ni bipolares, entre otras, que se encargan del filtrado y transporte al nervio óptico de las señales fisicoquímicas o eléctricas que representan la imagen capturada.

Debido a que las enfermedades de degeneración de retina solo implican la desaparición de las células fotoreceptoras, es posible restaurar la visión al simular o remplazar los conos y bastones mediante estimulación eléctrica para generar impulsos eléctricos en las células restantes de la retina que puedan transportar dichas señales al cerebro por el nervio óptico.

# 1.2. Estimulación de la retina mediante pulsos eléctricos

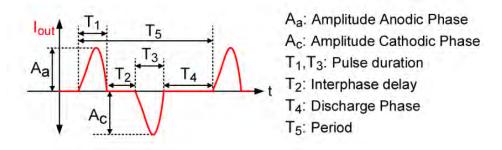

El objetivo de inyectar una carga eléctrica al tejido de la retina es generar una variación de voltaje  $\Delta V$  que polarice a la neurona o célula ganglionar para provocar un disparo o impulso eléctrico en una región de la zona macular, logrando la función de las células fotoreceptoras perdidas. Para alcanzar la meta propuesta es necesario implementar una forma de onda de corriente bifásica, como la descrita en la Figura 1.5, que pueda inyectar y luego retirar una carga eléctrica en el tejido con la mayor precisión posible, dado que el excedente de carga restante en el tejido puede provocar daño celular por efectos colaterales como electrólisis, formación de gas y corrosión de los electrodos.

La cantidad de carga inyectada debe ser controlada, es decir, ambas ondas anódica

y catódica,  $A_a$  y  $A_c$  respectivamente en la Figura 1.5, deben ser lo más parecidas posibles para evitar acumulación de carga en el tejido. Este es un requerimiento que se mencionará a lo largo de toda la tesis, puesto que implica la modificación de otros parámetros. La cantidad de carga inyectada se asocia, por ejemplo, al umbral de corriente de estimulación, que se explica como la mínima corriente necesaria para generar un estímulo en la retina y provocar un Fosfeno en la percepción visual. Este umbral puede variar entre algunas decenas de  $\mu$ A [2] [10] y debe ser elegido con el mayor rigor posible ya que implica en gran medida la disipación de potencia.

Figura 1.5: Onda de corriente bifásica para la estimulación eléctrica de la retina [11]

De la misma manera, la duración de cada una de las fases debe ser considerada, puesto que pueden modificar la disipación de potencia, la acumulación de cargas y la eficiencia en la estimulación. La propuesta de elegir una forma de onda más flexible [10]- [12], surge con la posibilidad de incrementar la eficiencia en la estimulación, reducir el alto voltaje requerido a la salida y reducir los umbrales de corriente de estimulación. Esta flexibilidad se representa en: el orden que se inyectan las cargas, primero la onda catódica y luego la anódica por ejemplo; si la forma de onda es no rectangular o asimétrica, como por ejemplo, gaussiana o exponencial; la frecuencia de los pulsos o periodo de la onda; entre otros.

Una forma de conseguir los umbrales de corriente y carga de estimulación consiste en la estimulación de células ganglionares con trenes de pulsos cuya amplitud varía desde un valor pequeño y se incrementa poco a poco hasta conseguir una respuesta en acción potencial de la célula en el 50 % de los pulsos aplicados [12]. Asimismo, se pueden modificar parámetros de la forma de onda de corriente para alcanzar una optimización en la estimulación, como la duración de fases, intervalos entre fases, polaridad, frecuencia y asimetría, considerada como la diferencia entre las formas de onda catódica y anódica. Por lo pronto, se conoce que existe una mayor respuesta de actividad neuronal a partir de una mínima carga cuando se aplica primero la onda catódica y la duración del primer pulso es muy pequeño, de aproximadamente 60  $\mu$ s [12].

Por otro lado, ambos parámetros de corriente de estimulación y duración de los periodos de cada fase convergen con otros que son de máximo interés para la estructuración de los requerimientos de diseño. Uno muy importante es el voltaje de

alimentación, el cual, a pesar de consistir en uno fijo, debe asumir los gastos en consumo de voltaje de cada uno de los elementos a implementar en el circuito, como lo son el Controlador de Corriente, los electrodos y las características de cada uno.

$$V_{DDP,min} = I_{stim}R_E + \frac{I_{stim}T_{stim}}{C_E} + V_{headroom}$$

(1.1)

En la ecuación 1.1 propuesta por [10] podemos observar que efectivamente la definición de los parámetros de la forma de onda, corriente de estimulación  $I_{stim}$  y periodo de la onda de estimulación  $T_{stim}$ , repercuten en el consumo de voltaje de otros elementos, como el del voltaje headroom del controlador de corriente, que se explicará más adelante, y el voltaje mínimo de alimentación  $V_{DDP,min}$ . También se puede observar que el modelo de impedancia elegida para el electrodo implica un gran incremento en el voltaje mínimo de alimentación. De ahí que muchos diseñadores buscan incrementar el máximo rango de voltaje a la salida y disminuir el consumo de voltaje de los espejos o fuentes de corrientes a la salida del Controlador de Corriente, denominado headroom.

Como hemos podido explicar, la forma de onda, que es el componente principal de la estimulación de retina mediante cargas eléctricas, está caracterizada por parámetros cuyo diseño es muy importante para el desarrollo de un Controlador de Corriente. Consecuentemente, estos parámetros son muy difíciles de definir, considerando el entorno biológico en el que se trabaja que consiste básicamente en las capacidades electrofisiológicas del tejido de la retina. Por ello, existen limitaciones que han sido descubiertas en el proceso de desarrollo e implementación de prótesis de retina y su experimentación in vivo e in vitro que deben ser explicadas para ser consideradas a la hora de generar una lista de requerimientos de las topologías que se utilizarán en el Controlador de Corriente.

# 1.3. Desafíos en ingeniería para los neuroestimuladores de prótesis epiretinales

Para poder listar las limitaciones que presenta un neuroestimulador, es necesario acotar las diferencias en requerimientos entre los tipos de prótesis epiretinal, subretinal y supracoroidal. En una prótesis subretinal, donde el arreglo de electrodos se encuentra debajo de la retina y remplazando el espacio que solía ser ocupado por los conos y bastones, la estimulación se realiza mediante un implante pasivo, el cual consiste en la activación de fotodiodos por recepción de fotones de luz y amplificación de señales para enviarlas a los electrodos. Por otro lado, la prótesis epiretinal se basa en la conversión de señales de imágenes digitales, provenientes de un sistema de cámara, a formas de onda bifásicas como la explicada en la sección previa. Por último, la prótesis supracoroidal, ubicada entre la esclerótica y la coroides, implica el

implante de dos electrodos: un arreglo a ubicarse en un espacio de la esclerótica y otro electrodo de retorno en la cavidad del vítreo, el cual implica el diseño de un nuevo bloque de señales de retorno [13]. En base a las descripciones básicas presentadas, podemos notar que el diseño a tratar en la presente tesis va enfocado a una prótesis epiretinal, ya que se utilizara una única estructura de electrodos de estimulación y se convertirán señales digitales provenientes de un sistema de imágenes a la forma de onda de corriente bifásica deseada, sin utilizar fotodiodos ni implantes pasivos.

Una de las limitaciones más importantes a considerar es la disipación de potencia. Esta ha sido descrita en base a tres factores: tamaño de los electrodos, impedancia del medio biológico y requerimientos de salida del neuroestimulador [2]. Los primeros dos factores determinan la carga final a la salida del Controlador de Corriente, mientras que el último factor implica el proceso de generación de la onda de estimulación. Además de los factores mencionados, es necesario considerar otros como la potencia mínima de saturación de los bloques internos al Controlador de Corriente [1] y el consumo de potencia en telemetría, donde este último no será trabajado en el presente diseño. Se considera un nivel de seguridad en el consumo de potencia, pues el incremento de la corriente que fluye dentro de un componente electrónico genera un incremento en la temperatura del entorno adyacente, el cual puede causar daño neuronal en la retina. Por lo pronto, se considera un incremento mayor a 1°C como dañino, lo cual implica un límite de seguridad de 3 mA y, ello a la vez, un límite en disipación de potencia de 77.8 mW [14].

El problema de las altas impedancias causadas por el entorno biológico y el electrodo es que se necesita un mayor rango de voltaje para poder inducir en ellas una corriente de estimulación. A este requerimiento se le denomina Voltage Compliance y tiene que ver con el rango de voltaje a la salida del Controlador de Corriente. Este parámetro se puede volver menos exigente en el caso que los electrodos representen una impedancia más pequeña, como de  $\pm$  2.5 V para electrodos de 20 K $\Omega$  y 160 nF [11]. Consecuentemente, la reducción del voltaje a la salida en este último caso implica una limitación en la máxima corriente que se puede generar en la forma de onda de estimulación, por lo que se recomienda un rango de voltaje a la salida de  $\pm$ 10 V debido a los electrodos de 30 K $\Omega$  [2]. Ahora que se sabe que el interfaz generado por el electrodo y el tejido neuronal de la retina está conformado por una impedancia resistiva y capacitiva, se vuelve necesario diseñar una respuesta en frecuencia optima, para lo cual se deben conocer todos los valores de capacitancia generados por dicho interfaz, así como de las capacitancias parasitas presentes en los MOSFET's. Esto puede convertirse en un gran limitante de ancho de banda, el cual permitirá ciertas frecuencias de ondas que se desean generar.

Otro limitante importante es el área ocupada por el implante. Cabe resaltar que existen muchos elementos que conforman a un neuroestimulador, además del Controlador de Corriente que se desea diseñar. Entre ellos, se considera a los elementos fuera del chip como capacitores y diodos, biomaterial de encapsulamiento de electrónicos como los polímeros, bobinas de inducción y comunicación, arreglo de electrodos, además de los otros bloques del neuroestimulador que comparten espacio en el chip

con el Controlador de Corriente. Más aún, el tamaño de los implantes de retina se encuentra limitado por las pequeñas incisiones que se pueden realizar en el globo ocular, de un máximo de 5 mm [1]. Por ejemplo, el límite en espacio ocupado recomendado para una prótesis epiretinal de 1024 canales de estimulación es de  $8\times 8$   $mm^2$  [10]. Asimismo, se puede observar que existe una tendencia en la reducción del área ocupada por los chips diseñados para las prótesis epiretinales e incremento de la cantidad de canales de estimulación, de  $5.3\times 5.1$   $mm^2$  en el 2010 [15] a  $3.1\times 4.5$   $mm^2$  en el 2013 con el doble de número de canales de estimulación [11].

También se puede observar que muchos implantes desarrollados presentan baja resolución, en el sentido que no permiten una alta cantidad de electrodos. Por ello, se busca mejorar la capacidad de empaquetamiento tanto como disminuir el espacio ocupado en el chip por los canales de estimulación y Controladores de Corriente. Esto hace un llamado nuevamente a la reducción del área ocupada y, para este nuevo caso, al incremento de la densidad de electrodos en el arreglo de estimulación [1]. Ciertamente existen prótesis de retina que han alcanzado altas densidades de electrodos pero con un tiempo de vida útil menor a 1 año, por lo que la duración del implante se vuelve un limitante de los neuroestimuladores. Este se puede incrementar utilizando mejores tecnologías de empaquetamiento. Existen limitantes dentro del Controlador de Corriente que pueden generar cierta imperfección en la generación de la forma de onda de corriente deseada. Por un lado, se encuentran los errores dinámicos, como el tiempo de establecimiento, y estáticos, como el error de desplazamiento y error de ganancia, dentro del conversor digital análogo. Por otro lado, los espejos de corriente pueden generar un limitante en la ganancia deseada al encontrarse una transconductancia fija para cada etapa.

## Capítulo 2

### El Controlador de Corriente

La estrategia a utilizar para la estimulación de la retina se basa en pulsos de corriente que serán generados por todas las etapas en conjunto que conforman al controlador de corriente. De ahí, podemos observar que el único objetivo del circuito a diseñar será la generación de la forma de onda bifásica explicada en el Capítulo 1. Para esto, existen arquitecturas que han sido propuestas y simuladas, por lo que un estudio de los parámetros utilizados por ellos se vuelve indispensable para poder generar requerimientos acordes a las necesidades actuales. A continuación se presenta una revisión de los principales Controladores de Corriente desarrollados en los últimos cinco años.

### 2.1. Estado del Arte

### 2.1.1. El proyecto Argus II de Second Sight

Argus II consiste en un sistema de prótesis de retina (RPS o  $Retinal\ Prosthesis\ System$  en inglés) patentado por la compañía  $Second\ Sight$  de desarrollo, fabricación y venta de prótesis visuales implantables para personas que sufren de ceguera provocada por enfermedades de degeneración de retina [16]. El sistema se encuentra compuesto por una parte externa y un implante que se ubica en el globo ocular. El componente externo lo conforma una cámara de video montada en unos lentes y una Unidad de Procesamiento de Video o VPU por sus siglas en inglés. El implante contiene un arreglo epiretinal de 60 microelectrodos, de 200  $\mu$ m de diámetro cada uno, un encapsulado de electrónicos y una bobina de recepción de datos o antena. La forma de onda que se genera para conseguir la estimulación eléctrica consiste en una del tipo bifásica donde la onda bifásica catódica ocurre antes de la anódica, con balance de carga para evitar efectos adversos por generación de gas o electrólisis y con monitoreo de la excursión de voltaje e impedancia en electrodos para poder realizar estudios a largo plazo de la variación de estos parámetros [17].

La regulación en la venta y producción de este sistema de prótesis de retina permitió una gran cantidad de pruebas in vivo en personas ciegas que fueron confirmando la portabilidad, estabilidad y larga duración del implante. Por lo pronto, en el 2012 se realizó un estudio para evaluar la seguridad y utilidad de la prótesis en ciegos con alta degeneración de retina. Por ello, se realizaron pruebas de agudeza visual, como localización de objetos y detección de movimiento en pacientes con el dispositivo implantado, y de prueba de utilidad, como la ubicación de una puerta en una sala y el seguimiento de una línea, consiguiendo resultados satisfactorios con umbrales de estimulación en promedio menores a 1 mC/ $cm^2$  y con menores eventos adversos [18]. Asimismo se confirmó la capacidad de indetificacion de letras y lectura de palabras cortas con una mínima separación entre letras para pacientes con el sistema implantado, en un rango de tiempo alcanzado de 6 a 221 segundos para cada paciente [19]. Con ellos se confirma la funcionalidad hasta 34 meses luego de la implantación.

Figura 2.1: Componente Interno del sistema de prótesis de retina Argus II [16].

Figura 2.2: Componente Externo del Sistema de prótesis de retina Argus II. [16].

# 2.1.2. El proyecto EPI-RET-3 del consorcio EPI-RET y el Ministerio de Educación e Investigación de Alemania

EPI-RET-3 es un sistema de implante de retina intraocular seguro y eficiente que consta de una parte extraocular y un implante intraocular. El implante extraocular lo conforma una computadora con un software para la estimulación, una unidad de transmisión basada en un FPGA o Field Programmable Gate Array, un amplificador clase E y una bobina de transmisión o antena. El implante intraocular posee una

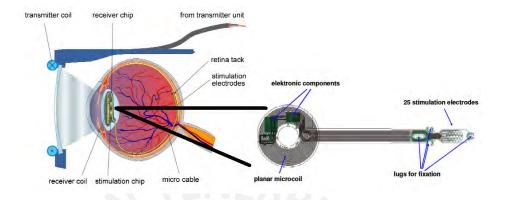

bobina de recepción y una unidad de estimulación conectados a un arreglo de electrodos para la estimulación mediante un micro cable [20]. En la Fig. 2.3 se muestra la disposición física del implante intraocular y la distribución de la bobina de recepción, los chips de recepción y estimulación y el arreglo de electrodos para la estimulación en el empaquetado de polímero.

Figura 2.3: Implante Intraocular del proyecto EPI-RET-3 [20]

El objetivo del chip de estimulación es generar ondas de duración y amplitud específicas según un umbral mínimo de corriente para causar la sensación de fosfenos en el cortex visual. Para ello, se ha logrado un máximo de entrega de carga de 95 mC/cm², con un umbral promedio de estimulación de 15  $\mu$ C/cm². El chip posee un tamaño de 4 mm² y alcanzó una salida de corriente de estimulación máxima de 330  $\mu$ A. Sin embargo, los rangos generados, en la forma de onda, de duración de fases y amplitud fueron [27 – 1526]  $\mu$ s y [0 – 100]  $\mu$ A, respectivamente. Para entender mejor el funcionamiento del estimulador, podemos observar el diagrama de bloques en la Fig. 2.4. En él se utiliza una fuente de corriente programable para conseguir la amplitud de onda deseada para la estimulación [21]. De la misma manera se puede elegir el ancho del pulso, por lo que al final se presenta un máximo de 500 Hz de frecuencia de pulsos.

Figura 2.4: Diagrama de bloques del estimulador [21]

# 2.1.3. Controlador de Corriente con alto voltaje a la salida para una prótesis epiretinal

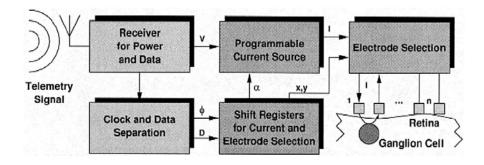

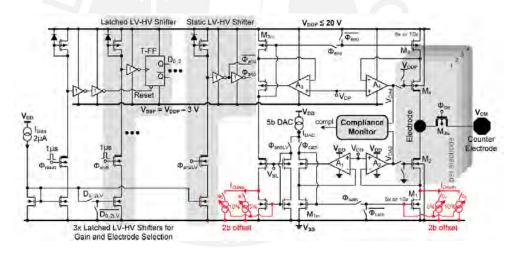

Chen et al. [15] propuso un controlador de corriente que permitía un mejor uso del área dentro del chip utilizando una técnica para aprovechar el área en desuso formada por las tres capas de metal. Asimismo, utilizando un modelo de electrodo con baja impedancia, se consiguió un umbral de corriente de estimulación bajo y por lo tanto, menor disipación de potencia de los estimuladores. El rango de voltaje a la salida es de  $\pm$  10 V para la estimulación, aunque en realidad se posee  $\pm$  12 V y 2 V se utilizan como Headroom Voltage o voltaje de saturación de los transistores de salida. Se consiguieron 256 canales de estimulación, de los cuales cada uno posee un Controlador Digital Local o LDC por sus siglas en inglés y un Controlador de Corriente, cuyo circuito esquemático se muestra en la Fig. 2.5.

Figura 2.5: Arquitectura del Controlador de Corriente propuesto por Chen et al. [15]

En la Fig. 2.5 se pueden distinguir 6 etapas, además del LDC, que conforman al Controlador de Corriente: un DAC o Conversor Analogo Digital, un VGCM o Espejo de Corriente de Ganancia Variable, transistores de protección, Level Shifters, transistor de cancelación de carga y una etapa de salida con transistores de alto voltaje. En general, los parámetros de la forma de onda son interpretados por el DAC, VGCM y Level Shifters en base a las señales digitales del LDC. Luego la etapa de salida de transistores de alto voltaje inyectan la carga al electrodo y consumen 2 V del rango  $\pm$  12 V para saturación. La liberación de carga acumulada por asimetría de la onda bifásica se consigue mediante el transistor HP4 en modo fuertemente triodo, es decir que el voltaje  $V_{DS}$  tiende a 0 V, y una señal proveniente del LDC. Para reducir el área ocupada se utilizaron transistores de bajo voltaje en el DAC, VGCM y LDC, los cuales son diez veces más pequeños que los transistores de alto voltaje.

El Conversor Digital Análogo posee una corriente de referencia de 0.33  $\mu$ A, una resolución de 4 bits y puede generar a la salida una señal entre 0 y 5  $\mu$ A. Se puede

observar que la proporción en escala completa que ofrece cada rama del DAC para la generación de la corriente es de  $\frac{1}{15}$ ,  $\frac{2}{15}$ ,  $\frac{4}{15}$  y  $\frac{8}{15}$ . Esta corriente es luego copiada por LN1 en el VGCM, la cual posee una ganancia de entre 1X y 10X, por lo que la onda de corriente puede alcanzar hasta aquí un máximo de  $50~\mu\text{A}$ . Los transistores de protección HN1, HN2 y HP1 protegen al VGCM de los altos voltajes presentes en la etapa de salida del Controlador de Corriente. Esta última etapa genera ambos pulsos catódico y anódico, cuyo orden es gobernado por dos bits de polaridad provenientes del LDC y se reflejan en los interruptores Scath y Sano. Asimismo posee una ganancia de 10X por lo que a la salida se puede obtener un rango máximo de  $500~\mu\text{A}$  en la onda de corriente de estimulación.

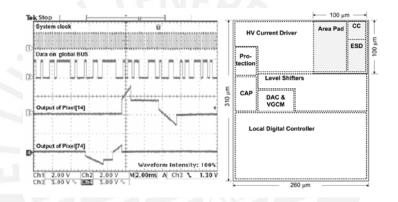

En la Fig. 2.6 se puede observar el alto rango de voltaje a la salida medido y el layout o distribución física de los bloques diseñados dentro del Controlador de Corriente, utilizando la técnica de efficient pad para aprovechar 100  $\mu$ m X 100  $\mu$ m de las tres capas de metal.

Figura 2.6: Forma de onda a la salida del controlador de corriente y layout del mismo [15].

# 2.1.4. Controlador de Corriente con monitoreo y demultiplexación de salidas

Noorsal et al. [10] diseñó un Controlador de Corriente con duración de pulso programable y alto rango de voltaje a la salida, pero además con monitoreo del voltaje a la salida para conseguir una fuente de voltaje adaptable a las necesidades de carga y corriente de estimulación. Cada Controlador de Corriente genera 4 salidas para 4 electrodos mediante un demultiplexor, mide  $0.2 \ mm^2$  y posee un rango de voltaje a la salida máximo de  $\pm 20 \ V$  y una salida máxima de  $1 \ mA$ .

La conversión de las señales digitales con información de la forma de onda estimulante a señales analógicas se consigue mediante un DAC de 2 referencias de corriente o LSB  $(0.8~\mu\text{A}/~3.2~\mu\text{A})$  de 6 bits: 5 bit para la resolución del DAC y 1 bit para la

selección del bit menos significativo o LSB por sus siglas en inglés. Existe un bit extra para la elección de ganancia del Espejo de Corriente en la etapa de salida, de 5X o 10X. A la salida podemos obtener, por lo tanto, 4 rangos de corriente de estimulación: 4-124  $\mu$ A, 8-248  $\mu$ A, 16-496  $\mu$ A y 32-992 [22]. Además del DAC implementado, existen Level Shifters, una fuente de corriente con alto rango de voltaje, un monitor de rango de voltaje a la salida y un demultiplexor 1:4 para que cada canal pueda estimular 4 electrodos.

La arquitectura del Controlador de Corriente propuesto se muestra en la Fig. 2.7. Los transistores de salida M1 y M3 se encuentran en modo triodo fuerte para reducir el voltaje headroom y permitir variaciones en la corriente de salida modificando únicamente los voltajes de sus puertas mediante una configuración de Espejos de Corriente Cascodo Regulado junto con los transistores M1m y M3m que también se encuentran en modo triodo fuerte. De esta manera también se consigue una impedancia de salida alta. Para incrementar la precisión en la forma de onda bifásica se utiliza la técnica gain boosting, por la cual VDS1 y VDS3 llegan a ser iguales. A pesar de ello, existen errores de precisión debido al voltaje umbral VTH cuando existen pequeñas corrientes a la salida, y proporcionales a VSAT o VDS cuando se trata de corrientes grandes y los transistores se encuentran en la región lineal. Por protección contra descargas electrostáticas, el sustrato de los transistores M2 y M4 se encuentran conectados a VSS y VDDP respectivamente.

Figura 2.7: Controlador de Corriente con monitor de salida y demultiplexor 1:4 [10]

El monitoreo se lleva a cabo mediante un mecanismo de realimentación del Cascodo Regulado para la detección del nivel de voltaje a la salida a base de 2 inversores CMOS. Si el Controlador de Corriente está funcionando fuera del rango de voltaje requerido, el monitor permite que esto se pueda identificar para modificar la fuente de voltaje a la salida. El demultiplexor se implementa con 2 biestables Toggle o Flip-Flop T Level Shifters y el control de ganancia del Espejo de Corriente también utiliza un T-FF. Los Level Shifter sirven para controlar la corriente anódica de salida, ya que se necesita pasar de bajos a altos voltajes, como  $V_{DDP}$  y  $V_{SSP}$ .

#### 2.1.5. Espejos de Corriente de bajo voltaje headroom para un Controlador de Corriente

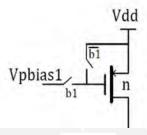

Con el objetivo de permitir un mayor rango de voltaje a la salida a pesar de una operación en bajo voltaje ( $\pm$  2.5 V), Monge et al. [11] utilizó una configuración de espejos de corriente que alcanzaba un alto valor de impedancia a la salida y bajo voltaje headroom o de consumo a la salida. Sin embargo, este incremento en el rango de voltaje de salida implica un incremento en el error debido a asimetría, por lo que se utilizó un circuito de auto calibración para cada canal. Asimismo, el interruptor de alto voltaje utilizado también puede limitar el voltaje a la salida del Controlador de Corriente, con el fin de no sobrepasar un máximo de 2.5 V en el voltaje que será aplicado a los electrodos. Ambos circuitos propuestos se pueden observar en la Fig. 2.8.

Figura 2.8: Implementación del (a) espejo de corriente de bajo consumo e (b) interruptor de alto voltaje [11]

A pesar que los transistores de alto voltaje sirven para el límite de voltaje a la salida, estos acumulan una carga debido al efecto cuerpo durante el retardo entre fases y la fase de descarga. Para poder eliminar esta carga acumulada, se utiliza un interruptor que se cierra previo a la estimulación. La etapa de salida está conformada por 6 transistores I/O de 2.5 V. Los transistores de los extremos deben recibir un voltaje cercano a  $V_{DD}$  y  $V_{SS}$ , ya que los espejos de corriente que generan las ondas catódica y anódica consumen dichos voltajes, por lo que para asegurar la saturación de ellos es necesario colocar  $V_{DD}$  y  $V_{SS}$  en las puertas de ellos. Los otros transistores de alto voltaje reciben un voltaje apropiado para evitar alcanzar voltajes entre sus terminales mayores al límite que pueden soportar, durante cada una de las fases anódica y catódica.

# 2.2. Cuadro comparativo de parámetros utilizados en trabajos previos

En el cuadro 2.1 se muestran los parámetros utilizados en trabajos previos para el diseño de un Controlador de Corriente. Estos serán utilizados como referencia para establecer las especificaciones del circuito a diseñar.

Para el presente trabajo se eligió la topología SCCT o Self-Cascode Composite-Transistor [26] con el fin de reducir el consumo de área ocupada por los pixeles de estimulación en el chip, manteniendo valores de impedancia y rango de voltaje a la salida altos, como en el caso de Monge et al. [11]. En la sección 3.3. Topología propuesta se brindan mayores detalles del motivo de la elección.

Tabla 2.1: Cuadro comparativo de especificaciones utilizadas en el estado del arte

| Parámetro                   | Chen et al.[15]                            | Noorsal et al.[10]                           | Monge et al.[11]                              |  |

|-----------------------------|--------------------------------------------|----------------------------------------------|-----------------------------------------------|--|

| Topología utilizada         | Múltiples voltajes mediante Level Shifters | Espejos de corriente<br>Cascodo Triodo Regu- | Espejos de corriente de bajo voltaje headroom |  |

| N./1                        | 256                                        | lado                                         | F10                                           |  |

| Número de canales           | 256                                        | 1024                                         | 512                                           |  |

| Area de un pi-              | $0.08034 \ mm^2$                           | $0.05875 \ mm^2$                             | $0.0169 \ mm^2$                               |  |

| xel de estimulación         |                                            |                                              |                                               |  |

| (Controlador de co-         |                                            |                                              |                                               |  |

| rriente, calibración        |                                            |                                              |                                               |  |

| y lógica local)             | 100 4                                      | 51117                                        |                                               |  |

| Umbral de estimu-<br>lación | $100 \ \mu A$                              |                                              | 7                                             |  |

| Modelo de electro-          | $10 \text{ K}\Omega + 100 \text{ nF}$      | $3.46~\mathrm{K}\Omega+110~\mathrm{nF}$      | $30 \text{ K}\Omega + 100 \text{ nF}$         |  |

| do                          |                                            |                                              |                                               |  |

| Electrodos por Ca-          | 1                                          | 4                                            | 1                                             |  |

| nal                         |                                            |                                              |                                               |  |

| Rango de Voltaje a          | ± 10 V                                     | $\pm 10 \text{ V}$                           | $\pm 2.4 \text{ V}$                           |  |

| la Salida                   | 14000                                      |                                              |                                               |  |

| Resolución de DAC           | 4 bit                                      | 6 bit                                        | 5 bit                                         |  |

| $I_{REF}$                   | $0.33~\mu\mathrm{A}$                       | $0.8 - 3.2 \ \mu A$                          | $1 \mu A$                                     |  |

| Error INL/DNL               | 0.16 LSB / 0.16 LSB                        | -                                            | -                                             |  |

| Ganancia del espejo         | 1X - 10X                                   | -                                            | -                                             |  |

| de corriente                |                                            |                                              |                                               |  |

| Ganancia de la eta-         | 10X                                        | 5X/10X                                       | -                                             |  |

| pa de salida                |                                            |                                              |                                               |  |

| Error de simetría           | 2.9%                                       | 15 %                                         | 2.24%                                         |  |

| Velocidad de datos          | 2 Mbps                                     | 968 Kbps                                     | 20 Mbps                                       |  |

| Disipación de po-           | $1.45~\mathrm{mW}$ @ $100~\mu\mathrm{A}$   | 1.16 mW @ 20 V / 0.41                        | $15~\mathrm{mW}~@~50~\mu\mathrm{A}$           |  |

| tencia                      |                                            | mW @ 5 V                                     |                                               |  |

| Tecnología CMOS             | $0.18~\mu{\rm m}~32~{ m V}$                | $0.35~\mu\mathrm{m}~50~\mathrm{V}$           | 65 nm 1.2 V / 2.5 V                           |  |

## Capítulo 3

# Diseño del Controlador de Corriente

En el presente capítulo se explicará la elección, análisis y diseño de la topología propuesta para cumplir con los requerimientos que han sido elegidos en base al estudio realizado en los capítulos anteriores. Se presenta el funcionamiento básico del controlador de corriente en la primera sección de este capítulo. Las especificaciones se muestran en la segunda sección. Asimismo, se discute el tipo de simulación necesaria para poder definir las dimensiones del circuito y verificar su desempeño. En la tercera sección se presentan las topologías que van a ser utilizadas, el diagrama de bloques y el diagrama esquemático del controlador de corriente. En la cuarta sección se realiza el análisis en larga señal, donde son consideradas las condiciones bajo las cuales los transistores entran en las diferentes regiones de operación, se analiza la impedancia de salida y los compromisos entre diferentes parámetros del transistor. Finalmente, se presenta el dimensionamiento de los transistores que componen cada bloque del sistema propuesto.

El proceso de diseño de circuitos integrados seguido corresponde a la metodología obtenida de [23], donde: el primer paso corresponde a la definición de requerimientos del circuito, entradas y salidas del sistema; el segundo paso, al cálculo manual de parámetros utilizando una ecuación del transistor; tercero, al conjunto de simulaciones que permitan ajustar los parámetros calculados hasta alcanzar especificaciones; cuarto, diseño de layout o disposición física del circuito. Asimismo, existen pasos adicionales, como simulación post-layout, fabricación de prototipo, pruebas y correcciones en el prototipo, y por último, producción.

Para realizar los cálculos de punto de operación y dimensionamiento de transistores, el modelo cuadrático del transistor ha sido considerado porque permite relacionar fácilmente los parámetros de factor de forma y corriente en el drenador y se puede realizar un análisis de trade-offs de manera más intuitiva. El modelo de transistor utilizado en las simulaciones es el BSIM3v3 level 53 (Berkeley Short-Channel IGFET Model 3 version 3) (IGFET- Insulated Gate Field-Effect Transistor) desarrollado por el BSIM Research Group de la Universidad de California [24], ya que es el modelo que permite el uso de la tecnología am<br/>s $0.35~\mu m$  en el programa de simulación SPECTRE con un modelo SPICE compatible para predecir el funcionamiento del circuito [25]. El modelo de transistor utilizado en nuestra topología soporta 5 V entre sus terminales debido a que posee una puerta de mayor grosor denominada mid-oxide de 15 nm típicamente, lo que incrementa su voltaje umbral. El nombre del modelo en la tecnología utilizada es NMOSM o PMOSM. El circuito fue implementado utilizando el entorno de trabajo <br/> Virtuoso y simulado mediante la herramienta <br/> Spectre Circuit Simulator de Cadence.

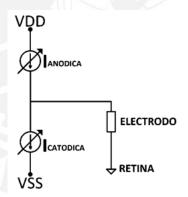

#### 3.1. Funcionamiento del Controlador de Corriente

La idea de inyectar y retirar una carga del tejido neuronal de la retina, simbolizado como una impedancia, se ejemplifica en la Fig. 3.1. El funcionamiento básico del circuito a diseñar corresponde al de la activación alternada de una fuente de corriente anódica y otra catódica, cuyo valor de corriente se pueda controlar de manera digital según la forma de onda que se desea inducir en un determinado punto del arreglo de electrodo. Este mismo modelo se aplicará a cada canal, asociado a un electrodo, que componga el neuroestimulador y debe asegurar bajos niveles de consumo de potencia y área, ya que estos parámetros incrementarán linealmente con el número de canales a ser implementados, los cuales pueden llegar a miles según el estado del arte.

Figura 3.1: Funcionamiento del Controlador de Corriente o Current Driver

A pesar que las fuentes de corriente utilizadas deberían ser ideales, en nuestro diseño no lo son. Es por ello que la impedancia de salida a alcanzar por el controlador de corriente debe ser muy alta y está relacionada directamente al valor de la impedancia del interfaz electrodo-retina. Sin embargo, la elección de dicho requerimiento no puede tomarse en función de esta única necesidad, puesto que existen otros condicionantes como el rango de voltaje permitido a la salida y consumo de área que limitaran los posibles valores a ser alcanzados. Estos compromisos existentes entre los parámetros de diseño serán estudiados en las siguientes secciones.

### 3.2. Especificaciones

Para poder definir los requerimientos, es necesario constatar las entradas y salidas de todo el circuito a diseñar. En primer lugar, se contará con 4 bits digitales de entrada para definir la amplitud de la onda de corriente a generar a la salida, tanto para el caso anódico (BP0, BP1, BP2 y BP3) como para el catódico (BN0, BN2, BN2 y BN3), y 1 bit (CK) para activar la descarga del electrodo cuando no existe estimulación positiva o negativa. En segundo lugar, para la polarización de los transistores se cuenta con una corriente de entrada de referencia (IREFP para onda anódica e IREFN para onda catódica), la cual, en nuestro caso particular, ha sido elegida igual a la corriente mínima generada a la salida del circuito, es decir la corriente de LSB (Least Significant Bit o Bit Menos Significativo), con el fin de evitar una rama extra de ganancia en el circuito de copia de corriente. Las fuentes de voltaje son  $V_{DD}$  y  $V_{SS}$ , dado que se tomara 0V como voltaje de referencia en la retina. En la etapa de salida, la forma de onda se generara por el pin de salida (OUT), que se conectara al electrodo, y se tendrá el pin del voltaje de referencia de la retina (RETINA), para la etapa de descarga.

Tabla 3.1: Especificaciones para el diseño del Controlador de Corriente

| Requerimiento       | Mínimo | Máximo | Valor fijo | Unidades              |

|---------------------|--------|--------|------------|-----------------------|

| Rango de voltaje a  | -2.2   | 2.2    |            | V                     |

| la salida           |        |        |            |                       |

| Rango de corriente  | -55    | 55     | -/1 1 1    | $\mu$ A               |

| a la salida         |        | 11111  |            |                       |

| Impedancia de sali- | 1.5    | SIL    |            | $M\Omega$             |

| da                  |        |        |            |                       |

| Voltaje headroom    |        | 0.4    | 8//        | V                     |

| Disipación de po-   |        | 1      |            | mW                    |

| tencia              |        |        | 1          |                       |

| Resolución DAC      |        |        | 4          | bits                  |

| Modelo de electro-  | 1011   | 7111   | 30 / 100   | KΩ / nF               |

| do                  | JCM)   |        |            |                       |

| Corriente de refe-  |        |        | 3.67       | $\mu$ A               |

| rencia              |        |        |            |                       |

| Voltaje de alimen-  |        |        | $\pm 2.5$  | V                     |

| tación              |        |        |            |                       |

| Área                |        | 0.02   |            | $mm^2$                |

| Slew rate           | 5      |        |            | $\frac{\mu A}{\mu S}$ |

La Tabla 3.1 muestra los rangos de valores que los parámetros del circuito a diseñar deben cumplir. Los requerimientos que han sido seleccionados para el presente diseño provienen del estudio realizado con respecto a los controladores de corriente que ya han sido desarrollados [10] [11] [15], y el Cuadro comparativo de especificaciones

utilizadas en el estado del arte presentado en la Tabla 2.1. El rango de corriente y la resolución de los conversores digital analógico a utilizar se tomaron debido al umbral de estimulación de las celular ganglionares discutido en [12] y los valores que ya han sido utilizados en otros trabajos. La corriente de referencia de entrada al circuito se obtuvo en base al requerimiento del rango de corriente y resolución de cada DAC a implementar. Debido a que el interfaz electrodo-retina representa una impedancia alta, cuyo modelo fue elegido en base a un electrodo Platino/Iridio de 100  $\mu$ m de diámetro utilizado en [11], entonces para cumplir con un rango de corriente de 55  $\mu$ A a la salida, se necesita un rango de voltaje que permita este flujo de carga. La elección del modelo de transistor utilizado se relaciona a este rango de voltaje deseado.

El voltaje de alimentación para todo el circuito es elegido en base al rango de voltaje deseado a la salida y el voltaje máximo permitido entre los terminales de los transistores, es decir, va relacionado a la tecnología. Por ello, es elegida la tecnología AMS  $0.35~\mu m$  mid-oxide con un rango de 5 V entre los terminales del transistor. Se debe tomar en cuenta que en otros trabajos se utilizaron valores mayores de alimentación, así como múltiples niveles, debido a que: los transistores utilizados eran modelos High Voltage y permitian un mayor rango de voltaje entre sus terminales; mayores valores de corriente a ser inducidos en el electrodo; ganancias múltiples en la copia de corriente a la etapa de salida; y modelos de electrodo con impedancias más altas. Son elegidos dos niveles de alimentación porque se va a inyectar y retirar una carga en un tejido orgánico cuyo valor de potencial electrostático promedio es 0 V, y para poder inducir una corriente entrante y otra saliente en la carga que simboliza el electrodo es necesario producir un voltaje positivo o negativo a la salida del circuito, respectivamente.

Para realizar el análisis de un circuito que trabaja con señales digitales y analógicas, es necesario realizar dos tipos de simulaciones. En primer lugar, el análisis en larga señal por medio de simulaciones DC permitirá obtener el punto de operación deseado de cada transistor, para asegurar una polarización que cumpla con los requerimientos establecidos (bajo voltaje de saturación, corriente de polarización debida). Asimismo, se podrán encontrar las dimensiones necesarias para asegurar una impedancia de salida alta. Para ello, se tiene que observar el comportamiento de los parámetros que se desean optimizar mientras se realiza un barrido de valores de otro parámetro controlable, como las dimensiones del transistor o el volta je puerta-surtidor. En segundo lugar, es necesario realizar también una simulación transitorio para poder medir el desempeño del controlador de corriente al generar la forma de onda deseada donde se pueda observar la diferencia entre el cambio en la salida para un intervalo de tiempo ideal y real. Esto se analizará más adelante mediante el slew rate, que consiste en el cambio permitido de voltaje/corriente por unidad de tiempo. Finalmente, se podrá generar la forma de onda deseada, utilizando los valores de bits y periodos correctos, recomendados en [12].

### 3.3. Topología propuesta

Se ha diseñado un Controlador de Corriente en base a la generación de la forma de onda bifásica por medio de un PDAC y NDAC en modo corriente para la onda anódica y catódica respectivamente. Ambos conversores de señal digital a analógica han sido implementados por espejos de corriente simple utilizando la topología de Transistor Compuesto o SCCT (Self Cascode Composite Transistor). Para permitir el control por medio de las señales digitales provenientes del Controlador Digital Local, el cual no se implementa en la presente tesis, se han utilizado transistores de 5V de canal corto en la tecnología  $0.35~\mu m$  a manera de interruptores, cuyo estado de abierto o cerrado depende de una señal digital en la puerta del transistor. Para desactivar alguno de los conversores mientras el otro se encuentra generando la forma de onda, se han utilizado puertas NOT o inversores que puedan generar la señal digital negada correspondiente.

#### 3.3.1. Diagrama de bloques y diagrama esquemático

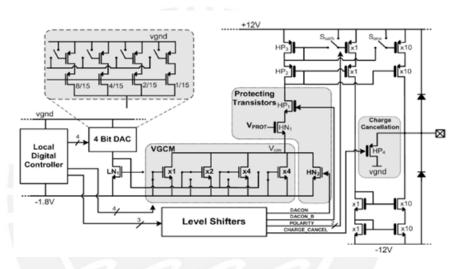

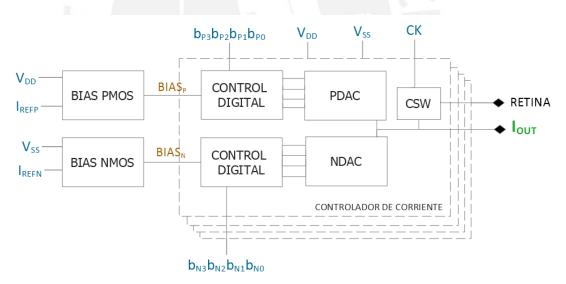

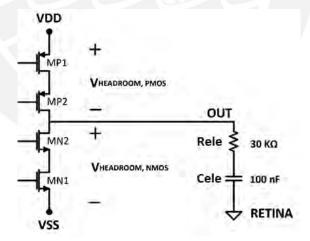

En el diagrama de bloques de la Fig. 3.2 se observan ambos circuitos de polarización BIAS NMOSM y BIAS PMOSM que definen el punto de operación de los transistores de salida en los conversores.

Figura 3.2: Diagrama de bloques del Controlador de Corriente

Por medio de compuertas NOT e interruptores, que conforman los bloques de CONTROL DIGITAL, se permite la activación de los transistores en los conversores PDAC y NDAC, al conmutar la puerta de ellos entre el voltaje de polarización BIAS y la alimentación VDD o VSS. Los parámetros de color azul representan las entradas y fuentes del Controlador de Corriente, los de color marrón son voltajes internos

que han sido generados y utilizados en el mismo circuito, y finalmente el parámetro de color verde representa la salida del sistema. Dado que el circuito de polarización puede ser compartido por más de un canal, existe la posibilidad de implementar más canales (controladores de corriente) para más electrodos con el fin de incrementar la resolución del neuroestimulador. Se ha utilizado un modelo de electrodo como una carga compuesta por una resistencia de 30 K $\Omega$  en serie con un condensador de 100 nF [11].

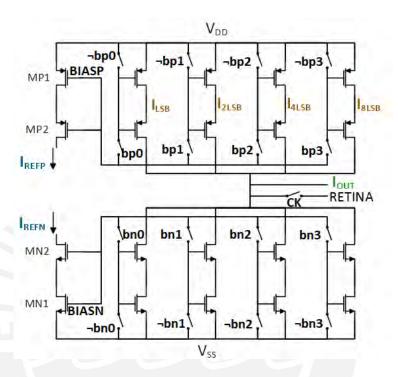

Figura 3.3: Diagrama Esquemático del Controlador de Corriente

En el diagrama esquemático de la Fig. 3.3 se puede observar la implementación de los bloques del controlador de corriente a nivel transistor. Los transistores MN1, MN2, MP1 y MP2 forman los circuitos de polarización, mientras que los demás transistores conforman las ramas de los conversores PDAC y NDAC que generan diferentes niveles de corriente. Se pueden diferenciar 4 niveles de corriente en función a los 4 bits de resolución que recibe cada conversor para generar la forma de onda bifásica. Para la activación y desactivación de las ramas de los conversores, se han colocado interruptores controlados por los bits de entrada, que polarizan o no a la rama indicada al conmutar la puerta de los transistores del conversor entre el voltaje BIAS y la fuente  $V_{DD}$  o  $V_{SS}$ .

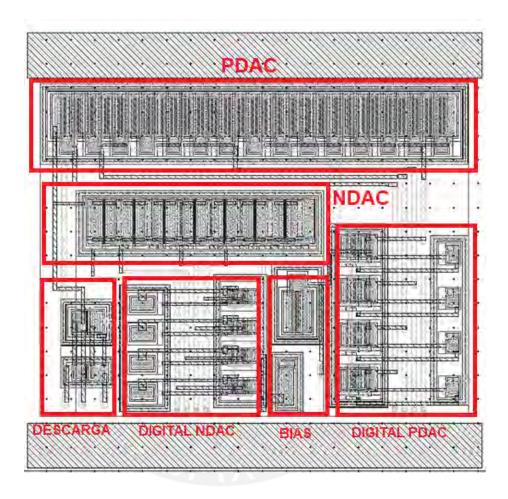

# 3.3.2. Transistor compuesto o Self Cascode Composite Transistor (SCCT)

Se ha elegido la topología SCCT de transistor compuesto para los espejos de corriente simple que componen a los conversores, ya que combina las ventajas de un arreglo cascodo de alta impedancia de salida y un espejo simple con bajo voltaje headroom, lo que permite utilizarlo en aplicaciones de bajo voltaje, que en nuestro caso se traduce en un mayor rango de voltaje a la salida. Otra ventaja que ofrece dicha topología, es la reducción en el consumo de área dentro del dispositivo, como se demuestra en [26], y es expresado en el Capítulo 4, sección 4.5. Disposición física del controlador de corriente.

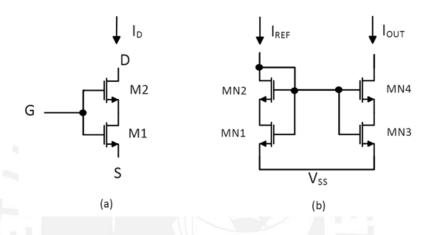

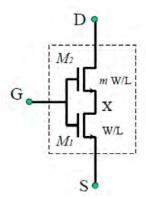

Figura 3.4: (a) Topologia de transistor compuesto o SCCT-Self Cascode Composite Transistor (b) Espejo de corriente simple utilizando topología SCCT [26]

El transistor compuesto, mostrado en la Fig. 3.4(a), está conformado por M1 y M2. Dado que comparten la misma puerta y la misma corriente en el drenador, asumiendo un voltaje fijo de surtidor en M1, podemos analizar las regiones de operación de ambos transistores a partir de las siguientes ecuaciones, asociadas a la activación de los transistores y la relación entre los voltajes  $V_{GS}$ .

$$V_{GS2} - V_{TH2} > 0 (3.1)$$

$$V_{GS1} - V_{TH1} > 0 (3.2)$$

$$V_{GS1} - V_{DS1} = V_{GS2} (3.3)$$

Dado que el transistor M2 tiene el sustrato conectado al surtidor de M1, y por el efecto cuerpo, podemos deducir las siguientes ecuaciones:

$$V_{SB2} = V_{DS1} (3.4)$$

$$V_{TH2} > V_{TH1} \tag{3.5}$$

$$V_{DSAT1} \approx V_{GS1} - V_{TH2} > V_{DS1}$$

(3.6)

Como el voltaje  $V_{SB2}$  es diferente de 0, entonces  $V_{TH2}$  incrementa por el efecto cuerpo. Como consecuencia, en la ecuación 3.6 se puede observar que el voltaje  $V_{DS1}$  es menor al necesario para que el transistor pueda estar en saturación, con lo que queda demostrado que M1 se encuentra en la región triodo.

Asimismo, como dicho voltaje  $V_{DS1}$  puede ser muy pequeño, se demuestra que el voltaje de saturación necesitado a la salida del circuito es  $V_{DSAT2}$ . El factor de forma del transistor M2 suele elegirse m veces el factor de forma del transistor M1, como parte de la topología SCCT [26]. Es por ello que la elección de  $\frac{W}{L}$  para el transistor M1 y la elección de m se discutirán con mayor detalle en la sección 3.4. Análisis en larga señal, así como el cálculo del voltaje de saturación y el voltaje headroom.

El espejo de corriente utilizando la topología SCCT se muestra en la Fig. 3.4(b). Los transistores MN1 y MN2 conforman la rama de polarización y se encuentran en una configuración diodo, por lo que definirán el punto de operación de la rama de salida conformada por MN3 y MN4, mediante el voltaje Overdrive  $(V_{OV})$ . Las ramas de polarización NMOS y PMOS conforman los bloques BIAS de la Fig. 3.2.

#### 3.3.3. Conversor Digital-Análogo en modo corriente

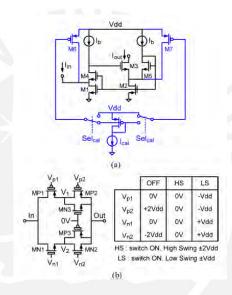

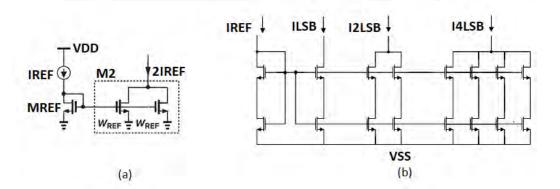

Figura 3.5: (a) Técnica para incrementar precisión de la copia de corriente al evitar duplicar ancho del transistor [27] (b) Técnica aplicada al NDAC del controlador de corriente

Los conversores PDAC y NDAC están compuestos por etapas de salida del espejo de corriente simple SCCT, donde las ramas que implicaban mayor corriente (múltiplos 2X, 4X y 8X de LSB) fueron implementadas utilizando una técnica para incrementar precisión en la copia. Dado que se ha elegido mantener el largo del transistor constante, con el fin de reducir *mismatch* para los que comparten mismo voltaje en la puerta,

y como el ancho de los transistores no está definido precisamente, por los efectos de *side-diffusion* y *corners* [27], entonces se utiliza una rama de ganancia unitaria que se repite para poder alcanzar la ganancia de corriente deseada, como se muestra en la Fig. 3.5.

#### 3.3.4. Circuitos de control digital

Con el fin de permitir el control digital de la fuente de corriente a partir de bits digitales provenientes de un circuito previo, denominado Controlador Digital Local, se ha adoptado el circuito de conmutación descrito en [32], mostrado en la Fig. 3.6.

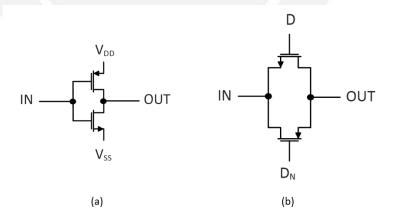

Figura 3.6: Circuito de conmutación de rama PDAC [28]

Se utiliza un MOSFET para cada interruptor, conmutando la puerta entre dos niveles lógicos, con el fin de forzar al transistor a ingresar a las regiones de Saturación o corte, según la necesidad del circuito. Dado que se necesita el valor negado de un bit de entrada, se implementó una puerta NOT utilizando la topología conformada por un transistor NMOSM y un PMOSM, como se muestra en la Fig. 3.7(a).

Figura 3.7: (a) Puerta NOT (b) Interruptor complementario [27]

Dado que a la salida del circuito se encuentran voltajes que varían entre -2.2 V y +2.2 V, es necesario considerar un interruptor que permita un alto rango de voltaje

entre sus terminales, es decir, un mayor swing, para poder realizar la descarga del electrodo en la última etapa de la forma de onda de estimulación. Por ello, se coloca a la salida del circuito, en paralelo al electrodo, un interruptor complementario, el cual es gobernado por la señal D (Discharge) y  $D_N$ , valor negado de la misma.

#### 3.4. Análisis en larga señal