| dc.contributor.advisor | Saldaña Pumarica, Julio César | es_ES |

| dc.contributor.author | Garayar Leyva, Guillermo Gabriel | es_ES |

| dc.date.accessioned | 2014-07-22T20:25:29Z | es_ES |

| dc.date.available | 2014-07-22T20:25:29Z | es_ES |

| dc.date.created | 2014 | es_ES |

| dc.date.issued | 2014-07-22 | es_ES |

| dc.identifier.uri | http://hdl.handle.net/20.500.12404/5445 | |

| dc.description.abstract | En el presente trabajo de tesis se realizó el diseño de un circuito de protección contra

ataques del tipo Differential Power Analysis (DPA) aplicado a tarjetas inteligentes. Este tipo

de tarjetas presenta la misma apariencia física de una tarjeta de crédito pero en su

estructura cuenta con un circuito integrado.

Se utilizó la tecnología AMS 0.35m de la compañía Austriamicrosystem, y se aplicó la

técnica denominada Atenuación de Corriente. Esta se basa en la implementación de un

circuito ubicado entre la fuente de alimentación y el procesador criptográfico de la tarjeta

inteligente, el cual logra disminuir las variaciones de consumo de corriente presentes

durante una operación criptográfica.

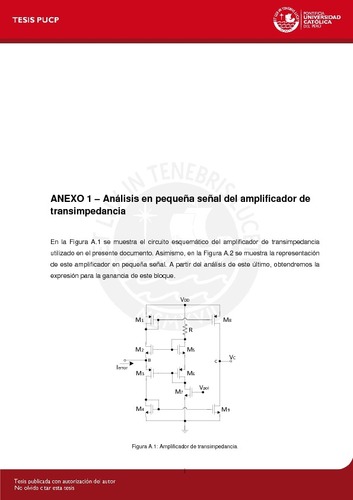

El circuito de protección se dividió en tres bloques: Sensor de Corriente, Amplificador de

Transimpedancia e Inyector de Corriente. Cada uno de estos bloques fue diseñado tomando

criterios del diseño de circuitos integrados analógicos, tales como consumo de potencia,

área ocupada y ganancia. Para esta etapa de diseño se utilizó el modelo Level 1 del

transistor MOSFET.

Posteriormente, se realizaron simulaciones a cada uno de los bloques del circuito de

protección usando el software Cadence. Finalmente, una vez alcanzados los requerimientos

establecidos, se procedió al desarrollo del layout físico del circuito diseñado.

El circuito diseñado logra una atenuación de las variaciones de consumo de corriente del

86%. Entre sus principales características se puede mencionar que consume 35.5mW ,

ocupa 2 60000m y presenta 96MHz de ancho de banda. | es_ES |

| dc.language.iso | spa | es_ES |

| dc.publisher | Pontificia Universidad Católica del Perú | es_ES |

| dc.rights | Atribución-NoComercial-SinDerivadas 2.5 Perú | * |

| dc.rights | info:eu-repo/semantics/openAccess | es_ES |

| dc.rights.uri | http://creativecommons.org/licenses/by-nc-nd/2.5/pe/ | * |

| dc.subject | Tarjetas inteligentes | es_ES |

| dc.subject | Protección de datos | es_ES |

| dc.subject | CMOS (Electrónica) | es_ES |

| dc.title | Diseño de circuito de protección contra extracción de información secreta en tarjetas inteligentes | es_ES |

| dc.type | info:eu-repo/semantics/bachelorThesis | es_ES |

| thesis.degree.name | Ingeniero Electrónico | es_ES |

| thesis.degree.level | Título Profesional | es_ES |

| thesis.degree.grantor | Pontificia Universidad Católica del Perú. Facultad de Ciencias e Ingeniería | es_ES |

| thesis.degree.discipline | Ingeniería Electrónica | es_ES |

| renati.advisor.dni | 10123705 | |

| renati.discipline | 712026 | es_ES |

| renati.level | https://purl.org/pe-repo/renati/level#tituloProfesional | es_ES |

| renati.type | https://purl.org/pe-repo/renati/type#tesis | es_ES |

| dc.publisher.country | PE | es_ES |

| dc.subject.ocde | https://purl.org/pe-repo/ocde/ford#2.02.01 | es_ES |