| dc.contributor.advisor | Monge, Manuel | es_ES |

| dc.contributor.advisor | Raffo, Mario | es_ES |

| dc.contributor.author | Naveda Paz, José Martín | es_ES |

| dc.date.accessioned | 2019-02-21T23:11:25Z | es_ES |

| dc.date.available | 2019-02-21T23:11:25Z | es_ES |

| dc.date.created | 2019 | es_ES |

| dc.date.issued | 2019-02-21 | es_ES |

| dc.identifier.uri | http://hdl.handle.net/20.500.12404/13541 | |

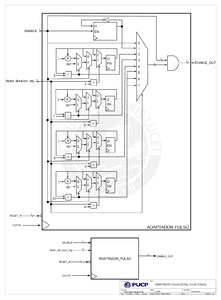

| dc.description.abstract | El presente trabajo consiste en el diseño de un controlador digital para un estimulador

de prótesis epiretinal que está conformada por una cámara, un procesador de video, la

caja de componentes electrónicos con el controlador incluido y el arreglo de electrodos.

Esta prótesis se implanta quirúrgicamente en el paciente que sufre de enfermedades

degenerativas de la retina como Retinitis Pigmentosa y Degeneración Macular

relacionada con la edad. Las entradas del controlador serán enviadas por un controlador

global y las salidas del controlador a un estimulador que usando un arreglo de

micro-electrodos estimularía directamente a las neuronas retinales saludables pasando

sobre las células fotorreceptoras dañadas por la enfermedad.

La forma de onda, periodo, duración, retraso de cada fase y amplitud son importantes

para el correcto estimulo de las células neuronales de la retina, por estas razones se

diseñó un controlador flexible basado en el diseño ITBCS13 [1] que es capaz de cambiar

parámetros y formas de onda de estimulación [2, 3] de forma independiente por canal.

Asimismo la corriente de estimulación debe ser bifásica debido a que reduce las cargas

residuales que da˜nan el tejido de la retina, por ende la estimulación tendrá una fase

catódica y anódica [4].

El controlador digital genera en cuatro canales las formas de onda Senodial,

Gaussiana, Rectangular y Triangular a través de las 8 señales de entrada que recibe del

controlador global: req, fase, forma onda, tiempo entre fases, tiempo descarga,

amplitud, factor duración y reset. Las salidas del controlador al estimulador de cuatro

canales serán las fases anódicas, catódicas y la amplitud de la onda: anódico reg ,

catódico reg y amplitud reg.

El diseño del controlador es basado en bloques digitales, codificados por medio del

lenguaje de descripción de hardware VHDL. Para realizar la verificación y validación del

funcionamiento de dicha descripción se usó la simulación por medio de Testbench en

VHDL, empleándose el software ModelSimAltera de la compañía Mentor Graphics [5].

Para la implementación se empleó un FPGA de la familia Cyclone II (tecnología TSMC’s

90-nm) [6]. La frecuencia de operación del controlador es de 164.69 MHz. | es_ES |

| dc.language.iso | spa | es_ES |

| dc.publisher | Pontificia Universidad Católica del Perú | es_ES |

| dc.rights | Atribución-CompartirIgual 2.5 Perú | * |

| dc.rights | info:eu-repo/semantics/openAccess | es_ES |

| dc.rights.uri | http://creativecommons.org/licenses/by-sa/2.5/pe/ | * |

| dc.subject | Control automático | es_ES |

| dc.subject | Sistemas de control digital | es_ES |

| dc.subject | Prótesis | es_ES |

| dc.subject | VHDL (Lenguaje de descripción de hardware) | es_ES |

| dc.title | Diseño de un controlador digital para un estimulador de prótesis epiretinal | es_ES |

| dc.type | info:eu-repo/semantics/bachelorThesis | es_ES |

| thesis.degree.name | Ingeniero Electrónico | es_ES |

| thesis.degree.level | Título Profesional | es_ES |

| thesis.degree.grantor | Pontificia Universidad Católica del Perú. Facultad de Ciencias e Ingeniería | es_ES |

| thesis.degree.discipline | Ingeniería Electrónica | es_ES |

| renati.discipline | 712026 | es_ES |

| renati.level | https://purl.org/pe-repo/renati/level#tituloProfesional | es_ES |

| renati.type | https://purl.org/pe-repo/renati/type#tesis | es_ES |

| dc.publisher.country | PE | es_ES |

| dc.subject.ocde | https://purl.org/pe-repo/ocde/ford#2.02.01 | es_ES |