### PONTIFICIA UNIVERSIDAD CATÓLICA DEL PERÚ

Esta obra ha sido publicada bajo la licencia Creative Commons

Reconocimiento-No comercial-Compartir bajo la misma licencia 2.5 Perú.

Para ver una copia de dicha licencia, visite

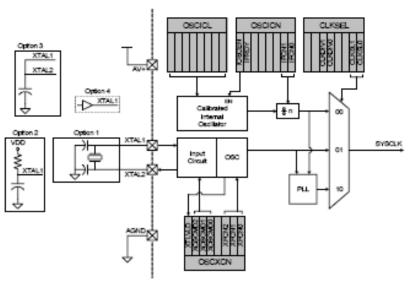

http://creativecommons.org/licenses/by-nc-sa/2.5/pe/

# PONTIFICIA UNIVERSIDAD CATÓLICA DEL PERÚ FACULTAD DE CIENCIAS E INGENIERÍA

## DISEÑO DEL SISTEMA DE ILUMINACIÓN AUTOMATIZADO PARA UNA OFICINA EN UN EDIFICIO INTELIGENTE, BASADO EN TECNOLOGÍA INALÁMBRICA ZIGBEE

Tesis para optar el Título de Ingeniero Electrónico

Presentado por:

MIGUEL EDUARDO HIDALGO ALCALÁ

Lima - Perú 2007

| NDICE TO THE REPORT OF THE PROPERTY OF THE PRO | Pág.       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| NTRODUCCIÓN:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5          |

| CAPÍTULO 1: EL MANEJO DE LA ILUMINACIÓN EN OFICINAS DE L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A          |

| CUIDAD DE LIMA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7          |

| 1.1. Proceso actual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7          |

| 1.1.1. Infraestructura.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7          |

| 1.1.2. Políticas.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8          |

| 1.2. Deficiencias del manejo de la iluminación en edificaciones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>.</b> 8 |

| 1.3. Declaración del marco problemático                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9          |

| CAPÍTULO 2: MÉTODOS Y TECNOLOGÍAS DISPONIBLES PARA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| CONTROLAR LA INTENSIDAD DE LA ILUMINACIÓN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11         |

| 2.1. Estado del arte.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11         |

| 2.1.1. Tipos de sistemas.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12         |

| 2.1.2. Tecnologías de comunicación disponibles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14         |

| 2.2. Conceptualizaciones generales                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17         |

| 2.2.1. Sistemas de iluminación                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17         |

| 2.2.1.1 Definición                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17         |

| 2.2.1.2 Modos de control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17         |

| 2.2.1.3 Productos utilizados actualmente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18         |

| 2.2.2 Edificio Inteligente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18         |

| 2.2.2.1 Definición                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19         |

| 2.2.2.2 Subsistemas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19         |

| 2.2.3 Tecnología ZigBee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20         |

| 2.2.3.1 Definición                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20         |

| 2.2.3.2 Características                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20         |

| 2.2.3.3 Frecuencia, ancho de banda y número de canales     | 20 |

|------------------------------------------------------------|----|

| 2.2.3.4 Características de los paquetes transmitidos       | 21 |

| CAPÍTULO 3: REQUERIMIENTOS PARA EL DISEÑO DEL SISTEMA D    | E  |

| CONTROL BASADO EN TECNOLOGÍA INALÁMBRICA                   | 22 |

| 3.1. Hipótesis de la investigación                         | 22 |

| 3.1.1. Hipótesis principal                                 | 22 |

| 3.1.2. Hipótesis secundarias                               | 22 |

| 3.2. Objetivos de la investigación.                        | 23 |

| 3.2.1. Objetivo General                                    | 23 |

| 3.2.2. Objetivos Específicos.                              | 23 |

| 3.3. Universo y muestra.                                   | 24 |

| 3.4. Situación actual y tecnologías disponibles para la    |    |

| optimización                                               | 24 |

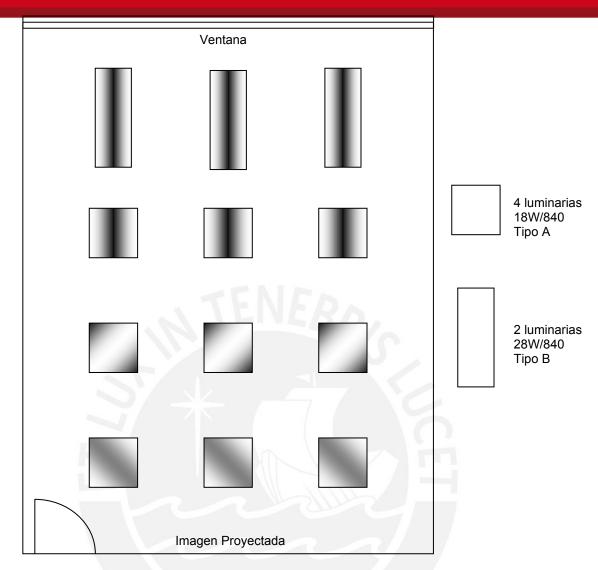

| 3.4.1. Distribución actual de las luminarias               | 24 |

| 3.4.2. Detalle de las luminarias actuales                  | 28 |

| 3.4.3. Balastos y balastos electrónicos                    | 29 |

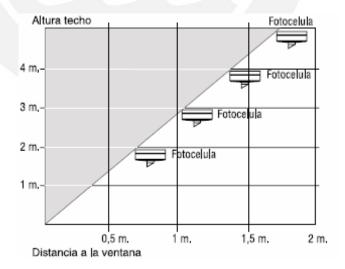

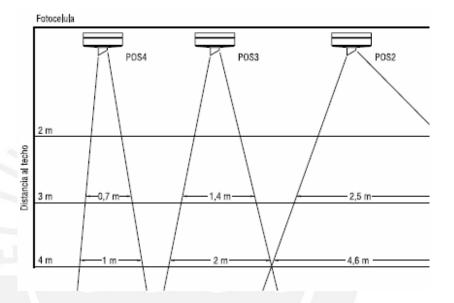

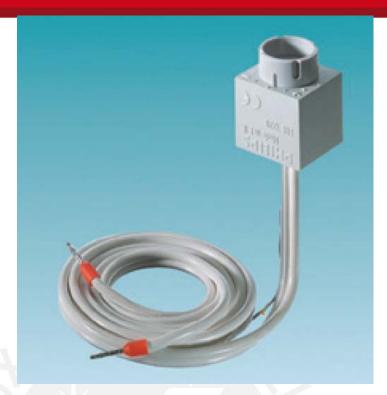

| 3.4.4. Sensor de luz, fotosensor o fotocélula              | 31 |

| 3.5. Interpretando los datos: Determinación de la solución | 32 |

| 3.5.1. Luminarias                                          | 32 |

| 3.5.2. Balastos electrónicos                               | 32 |

| 3.5.3. Fotocélula                                          | 37 |

| 3.5.4. Comunicación inalámbrica                            | 40 |

| CAPÍTULO 4: DISEÑO DEL SISTEMA DE REGULACIÓN PARA UNA      |    |

| OFICINA EN LIMA                                            | 44 |

| 4.1. Consideraciones preliminares.                         | 44 |

| 4.2. Análisis y diseño del sistema                          | 44   |

|-------------------------------------------------------------|------|

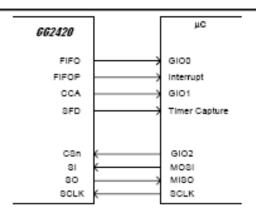

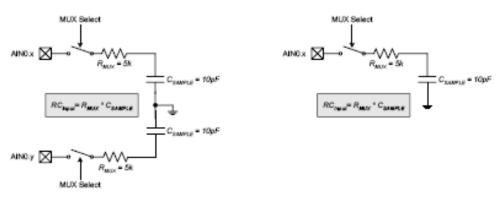

| 4.2.1. El microcontrolador                                  | 45   |

| 4.2.2. Transmisor-receptor de radiofrecuencia de 2.4 GHz IE | EE   |

| 802.15.4                                                    | 46   |

| 4.2.3. La antena                                            | 48   |

| 4.3. Desarrollo de la solución                              | 51   |

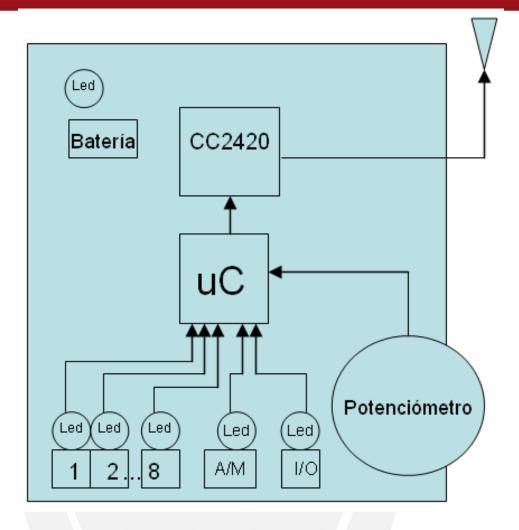

| 4.3.1. Módulo de control maestro (transmisor)               | 53   |

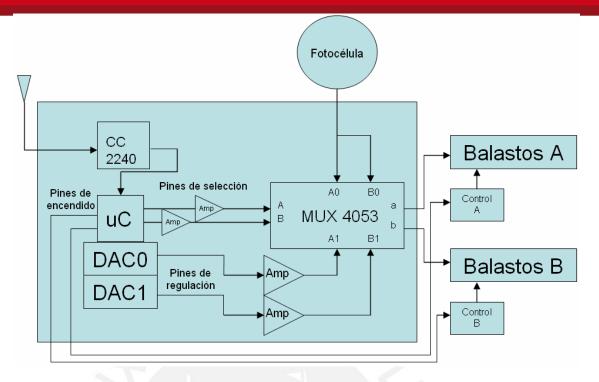

| 4.4. Módulo de regulación de la iluminación (receptor)      | 55   |

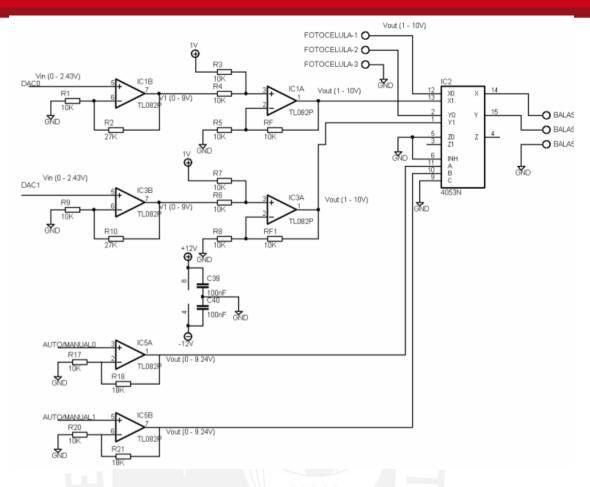

| 4.4.1. Multiplexor analógico.                               | 56   |

| 4.4.2. Acondicionamiento de la señal del conversor          |      |

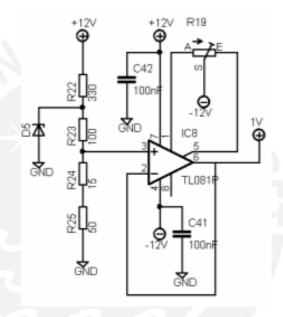

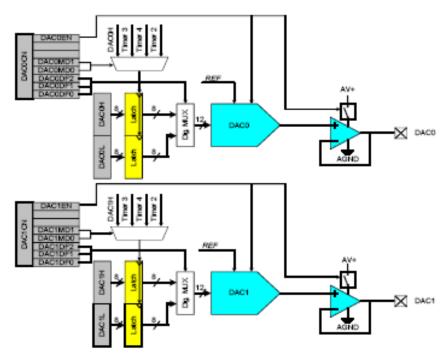

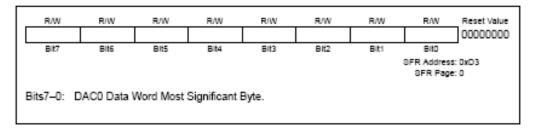

| digital/análogo                                             | 57   |

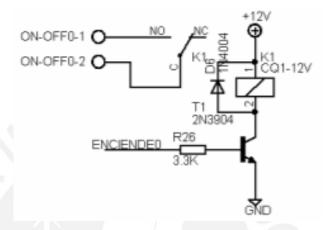

| 4.4.3. Acondicionamiento de la señal de control de encendi  | do y |

| apagado de las luminarias                                   | 60   |

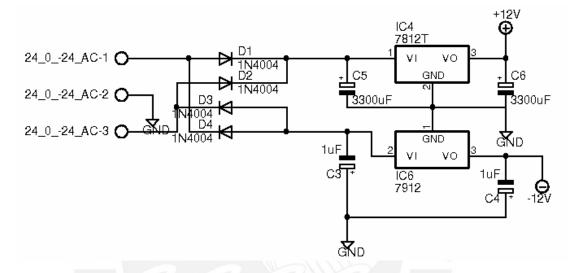

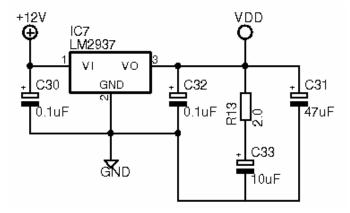

| 4.4.4. Fuentes de alimentación.                             | 61   |

| 4.5. Simulación de la instalación y funcionamiento          | 63   |

| 4.5.1. Lógica del programa                                  | 64   |

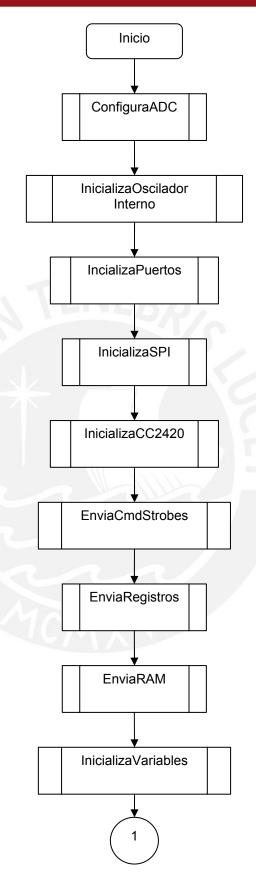

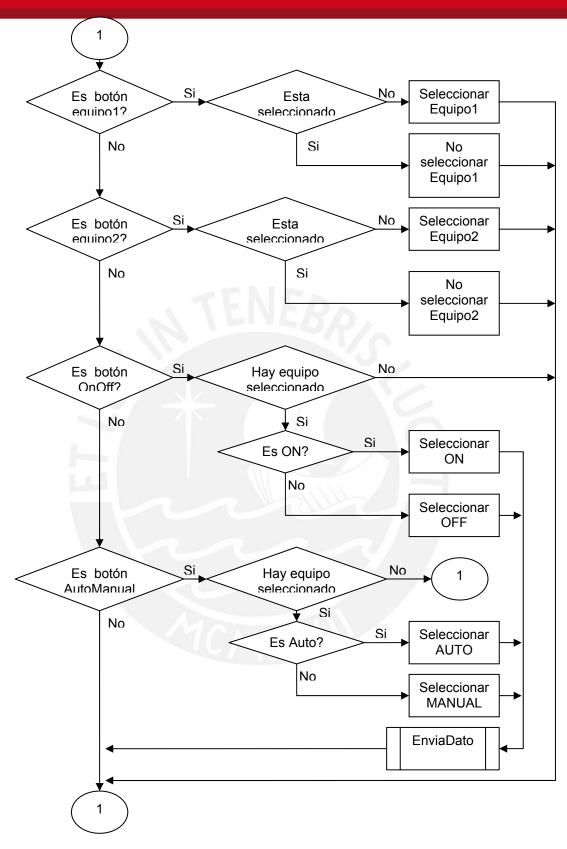

| 4.5.1.1. Programa de transmisión                            | 66   |

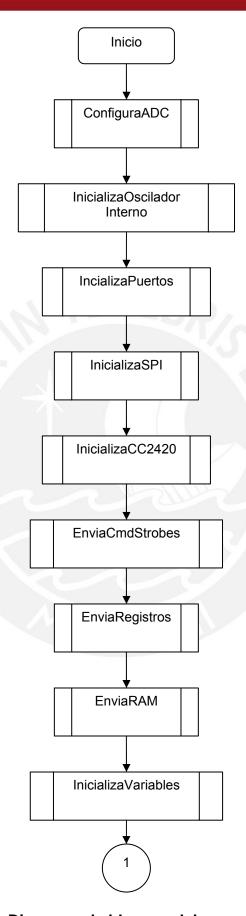

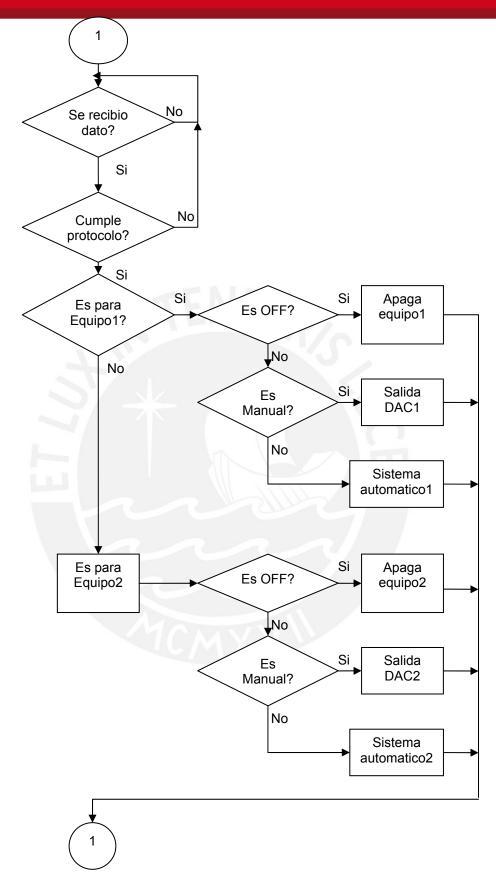

| 4.5.1.2. Programa de recepción                              | 70   |

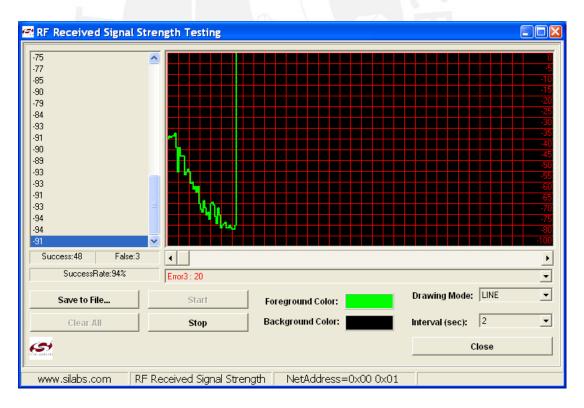

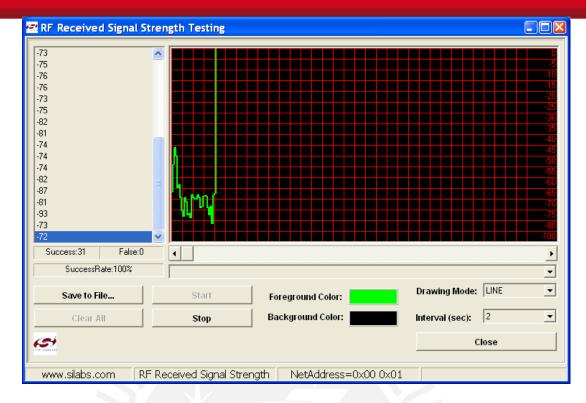

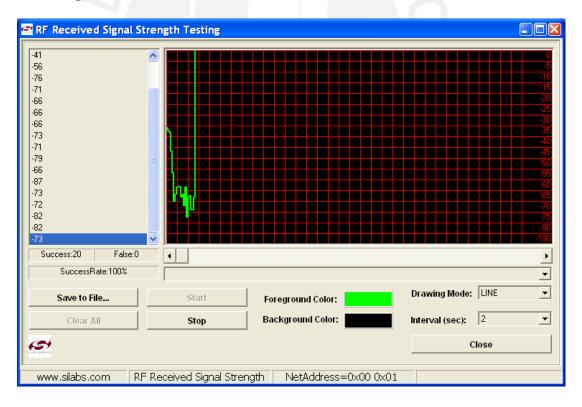

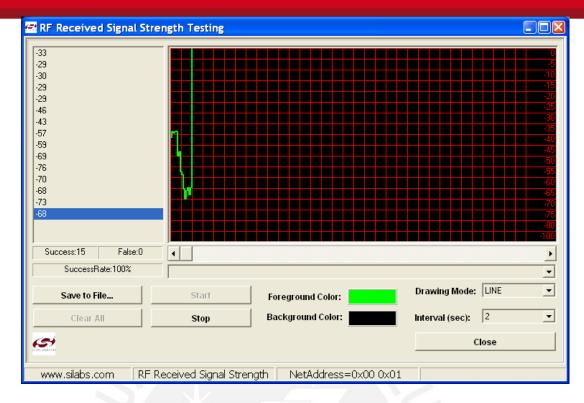

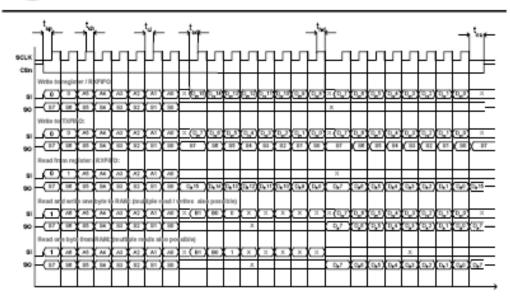

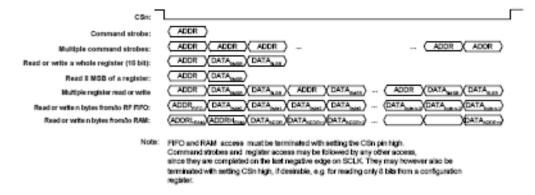

| 4.5.2. Pruebas de los programas                             | 73   |

| 4.6. Presupuesto                                            | 81   |

| CONCLUSIONES Y RECOMENDACIONES                              | 85   |

| FUENTES                                                     | 88   |

| Bibliografía                                                | 88   |

| Documentos                                                  | 89   |

#### INTRODUCCIÓN:

En la actualidad, en la ciudad de Lima hay un sin número de oficinas de diversa índole para atender los distintos niveles y rubros de la industria.

Sin embargo, sólo las nuevas construcciones tienen cierto grado de automatización y normalmente está orientado al control de la temperatura (aire acondicionado). Prácticamente ninguna oficina cuenta con automatización en la iluminación y, las que lo hacen, lo limitan al encendido y apagado automático de las luces de los baños, cuando el gasto de energía eléctrica más grande lo están realizando la iluminación de la oficina en sí y los monitores de las computadoras.

El manejo de los monitores es sencillo debido a que se pueden configurar fácilmente para que se apaguen luego de un tiempo específico de inactividad, pero en cuanto a la iluminación, lo más cercano a ahorro que se ha pretendido lograr a un nivel macro es instalar luces fluorescentes de menor consumo de energía, distribuirlas de manera que las luces estén sectorizadas y que cada sector esté comandado por un interruptor diferente. Si bien estas medidas ayudan, no son del todo eficientes, debido a que es común que alguna luz este prendida innecesariamente.

En nuestros días, donde la tecnología la llevamos a donde sea que vayamos, ya sea en un celular, en una memoria flash USB de gran capacidad, en un reproductor de música MP3, etc.; lo más lógico es que la tecnología esté donde sea que lleguemos y aquí es donde empieza a formarse el concepto de los edificios inteligentes.

El presente documento pretende mostrar una manera de ahorrar la energía eléctrica utilizada para la iluminación en una oficina, administrando su uso de

acuerdo a la demanda, no sólo en algo tan básico como encenderla sólo cuando va a ser utilizada y apagarla en caso contrario, sino en algo más elaborado como regular su intensidad de acuerdo a la necesidad y lograr realizarlo por sectores y de manera remota.

## CAPITULO 1: EL MANEJO DE LA ILUMINACIÓN EN OFICINAS DE LA CUIDAD DE LIMA.

#### 1.1. Proceso actual.

El proceso actual del manejo de la iluminación es una actividad simple y cotidiana que se realiza de manera manual mediante el uso de interruptores. Básicamente lo que sucede es que se observa el ambiente en general y, sobretodo, la zona de trabajo. Luego, se procede a encender luces o apagarlas de acuerdo a la necesidad, procurando lograr un ambiente adecuado y lo suficientemente cómodo como para realizar una tarea específica. En ocasiones, de ser el caso, suelen abrirse o cerrarse persianas y/o cortinas para ayudar a conseguir la intensidad luminosa deseada. Por lo tanto, la activación y desactivación se produce bajo demanda y de manera aleatoria en el tiempo.

En resumen, lo que se tiene es un sistema basado en prueba y error, que se regula luego de largos intervalos de tiempo y que, muchas veces, es regulado de una manera inadecuada.

#### 1.1.1. Infraestructura.

Existen diferentes tipos y niveles de iluminación para distintos tipos de oficinas. En el caso de esta oficina, en la que se trabaja en cubículos frente a un computador la mayor parte del tiempo, la iluminación es controlada por varios interruptores correspondientes a distintos sectores. Además presenta diferentes ambientes que requieren distinta iluminación.

#### 1.1.2. Políticas.

El Código Nacional de Electricidad del Perú estipula cómo debe ser la instalación y el cableado de las luminarias, así como cuántas luminarias y de qué tipo deben usarse para conseguir la iluminación adecuada según el tipo de trabajo a realizarse.

Sin embargo, la oficina en cuestión está en funcionamiento desde mediados del año 2006 y ha sido revisada por organismos reguladores que inspeccionaron las instalaciones y autorizaron su funcionamiento. Además, lo que más interesa para efectos del presente proyecto son los estándares y las normas reguladoras existentes en lo referente a la comunicación entre dispositivos de control. Desde detalles acerca de cómo debe ser el cableado o instalación de los mismos, hasta los formatos de las tramas de información de los diferentes protocolos que existen.

El objetivo de revisar los documentos reguladores es poder conocer mejor los estándares y las normas que deben cumplirse para poder desarrollar un sistema más flexible y adaptable, tratando de reducir al mínimo los problemas de interoperabilidad que puedan presentarse.

#### 1.2. Deficiencias del manejo de la iluminación en edificaciones.

En el proceso actual se han observado algunas deficiencias:

Necesariamente tiene que haber alguien alrededor para poder modificar el estado de la iluminación: Alguien tiene que encender o apagar las luces para controlar la intensidad luminosa, ya sea para incrementarla o para disminuirla.

- Como el manejo de la intensidad de la iluminación es manual y mediante interruptores, se obliga al usuario a que el control tenga que ser desde el punto en el que esta ubicado dicho interruptor.

- Por el mismo hecho que la iluminación sólo puede controlarse desde el interruptor, es usual que haya luminarias encendidas innecesariamente porque a los usuarios les cuesta acercarse a apagarlas o simplemente porque no se dan cuenta que la iluminación es escasa hasta que dicho suceso se hace realmente molesto.

#### 1.3. Declaración del marco problemático.

Actualmente, el sistema de iluminación en las oficinas es controlado de manera manual y centralizado, lo que produce que, en muchas ocasiones, la intensidad de la iluminación no sea la adecuada para el tipo de trabajo que se va a realizar. Cabe destacar además, que el control actual no se ajusta a la tendencia que tiene la sociedad al ahorro y al cuidado del ahorro.

Los dos posibles problemas frente a esto son: que la iluminación sea escasa, en cuyo caso el trabajo de oficina puede producir incomodidad, jaquecas y cansancio excesivo innecesario; o que la iluminación sea abundante, lo que produce un consumo energético y desgaste de luminarias innecesario. En ambos casos, los problemas producen un desperdicio económico para la empresa. En el primer caso, es una disminución en el rendimiento del empleado y en el

segundo, es un monto mayor el que se pagará en el recibo de la luz y las luminarias se tendrán que cambiar más seguido.

### CAPITULO 2: MÉTODOS Y TECNOLOGÍAS DISPONIBLES PARA CONTROLAR LA INTENSIDAD DE LA ILUMINACIÓN.

#### 2.1. Estado del arte.

La energía eléctrica es la forma de energía más utilizada. Gracias a la flexibilidad en la generación y a que el transporte por líneas de alta tensión es sumamente ventajoso, se ha convertido para la industria en la forma más grande de consumo de energía.

Los inconvenientes de esta forma de energía son la imposibilidad de almacenamiento en grandes cantidades y que las líneas de transmisión son muy costosas y por estos motivos, el ahorro de energía eléctrica es un tema que siempre es de interés.

Actualmente, existen diversas maneras de regular el uso de la energía eléctrica, sin embargo, en el Perú, específicamente en Lima, aún no se ha logrado hacer de una manera realmente eficiente. Además, según un estudio realizado en Venezuela y plasmado en el "Manual de diseño para edificaciones energéticamente eficientes", se sabe que a nivel de toda Latino América cerca del 60% de la energía eléctrica generada es destinada al sector comercial y residencial y cerca del 40% de esta es destinada a iluminación. En este sentido el control de la iluminación es un tema importante para conseguir un ahorro significativo de energía.

De lo que estamos hablando ahora es de domótica (edificios y viviendas inteligentes), aunque realmente sólo estamos entrando en la base de esta, porque es la integración de sistemas automatizados la que realmente se define como tal. Sin embargo, el principio es el mismo debido a que en la actualidad contamos con estándares que hacen posible dicha integración entre diversos sistemas automatizados, así que nos referiremos a domótica porque justamente el desarrollo de este diseño estará buscando la posterior integración a un sistema de mayor envergadura.

#### 2.1.1. Tipos de sistemas.

Existen claramente dos tipos de sistemas domóticos: Los sistemas basados en corrientes portadoras, utilizando la red de baja tensión ya instalada y los sistemas que utilizan su propia red para la interconexión de dispositivos.

• Sistemas mediante corrientes portadoras: Tienen la gran ventaja de no necesitar un cableado adicional para su instalación y que su aplicación en edificios ya construidos es inmediata. La desventaja es la complejidad de sus dispositivos, debido a que son necesarios moduladores y demoduladores en todos los elementos del sistema ya que la información va superpuesta a la red eléctrica. Además, aunque se adicionen filtros para recuperar claramente los datos enviados, la misma red eléctrica utilizada como soporte de transmisión puede influir

en el correcto funcionamiento porque introduce numerosas interferencias y, debido a la necesidad física de conexión para el transporte de los datos, tampoco es posible hacer que la información se transmita a través de transformadores.

Existen principalmente tres sistemas comerciales: X-10 de Home Systems, que fue la primera tecnología en la industria para comunicaciones entre dispositivos domóticos y aún está ampliamente disponible (fue desarrollada en 1975 por Pico Electronics - Escocia); CAD de Legrand y Global Home System de Landis & Gyr.

Sistemas que utilizan su propia red de datos: Pueden ser alámbricos o inalámbricos, pero en cualquiera de los dos casos pueden ser sistemas centralizados, donde existe un dispositivo encargado de procesar la información recibida de los sensores y transmisores para enviar órdenes a los actuadotes correspondientes, o sistemas distribuidos, donde cada elemento tiene la capacidad de tratar la información que recibe y actuar de forma autónoma. En la Tabla 1 se muestran las principales ventajas y desventajas de cada uno de estos sistemas.

|                         | Ventajas                                                                       | Desventajas                                                                                                                 |  |

|-------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Sistema<br>centralizado | Bajo costo - No necesita módulos especiales de direccionamiento.               | Flexibilidad limitada - Las posibles reconfiguraciones serán muy costosas.                                                  |  |

|                         | Instalación sencilla - Posibilita la utilización de gran cantidad de elementos | Dependencia de la<br>unidad de control - Si<br>esta falla, todo el sistema<br>deja de funcionar.<br>Cableado - Se necesitan |  |

|                         | convencionales.                                                                | más metros de cable que en el caso del sistema distribuido.                                                                 |  |

| 11:                     | Sistemas más potentes -<br>Permiten implementar<br>gran cantidad de            | Programación compleja -<br>Utiliza software<br>especializado.                                                               |  |

| Sistema<br>distribuido  | aplicaciones.  Cableado - Se necesitan menos metros de cable.                  | Es costoso - Debido a la<br>necesidad de incluir<br>protocolos CSMA/CD y                                                    |  |

|                         | Mayor flexibilidad -<br>Facilidad de<br>reconfiguración.                       | poseer capacidad de procesamiento, lo que implica necesidad de compatibilidad.                                              |  |

Tabla 1: Ventajas y desventajas de los sistemas con red de datos

#### propia

#### 2.1.2. Tecnologías de comunicación disponibles.

En lo referente a la comunicación, el método utilizado por el sistema X-10 (que comunica los dispositivos por la red eléctrica), ya no es lo suficientemente robusto para las demandas actuales de los consumidores y las compañías que se disputan el mercado, tanto en los medios alámbricos como inalámbricos, son la Alianza ZigBee (que utiliza el estándar Zigbee), Smarthome (que utiliza Insteon) y Zensys (que utiliza Z-Wave):

Insteon: Utiliza una tecnología que se basa tanto en radiofrecuencia (RF) (entre 902-924MHz), como en el sistema mediante corrientes portadoras (ya sea a 110 o 220 V).

El vicepresidente de Smarthome, Ken Fairbanks [10], dice que cada mensaje o transmisión es propagada a través de RF y la línea de alimentación. Explica que las viviendas son lugares en los cuales es difícil hacer que la RF trabaje de manera confiable y la naturaleza dual del Insteon crea una red robusta. Su RF tiene alcances de 45 mts., es compatible con dispositivos X-10 y permite la integración con computadoras.

**Z-Wave:** Es un protocolo completamente inalámbrico que utiliza banda angosta para transmitir sus comandos de control y data menor (no tiene suficiente ancho de banda para audio o video). Trabaja a una frecuencia de 908MHz y permite la formación de redes, en las que todos los dispositivos apoyan al sistema actuando cada uno como su propio repetidor.

Según Michael Einstein, vocero de marketing en Z-Wave, una de las principales ventajas sobre los productos X-10, es la seguridad. Afirma que mientras que con X-10 sólo se pueden tener 256 identificadores (IDs) únicos y una persona podría estar prendiendo o apagando la luz de un vecino o abriendo y cerrando la puerta del garaje de otro por errores de IDs duplicados, Z-Wave tiene cerca de cuatro billones de IDs únicos. Este protocolo también permite integración con

computadoras mediante comunicación serial (RS232 y USB) para control remoto.

**ZigBee:** Es un estándar de comunicación inalámbrica que está siendo muy utilizada para las aplicaciones de domótica, ya que, entre otras cosas, puede formar su propia red con gran número de dispositivos y prescindir del cableado, además de posibilitar el control remoto.

También permite formar redes de tipo estrella, rejilla o árbol; mediante la utilización de tres tipos de dispositivos [8]:

- Coordinador de red: Encargado de mantener información general de la red y tiene los mayores requisitos de memoria y capacidad de procesado.

- Función completa: Soporta todas las funciones definidas por el estándar IEEE 802.15.4 (Redes WPAN) y ZigBee. Además, puede funcionar como coordinador de red.

- Función reducida: Implementan sólo una parte de las funciones de acuerdo con su tarea. Esta funcionalidad permite que sea de menor costo y complejidad y, por lo tanto, de mayor consumo.

El protocolo ZigBee fue creado con la intención de satisfacer las necesidades del mercado de conexiones inalámbricas de bajo costo, bajo consumo de energía, bajas velocidades de transmisión y seguridad moderada. Los dispositivos Zigbee cuentan con una dirección MAC única, lo que evita que haya problemas de IDs duplicados y hace que las redes que se quieran formar puedan tener

un número de dispositivos muy elevado. Además, tiene un alcance entre 10 y 75 metros dependiendo del entorno y opera en tres bandas libres para cumplir con los requerimientos mundiales: En la banda de 2.4GHz. a 250kbps (global), en la de 915MHz. a 40kbps (EE.UU.) y en la de 868MHz (Europa). a 20kbps. Es importante destacar que el método de modulación es distinto si se opera en la banda de 2.4GHz (O-QPSK) o en las bandas 915/868MHz (BPSK) [2].

#### 2.2. Conceptualizaciones generales.

#### 2.2.1. Sistemas de iluminación

Las estrategias para el control de iluminación pueden jugar un papel significativo en la reducción del costo de energía [11].

#### 2.2.1.1 Definición

Sistema compuesto por fuentes de luz instaladas y distribuidas de tal manera que se optimice el confort visual para la adecuada realización de una determinada actividad [15].

#### 2.2.1.2 Modos de control

Existen dos modos de control de un sistema de iluminación. Los de alto voltaje y los de bajo voltaje:

Alto voltaje: Normalmente utilizan temporizadores de alto voltaje,

Ilaves de alta tensión y contactores. Son costos y requieren un amplio margen de seguridad [11].

Bajo voltaje: Utilizan interruptores comunes y en ocasiones se automatiza el encendido y apagado mediante el uso de sensores.

Son más seguros y más costo-efectivos [11].

#### 2.2.1.3 <u>Productos utilizados actualmente</u>

Principalmente son cuatro:

- Lámparas incandescentes: Termo-radiadores compuestos por un filamento metálico en forma de espiral, alojado en el interior de una ampolla de vidrio [12].

- Lámparas de vapor de mercurio: Lámparas eléctricas de descarga en las que la emisión de radiaciones luminosas se debe a la excitación de los átomos de mercurio contenidos en el tubo de descarga [12].

- Lámparas de vapor de sodio: Fuentes luminosas en las que la producción de luz se efectúa como consecuencia a la excitación de los átomos de sodio contenidos en el tubo de descarga [12].

- Lámparas Fluorescentes: Aquellas lámparas de descarga en atmósfera de mercurio a baja presión en las que la generación de luz se debe principalmente, al fenómeno de fotoluminiscencia [12].

#### 2.2.2 Edificio Inteligente

Los edificios cada vez son más complejos y sus regulaciones de gobierno más rectas, especialmente con respecto a la seguridad de la vida [12].

#### 2.2.2.1 Definición

Se define como edificio inteligente a aquel que provee un ambiente productivo y costo-efectivo a través de la optimización de su estructura, sistema, servicio y administración así como a la interrelación entre ellos [11].

También se define como el edificio que incluye todo el hardware, software, cableado e incidentes que son parte del sistema de supervisión, control y funciones de monitoreo necesarias para su automatización integral [12].

#### 2.2.2.2 Subsistemas

Existen varios tipos de subsistemas que pueden o no, estar incluidos en un edificio inteligente y se mencionan a continuación:

- Control de energía Que incluye administración y regulaciones en el uso de la energía eléctrica en todos los artefactos que la utilizan [9][11][12].

- Calefacción, ventilación y aire acondicionado (HVAC) Para mantener un ambiente y una temperatura apropiadas de acuerdo a las necesidades del local [9][11][12].

- Incendios Manejo de alarmas y rociadores para advertir,

contener y extinguir un incendio [9][11][12].

- Seguridad Con el uso de cámaras, alarmas y control de accesos ante intrusiones no deseadas [9][11][12].

- Transporte y tráfico Brindándole inteligencia a los ascensores para una mejor administración de su uso [9][12].

- Contaminación Calidad del aire en el exterior e interior y manejo adecuado de desechos tóxicos [9][12].

- Comunicación Calidad y seguridad en la misma, ya sea cableada o inalámbrica [12].

- Plomería Haciendo posible la automatización del suministro de agua y activación del drenaje [11][12].

#### 2.2.3 Tecnología ZigBee

#### 2.2.3.1 Definición

Estándar de comunicación inalámbrica de corto alcance, destinada a la electrónica de consumo y al control industrial; permitiendo el control remoto, sensado y uso de aplicaciones [2][13].

#### 2.2.3.2 Características

Establece comunicaciones inalámbricas entre dispositivos y está centrado en aplicaciones de bajo coste y consumo [2], es ideal para locales aislados y ha sido implementado con el estándar 802.15.4 que define las capas física y MAC (Medium Access Control) [13]. Además puede conectar hasta 255 nodos por red y es un fácil protocolo de definición porque es implementable en microcontroladores de bajo costo [2].

#### 2.2.3.3 Frecuencia, ancho de banda y número de canales

Estos tres parámetros varían dependiendo de la ubicación geográfica y se resumen en la **Tabla 2**.

|                 | Frecuencia | BW       | Nº de canales |

|-----------------|------------|----------|---------------|

| Europa          | 868 MHz    | 20 Kbps  | 1             |

| EE.UU.          | 915 MHz    | 40 Kbps  | 10            |

| Resto del mundo | 2.4 GHz    | 250 Kbps | 16            |

Tabla 2: Características de la señal Zigbee

#### 2.2.3.4 Características de los paquetes transmitidos

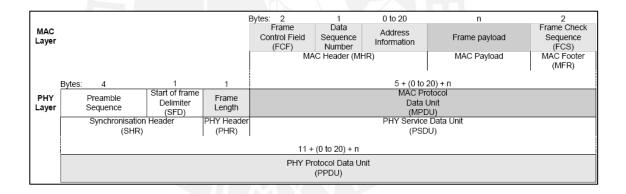

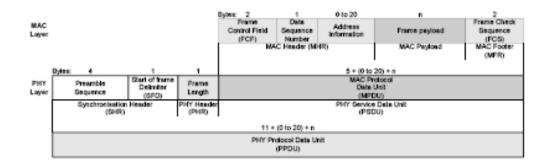

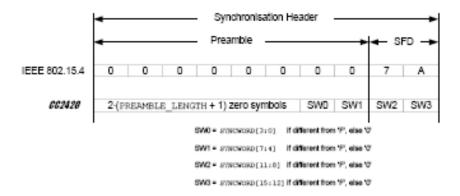

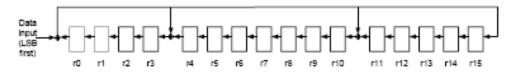

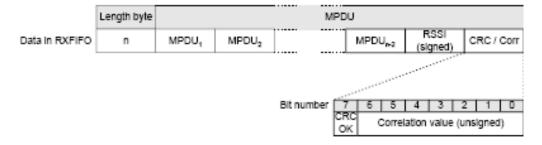

Tamaño máximo: 128 bytes (incluyendo) el encabezado [6].

Para asegurar operaciones confiables utiliza una técnica llamada Carrier Sense Multiple Access (CSMA), que consiste en transmitir sólo cuando nadie mas lo esta haciendo [6][13].

Permite enviar los paquetes en un orden que obedece a una prioridad determinada [6].

### CAPÍTULO 3: REQUERIMIENTOS PARA EL DISEÑO DEL SISTEMA DE CONTROL BASADO EN TECNOLOGÍA INALÁMBRICA.

#### 3.1. Hipótesis de la investigación.

#### 3.1.1. Hipótesis principal

Dado que en Lima el control de la iluminación es manual, se regula ocasionalmente (generando en muchas ocasiones abundancia o escasez de luz) y no se automatiza porque la interconexión de dispositivos requiere una serie de esfuerzos que suelen considerarse innecesarios; entonces un sistema de regulación de la iluminación, que se pueda controlar de manera inalámbrica, permitirá optimizar el uso de los recursos para generar un ahorro en el consumo de energía e incrementar el grado de confort, sin requerir de un cableado adicional.

#### 3.1.2. Hipótesis secundarias

- 1) Utilizar un estándar en la comunicación entre dispositivos permitirá la posterior integración con otros sistemas automatizados para lograr generar un sistema de mayor envergadura.

- 2) Los sistemas automatizados permiten que el proceso de control sea continuo y reprogramable ante algún cambio en cuanto a la intensidad luminosa necesaria en un determinado sector.

- 3) El uso de un sistema automatizado para el control de la iluminación debería evitar el desperdicio de energía eléctrica, optimizando el uso de los recursos disponibles para lograr un ahorro económico.

- 4) El empleo de un sistema de control inalámbrico posibilita la implementación de dichos sistemas en ambientes que originalmente no fueron pensados para tales fines, eliminando el trabajo de cableado necesario.

- 5) El uso de un sistema de control que brinde la cantidad de luz necesaria en todo momento, incrementará el grado de confort de las personas que trabajen en el área.

#### 3.2. Objetivos de la investigación.

#### 3.2.1. Objetivo General.

Diseñar un sistema regulable e inalámbrico para controlar la intensidad luminosa en un ambiente de trabajo de acuerdo a sus propias necesidades, maximizando el grado de confort y reduciendo el desperdicio de la energía eléctrica.

#### 3.2.2. Objetivos Específicos.

- 1) Evitar el exceso o la falta de iluminación; por lo tanto, proporcionar sólo la intensidad luminosa necesaria para la actividad a realizar, a menos que el usuario desee graduar la intensidad manualmente.

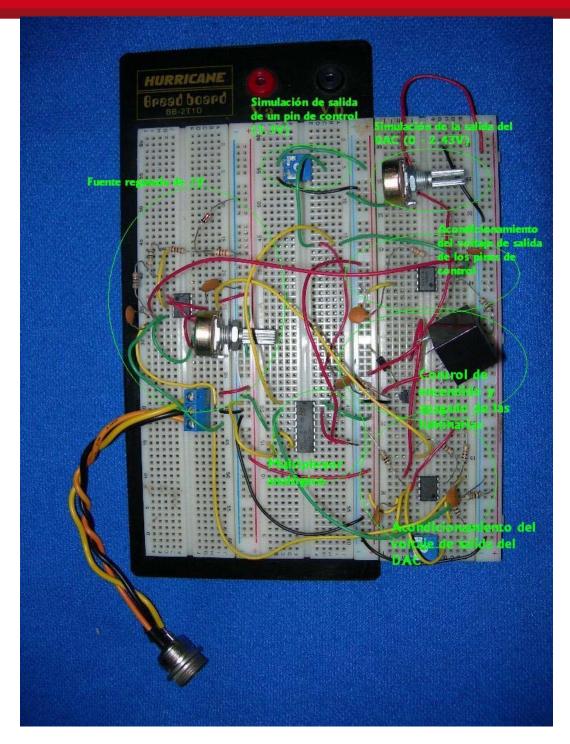

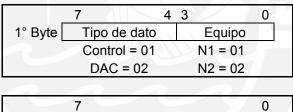

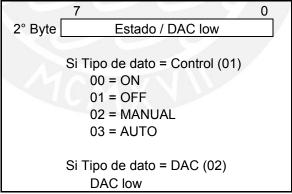

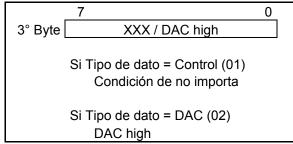

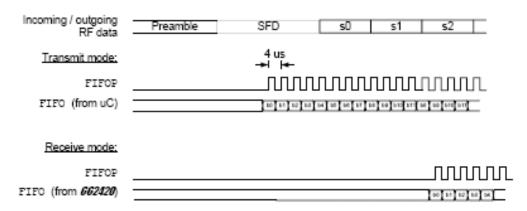

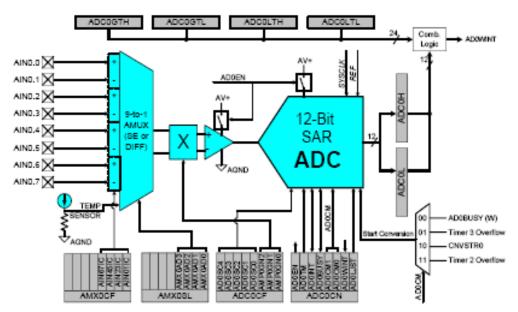

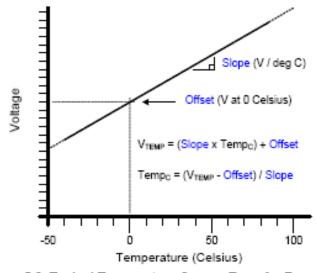

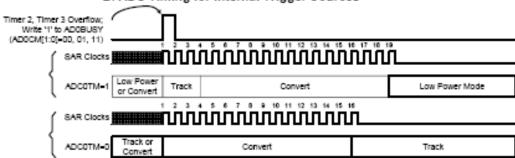

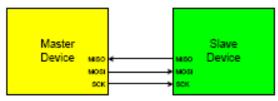

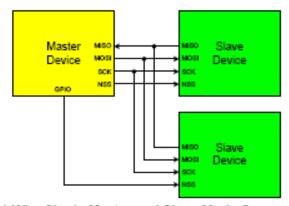

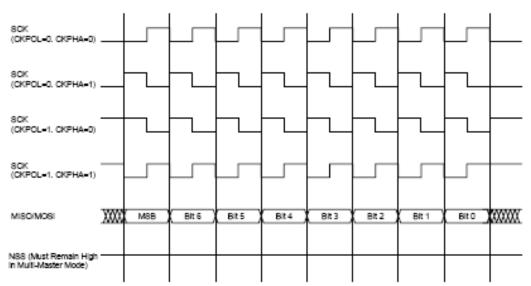

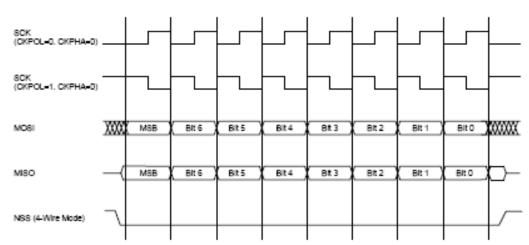

- 2) Sistematizar y automatizar el proceso de regulación de la intensidad luminosa valiéndose del control retroalimentado.